#### 1/O INTERFACE

#### General Theory

As in any computer based system, the 8080 CPU must be able to communicate with devices or structures that exist outside its normal memory array. Devices like keyboards, paper tape, floppy disks, printers, displays and other control structures are used to input information into the 8080 CPU and display or store the results of the computational activity.

Probably the most important and strongest feature of the 8080 Microcomputer System is the flexibility and power of its I/O structure and the components that support it. There are many ways to structure the I/O array so that it will "fit" the total system environment to maximize efficiency and minimize component count.

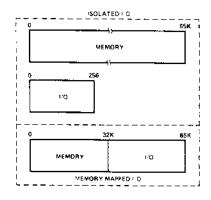

The basic operation of the I/O structure can best be viewed as an array of single byte memory locations that can be Read from or Written into. The 8080 CPU has special instructions devoted to managing such transfers (IN, OUT). These instructions generally isolate memory and I/O arrays so that memory address space is not effected by the I/O structure and the general concept is that of a simple transfer to or from the Accumulator with an addressed "PORT". Another method of I/O architecture is to treat the I/O structure as part of the Memory array. This is generally referred to as "Memory Mapped I/O" and provides the designer with a powerful new "instruction set" devoted to I/O manipulation.

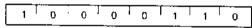

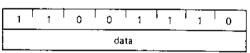

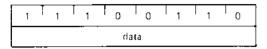

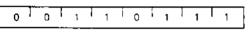

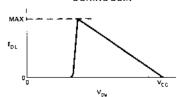

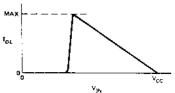

Figure 3-8. Memory/t/O Mapping.

#### Isolated I/O

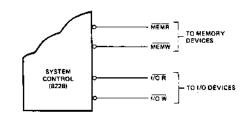

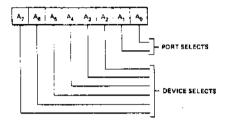

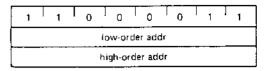

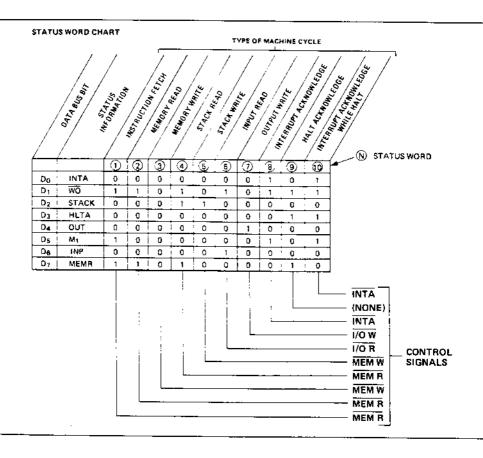

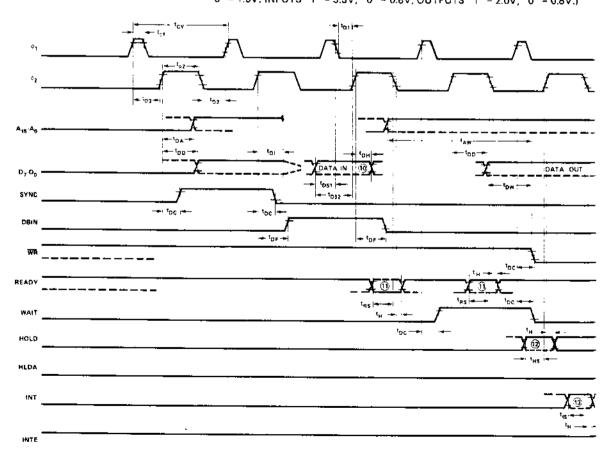

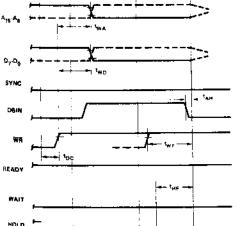

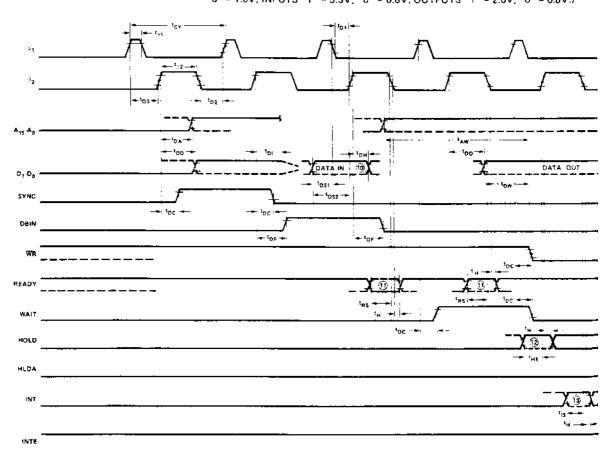

In Figure 3-9 the system control signals, previously detailed in this chapter, are shown. This type of I/O architecture separates the memory address space from the I/O address space and uses a conceptually simple transfer to or from Accumulator technique. Such an architecture is easy to understand because I/O communicates only with the Accumulator using the IN or OUT instructions. Also because of the isolation of memory and I/O, the full address space (65K) is uneffected by I/O addressing.

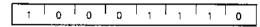

Figure 3-9. Isolated I/O.

#### Memory Mapped I/O

By assigning an area of memory address space as f/O a powerful architecture can be developed that can manipulate I/O using the same instructions that are used to manipulate memory locations. Thus, a "new" instruction set is created that is devoted to I/O handling.

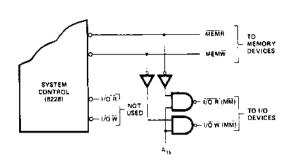

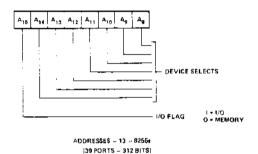

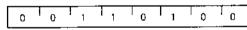

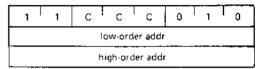

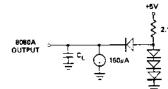

As shown in Figure 3-10, new control signals are generated by gating the  $\overline{\text{MEMR}}$  and  $\overline{\text{MEMW}}$  signals with A<sub>15</sub>, the most significant address bit. The new I/O control signals connect in exactly the same manner as (solated I/O, thus the system bus characteristics are unchanged.

By assigning A<sub>15</sub> as the !/O "flag", a simple method of I/O discipline is maintained:

If A 15 is a "zero" then Memory is active.

If A 15 is a "one" then I/O is active.

Other address bits can also be used for this function. A<sub>15</sub> was chosen because it is the most significant address bit so it is easier to control with software and because it still allows memory addressing of 32K.

I/O devices are still considered addressed "ports" but instead of the Accumulator as the only transfer medium any of the internal registers can be used. All instructions that could be used to operate on memory locations can be used in I/O.

#### Examples:

(Input Port to any Register) MOVr. M MOV M, r (Output any Register to Port) MVLM (Output immediate data to Port) LDA (Input to ACC) (Output from ACC to Port) STA LHLD (16 Bit Input) SHLD (16 Bit Output) ADD M (Add Port to ACC) ("AND" Port with ACC) ANA M

It is easy to see that from the list of possible "new" instructions that this type of I/O architecture could have a drastic effect on increased system throughput, it is conceptually more difficult to understand than Isolated I/O and it does limit memory address space, but Memory Mapped I/O can mean a significant increase in overall speed and at the same time reducing required program memory area.

Figure 3-10, Memory Mapped I/O.

### I/O Addressing

With both systems of I/O structure the addressing of each device can be configured to optimize efficiency and reduce component count. One method, the most common, is to decode the address bus into exclusive "chip selects" that enable the addressed I/O device, similar to generating chipselects in memory arrays.

Another method is called "linear select". In this method, instead of decoding the Address Bus, a singular bit from the bus is assigned as the exclusive enable for a specific I/O device. This method, of course, limits the number of I/O devices that can be addressed but eliminates the need for extra decoders, an important consideration in small system design.

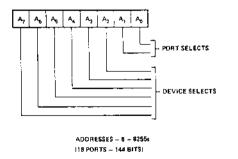

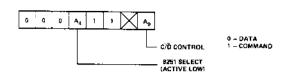

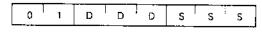

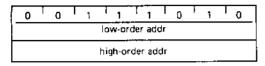

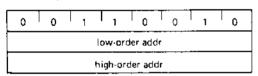

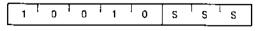

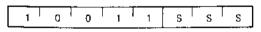

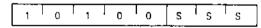

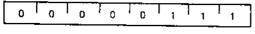

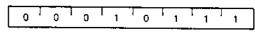

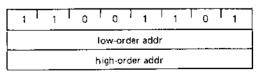

A simple example illustrates the power of such a flexible I/O structure. The first example illustrates the format of the second byte of the IN or OUT instruction using the Isolated I/O technique. The devices used are Intel®8255 Programmable Peripheral Interface units and are linear selected. Each device has three ports and from the format it can be seen that six devices can be addressed without additional decoders.

### **EXAMPLE #1**

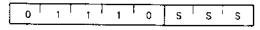

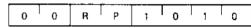

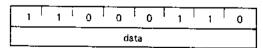

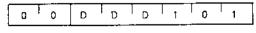

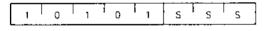

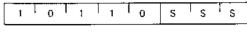

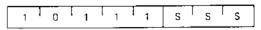

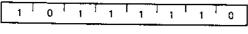

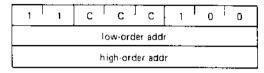

Figure 3-11, Isolated I/O - (Linear Select) (8255)

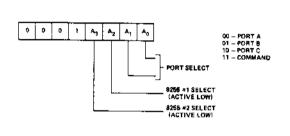

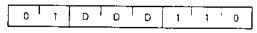

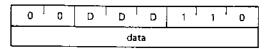

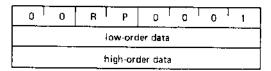

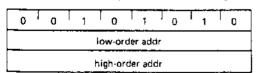

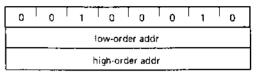

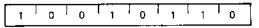

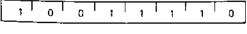

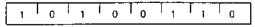

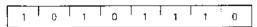

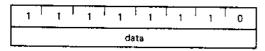

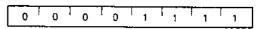

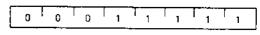

The second example uses Memory Mapped I/O and linear select to show how thirteen devices (8255) can be addressed without the use of extra decoders. The format shown could be the second and third bytes of the LDA or STA instructions or any other instructions used to manipulate I/O using the Memory Mapped technique.

It is easy to see that such a flexible I/O structure, that can be "tailored" to the overall system environment, provides the designer with a powerful tool to optimize efficiency and minimize component count.

#### EXAMPLE #2

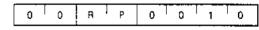

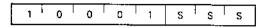

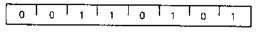

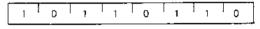

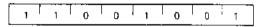

Figure 3-12. Memory Mapped I/O - (Linear Select (8255)

#### I/O Interface Example

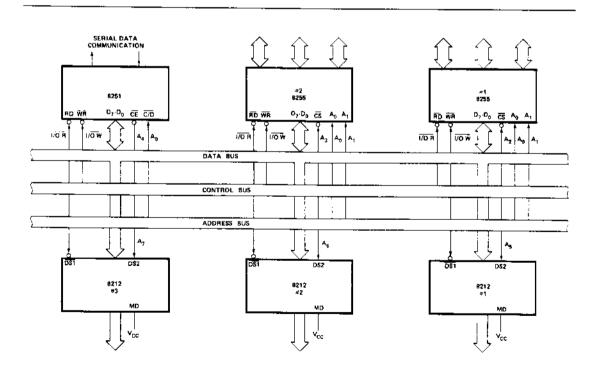

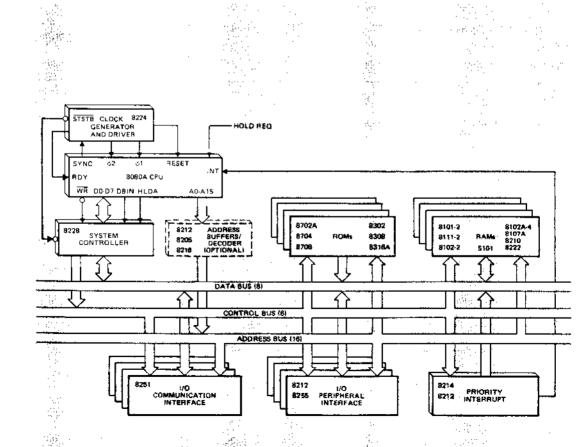

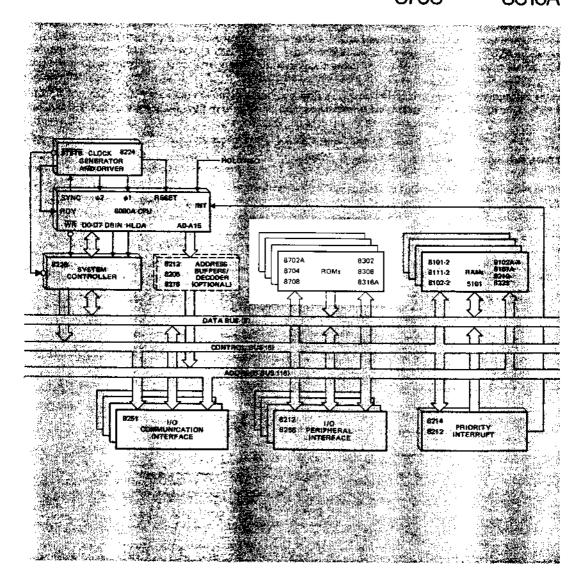

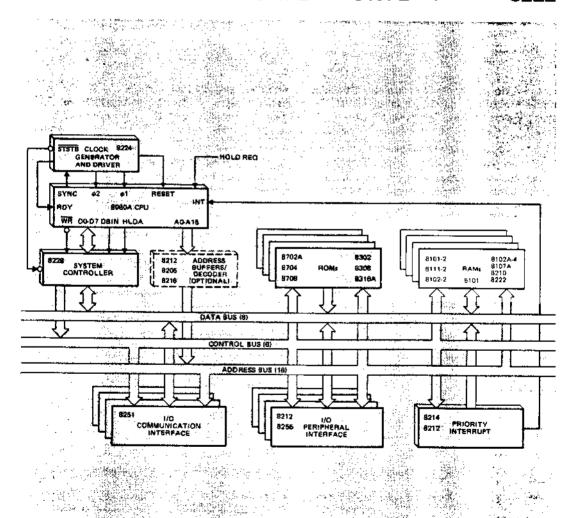

In Figure 3-16 a typical I/O system is shown that uses a variety of devices (8212, 8251 and 8255). It could be used to interface the peripherals around an intelligent CRT terminals; keyboards, display, and communication interface. Another application could be in a process controller to interface sensors, relays, and motor controls. The limitation of the application area for such a circuit is solely that of the designers imagination.

The I/O structure shown interfaces to the 8080 CPU using the bus architecture developed previously in this chapter. Either isolated or Memory Mapped techniques can be used, depending on the system I/O environment.

The 8251 provides a serial data communication interface so that the system can transmit and receive data over communication links such as telephone lines.

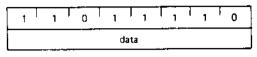

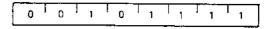

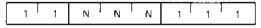

Figure 3-13, 8251 Format,

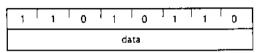

The two (2) 8255s provide twenty four bits each of programmable I/O data and control so that keyboards, sensors, paper tape, etc., can be interfaced to the system.

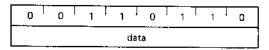

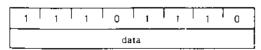

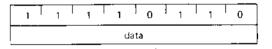

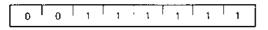

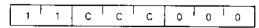

Figure 3-14. 8255 Format.

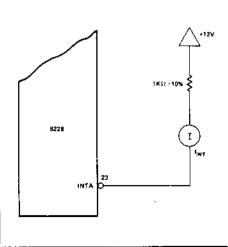

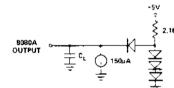

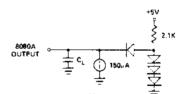

The three 8212s can be used to drive long lines or LED indicators due to their high drive capability. (15mA)

Figure 3-15. 8212 Format.

Addressing the structure is described in the formats illustrated in Figures 3-13, 3-14, 3-15. Linear Select is used so that no decoders are required thus, each device has an exclusive "enable bit".

The example shows how a powerful yet flexible I/O structure can be created using a minimum component count with devices that are all members of the 8080 Microcomputer System.

Figure 3-16. Typical I/O Interface.

A computer, no matter how sophisticated, can only do what it is "told" to do. One "tells" the computer what to do via a series of coded instructions referred to as a Program. The realm of the programmer is referred to as Software, in contrast to the Hardware that comprises the actual computer equipment. A computer's software refers to all of the programs that have been written for that computer.

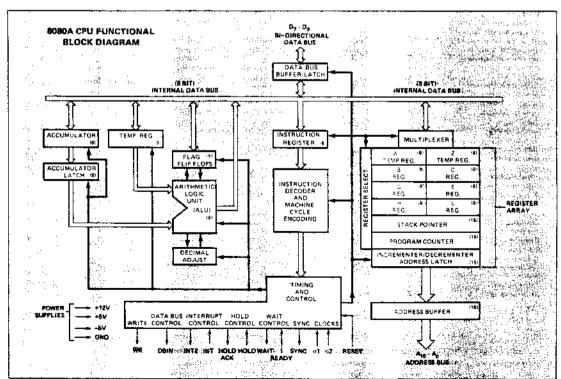

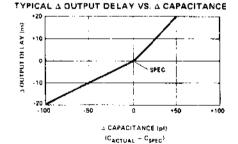

When a computer is designed, the engineers provide the Central Processing Unit (CPU) with the ability to perform a particular set of operations. The CPU is designed such that a specific operation is performed when the CPU control logic decodes a particular instruction. Consequently, the operations that can be performed by a CPU define the computer's Instruction Set.

Each computer instruction allows the programmer to initiate the performance of a specific operation. All computers implement certain arithmetic operations in their instruction set, such as an instruction to add the contents of two registers. Often logical operations (e.g., OR the contents of two registers) and register operate instructions (e.g., increment a register) are included in the instruction set. A computer's instruction set will also have instructions that move data between registers, between a register and memory. and between a register and an I/O device. Most instruction sets also provide Conditional Instructions. A conditional instruction specifies an operation to be performed only if certain conditions have been met; for example, jump to a particular instruction if the result of the last operation was zero. Conditional instructions provide a program with a decision-making capability.

By logically organizing a sequence of instructions into a coherent program, the programmer can "tell" the computer to perform a very specific and useful function.

The computer, however, can only execute programs whose instructions are in a binary coded form (i.e., a series of 1's and 0's), that is called Machine Code, Because it would be extremely cumbersome to program in machine code, programming languages have been developed. There

are programs available which convert the programming language instructions into machine code that can be interpreted by the processor.

One type of programming language is Assembly Language. A unique assembly language mnemonic is assigned to each of the computer's instructions. The programmer can write a program (called the Source Program) using these mnemonics and certain operands; the source program is then converted into machine instructions (called the **Object Code**). Each assembly language instruction is converted into one machine code instruction (1 or more bytes) by an Assembler program. Assembly languages are usually machine dependent (i.e., they are usually able to run on only one type of computer).

#### THE 8080 INSTRUCTION SET

The 8080 instruction set includes five different types of instructions:

- Data Transfer Group—move data between registers or between memory and registers

- Arithmetic Group add, subtract, increment or decrement data in registers or in memory

- Logical Group AND, OR, EXCLUSIVE-OR, compare, rotate or complement data in registers or in memory

- Branch Group conditional and unconditional jump instructions, subroutine call instructions and return instructions

- Stack, I/O and Machine Control Group includes I/O instructions, as well as instructions for maintaining the stack and internal control flags.

#### Instruction and Data Formats:

Memory for the 8080 is organized into 8-bit quantities, called Bytes. Each byte has a unique 16-bit binary address corresponding to its sequential position in memory. The 8080 can directly address up to 65,536 bytes of memory, which may consist of both read-only memory (ROM) elements and random-access memory (RAM) elements (read/ write memory).

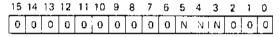

Data in the 8080 is stored in the form of 8-bit binary integers:

When a register or data word contains a binary number, it is necessary to establish the order in which the bits of the number are written. In the Intel 8080, BiT 0 is referred to as the Least Significant Bit (LSB), and BIT 7 (of an 8 bit number) is referred to as the Most Significant Bit (MSB).

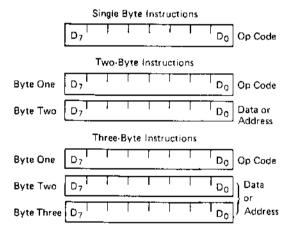

The 8080 program instructions may be one, two or three bytes in length. Multiple byte instructions must be stored in successive memory locations; the address of the first byte is always used as the address of the instructions. The exact instruction format will depend on the particular operation to be executed.

#### Addressing Modes:

Often the data that is to be operated on is stored in memory. When multi-byte numeric data is used, the data, like instructions, is stored in successive memory locations, with the least significant byte first, followed by increasingly significant bytes. The 8080 has four different modes for addressing data stored in memory or in registers:

- Direct Bytes 2 and 3 of the instruction contain the exact memory address of the data item (the low-order bits of the address are in byte 2, the high-order bits in byte 3).

- Register The instruction specifies the register or register-pair in which the data is located,

- Register Indirect The instruction specifies a register-pair which contains the memory

address where the data is located (the high-order bits of the address are in the first register of the pair, the low-order bits in the second).

Immediate — The instruction contains the data itself. This is either an 8-bit quantity or a 16-bit quantity (least significant byte first.) most significant byte second).

Unless directed by an interrupt or branch instruction, the execution of instructions proceeds through consecutively increasing memory locations. A branch instruction can specify the address of the next instruction to be executed in one of two ways:

- Direct The branch instruction contains the address of the next instruction to be executed, (Except for the 'AST' instruction, byte 2 contains the low-order address and byte 3 the high-order address.)

- Register indirect The branch instruction indicates a register-pair which contains the address of the next instruction to be executed. (The high-order bits of the address are in the first register of the pair, the low-order bits in the second.)

The RST instruction is a special one-byte call instruction (usually used during interrupt sequences). RST includes a three-bit field; program control is transferred to the instruction whose address is eight times the contents of this three-bit field.

#### Condition Flags:

There are five condition flags associated with the execution of instructions on the 8080. They are Zero, Sign. Parity, Carry, and Auxiliary Carry, and are each represented by a 1-bit register in the CPU. A flag is "set" by forcing the bit to 1; "reset" by forcing the bit to 0.

Unless indicated otherwise, when an instruction affects a flag, it affects it in the following manner:

Zero: If the result of an instruction has the value 0, this flag is set; otherwise it is reset.

Sign: If the most significant bit of the result of the operation has the value 1, this flag is set: otherwise it is reset.

If the modulo 2 sum of the bits of the re-Parity: sult of the operation is 0, (i.e., if the result has even parity), this flag is set: otherwise it is reset (i.e., if the result has odd parity).

If the instruction resulted in a carry Carry: (from addition), or a borrow (from subtraction or a comparison) out of the highorder bit, this flag is set; otherwise it is

reset.

| iliary Carry: If the instruction caused a carry out |

|-----------------------------------------------------|

| of bit 3 and into bit 4 of the resulting            |

| value, the auxiliary carry is set; otherwise        |

| it is reset. This flag is affected by single        |

| precision additions, subtractions, incre-           |

| ments, decrements, comparisons, and log-            |

| ical operations, but is principally used            |

| with additions and increments preceding             |

| a DAA (Decimal Adjust Accumulator)                  |

| instruction,                                        |

#### Symbols and Abbreviations:

MEANING

Aux

SYMBOLS

The following symbols and abbreviations are used in the subsequent description of the 8080 instructions:

| accumulator Register A  addr 16-bit address quantity  data 8-bit data quantity  data 16 16-bit data quantity  byte 2 The second byte of the instruction  byte 3 The third byte of the instruction  port 8-bit address of an I/O device  r,r1,r2 One of the registers A,B,C,D,E,H,L  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS= source): | SIMBOLS     | MEMAING                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------|

| data 8-bit data quantity  data 16 16-bit data quantity  byte 2 The second byte of the instruction  byte 3 The third byte of the instruction  port 8-bit address of an I/O device  r,r1,r2 One of the registers A,B,C,D,E,H,L  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                | accumulator | Register A                                |

| data 16  16-bit data quantity  byte 2  The second byte of the instruction  byte 3  The third byte of the instruction  port  8-bit address of an I/O device  r,r1,r2  One of the registers A,B,C,D,E,H,L  DDD,SSS  The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                    | addr        | 16-bit address quantity                   |

| byte 2 The second byte of the instruction  byte 3 The third byte of the instruction  port 8-bit address of an I/O device  r,r1,r2 One of the registers A,B,C,D,E,H,L  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                        | data        | 8-bit data quantity                       |

| byte 3 The third byte of the instruction  port 8-bit address of an I/O device  r,r1,r2 One of the registers A,B,C,D,E,H,Ł  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                                                                   | data 16     | 16-bit data quantity                      |

| port 8-bit address of an I/O device  r,r1,r2 One of the registers A,B,C,D,E,H,L  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                                                                                                             | byte 2      | The second byte of the instruction        |

| r,r1,r2 One of the registers A,B,C,D,E,H,L  DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                                                                                                                                                  | byte 3      | The third byte of the instruction         |

| DDD,SSS The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                                                                                                                                                                                              | port        | 8-bit address of an I/O device            |

| ters A,B,C,D,E,H,L (DDD=destination, SSS=                                                                                                                                                                                                                                                                                                                                                  | r,r1,r2     | One of the registers A,B,C,D,E,H,Ł        |

|                                                                                                                                                                                                                                                                                                                                                                                            | DDD,SSS     | ters A,B,C,D,E,H,L (DDD=destination, SSS= |

| DDD or SSS | REGISTER NAME |  |

|------------|---------------|--|

| 111        | Α             |  |

| 000        | В             |  |

| 001        | C             |  |

| 010        | D             |  |

| 011        | E             |  |

| 100        | н             |  |

| 101        | L             |  |

rp One of the register pairs:

RP

B represents the B,C pair with B as the high-order register and C as the low-order register;

D represents the D,E pair with D as the highorder register and E as the low-order register;

H represents the H,L pair with H as the highorder register and L as the low-order register;

SP represents the 16-bit stack pointer register.

The bit pattern designating one of the register pairs B,D,H,SP:

| RP | REGISTER PAIR |

|----|---------------|

| 00 | B-C           |

| 01 | D-E           |

| 10 | H-L           |

| 11 | SP            |

|    |               |

| rl             | The second (low-order) register of a designated register pair.                                                       |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| PC             | 16-bit program counter register (PCH and PCL are used to refer to the high-order and low-order 8 bits respectively). |

| SP             | 16-bit stack pointer register ISPH and SPL are used to refer to the high-order and low-order 8 bits respectively).   |

| r <sub>m</sub> | Bit m of the register r (bits are number 7 through 0 from left to right).                                            |

| Z,S,P,CY,AC    | The condition flags: Zero, Sign, Parity, Carry, and Auxiliary Carry, respectively.                                   |

| ( )            | The contents of the memory location or registers enclosed in the parentheses.                                        |

| -              | "Is transferred to"                                                                                                  |

| ٨              | Logical AND                                                                                                          |

| ^<br>∀<br>∨    | Exclusive OR                                                                                                         |

| ٧              | Inclusive OR                                                                                                         |

| +              | Addition                                                                                                             |

|                | Two's complement subtraction                                                                                         |

| *              | Multiplication                                                                                                       |

| <b>↔</b>       | "Is exchanged with"                                                                                                  |

| _              | The one's complement (e.g., $(\overline{A})$ )                                                                       |

| n              | The restart number 0 through 7                                                                                       |

| NNN            | The binary representation 000 through 111 for restart number 0 through 7 respectively.                               |

The first (high-order) register of a designated

register pair.

### Description Format:

The following pages provide a detailed description of the instruction set of the 8080, Each instruction is described in the following manner:

- The MAC 80 assembler format, consisting of the instruction mnemonic and operand fields, is printed in BOLDFACE on the left side of the first line.

- The name of the instruction is enclosed in parenthesis on the right side of the first line.

- 3. The next line(s) contain a symbolic description of the operation of the instruction.

- This is followed by a narative description of the operation of the instruction.

- The following line(s) contain the binary fields and patterns that comprise the machine instruction.

6. The last four lines contain incidental information about the execution of the instruction. The number of machine cycles and states required to execute the instruction are listed first. If the instruction has two possible execution times, as in a Conditional Jump, both times will be listed, separated by a slash. Next, any significant data addressing modes (see Page 4-2) are listed. The last line lists any of the five Flags that are affected by the execution of the instruction.

## Data Transfer Group:

This group of instructions transfers data to and from registers and memory. Condition flags are not affected by any instruction in this group.

# MOV r1, r2 (Move Register)

(r1) - (r2)

The content of register r2 is moved to register r1.

Cycles: 1

States: 5

Addressing: register

Flags: none

# MOV r, M (Move from memory)

(r) --- ((H) (L))

The content of the memory location, whose address is in registers H and L, is moved to register r,

Cycles: 2 States: 7

Addressing: reg. indirect

Flags: none

# MOV M, r (Move to memory)

$((H)(L)) \leftarrow (c)$

The content of register r is moved to the memory location whose address is in registers H and L.

Cycles: 2 States: 7

Addressing: reg, indirect

Flags: none

# MVI r, data (Move Immediate)

(r) - (byte 2)

The content of byte 2 of the instruction is moved to register r.

Cycles: 2 States: 7

Addressing: immediate

Flags: none

# MVI M, data (Move to memory immediate)

((H) (L)) - (byte 2)

The content of byte 2 of the instruction is moved to the memory location whose address is in registers H and L.

Cycles: 3 States: 10

Addressing: immed./reg. indirect

Flags: none

#### LXI rp, data 16 (Load register pair immediate)

(rh) ← (byte 3), (rl) ← (byte 2)

Byte 3 of the instruction is moved into the high-order register (rh) of the register pair rp. Byte 2 of the instruction is moved into the low-order register (rl) of the register pair rp.

Cycles: 3 States: 10

Addressing: immediate

Flags: none

LDA addr (Load Accumulator direct)

(A) - ((byte 3)(byte 2))

The content of the memory location, whose address is specified in byte 2 and byte 3 of the instruction, is moved to register A.

Cycles: 4 States: 1

States: 13

Addressing: direct

Flags: none

#### STA addr (Store Accumulator direct)

((byte 3)(byte 2)) - (A)

The content of the accumulator is moved to the memory location whose address is specified in byte 2 and byte 3 of the instruction.

Cycles: 4

States: 13 Addressing: direct

Flags: none

LHLD addr (Load H and £ direct)

(L) ← ((byte 3)(byte 2))

(H) - ((byte 3)(byte 2) + 1)

The content of the memory location, whose address is specified in byte 2 and byte 3 of the instruction, is moved to register L. The content of the memory location at the succeeding address is moved to register H.

Cycles: 5

States: 16

Addressing: direct

Flags: none

SHLD addr (Store H and L direct)

((byte 3)(byte 2)) → (L)

((byte 3)(byte 2) + 1) - (H)

The content of register L is moved to the memory location whose address is specified in byte 2 and byte 3. The content of register H is moved to the succeed-

ing memory location.

Cycles: 5

States: 16 Addressing: direct

Flags: none

#### LDAX rp (Load accumulator indirect)

(A) ← ((rp))

The content of the memory location, whose address is in the register pair rp, is moved to register A. Note: only register pairs rp=B (registers B and C) or rp=D (registers D and E) may be specified.

Cycles: 2

States: 7

Addressing: reg, indirect

Flags: none

STAX rp (Store accumulator indirect)

$\{(rp)\} \leftarrow \{A\}$

The content of register A is moved to the memory location whose address is in the register pair rp, Note: only register pairs rp=8 (registers B and C) or rp=D (registers D and E) may be specified.

Cycles: 2

States: 7

Addressing: reg, indirect

Flags: none

XCHG (Exchange H and L with D and E)

$(H) \leftarrow (D)$

(L) ++ (E)

The contents of registers H and L are exchanged with the contents of registers D and E.

Cycles: 1

States: 4

Addressing: register

Flags: none

### Arithmetic Group:

This group of instructions performs arithmetic operations on data in registers and memory.

Unless indicated otherwise, all instructions in this group affect the Zero, Sign, Parity, Carry, and Auxiliary Carry flags according to the standard rules.

All subtraction operations are performed via two's complement arithmetic and set the carry flag to one to indicate a borrow and clear it to indicate no borrow.

# ADD r (Add Register)

$(A) \leftarrow (A) + (r)$

The content of register r is added to the content of the accumulator. The result is placed in the accumulator.

Cycles: States:

Addressing: register

Flags: Z,S,P,CY,AC

4

# ADD M (Add memory)

$(A) \leftarrow (A) + ((H)(L))$

The content of the memory location whose address is contained in the H and L registers is added to the content of the accumulator. The result is placed in the accumulator.

Cycles: 2 States: 7

Addressing: reg. indirect

Flags: Z,S,P,CY,AC

# ADI data (Add immediate)

(A) - (A) + (byte 2)

The content of the second byte of the instruction is added to the content of the accumulator. The result is placed in the accumulator.

Cycles: 2

States: 7

Addressing: immediate

Flags: Z,S,P,CY,AC

# ADC r (Add Register with carry)

$$\{A\} \leftarrow \{A\} + \{r\} + \{CY\}$$

The content of register r and the content of the carry bit are added to the content of the accumulator. The result is placed in the accumulator.

Cycles: 1

States: 4

Addressing: register Flags: Z.S.P.CY.AC

# ADC M (Add memory with carry)

The content of the memory location whose address is contained in the H and L registers and the content of the CY flag are added to the accumulator. The result is placed in the accumulator.

Cycles: 2

States: 7

Addressing: reg. indirect Flags: Z,S,P,CY,AC

# ACI data (Add immediate with carry)

The content of the second byte of the instruction and the content of the CY flag are added to the contents of the accumulator. The result is placed in the accumulator.

Cycles: 2 States: 7

Addressing: immediate

Flags: Z,S,P,CY,AC

# SUB r (Subtract Register)

The content of register r is subtracted from the content of the accumulator. The result is placed in the accumulator.

Cycles: 1 States: 4

Addressing: register

Flags: Z,S,P,CY,AC

#### SUB M (Subtract memory) $(A) \leftarrow (A) - ((H)(L))$

The content of the memory location whose address is contained in the H and L registers is subtracted from the content of the accumulator. The result is placed in the accumulator.

Cycles: 2 States:

Addressing: reg. indirect

Z.S.P.CY.AC Flags:

#### SUI data (Subtract immediate)

The content of the second byte of the instruction is subtracted from the content of the accumulator. The result is placed in the accumulator.

Cycles: 2 States: 7

Addressing: immediate Z.S.P.CY.AC Flags:

#### SBB r (Subtract Register with borrow)

(A)

$$\leftarrow$$

(A)  $-$  (r)  $+$  (CY)

The content of register r and the content of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator.

Cycles: 1

States: Addressing: register

Flags: Z.S.P.CY.AC

#### SBB M (Subtract memory with borrow)

$$(A) \longrightarrow (A) - ((H)(L)) - (CY)$$

The content of the memory location whose address is contained in the H and L registers and the content of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator

Cycles: 2 States: 7

Addressing: reg. indirect Flags: Z.S.P.CY.AC

#### SBI data (Subtract immediate with borrow)

(A)

$$\leftarrow$$

(A) - (byte 2) - (CY)

The contents of the second byte of the instruction and the contents of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator.

Cycles: 2 States: 7

Addressing: immediate Flags: Z.S.P.CY.AC

#### INR r (Increment Register)

$$(r) - (r) + 1$$

The content of register r is incremented by one. Note: All condition flags except CY are affected.

States: 5 Addressing: register Flags: Z,S,P,AC

#### INR M (Increment memory)

$$((H)(L)) \leftarrow ((H)(L)) + 1$$

The content of the memory location whose address is contained in the H and L registers is incremented by one. Note: All condition flags except CY are affected.

Cycles: 3 States: 10

Addressing: rea, indirect Flags: Z,S,P,AC

#### DCR r (Decrement Register)

(r)

$$\leftarrow$$

(r)  $-1$

The content of register r is decremented by one. Note: All condition flags except CY are affected.

Cycles: 1 5 States:

Addressing: register Flags: Z,S,P,AC

(Decrement memory) DCR M

((H) (L) ← ((H) (L)) = 1

The content of the memory location whose address is contained in the H and L registers is decremented by one, Note: All condition flags except CY are affected.

Cycles:

3 10

States:

Addressing: reg, indirect

> Flags: Z.S.P.AC

INX rp

(Increment register pair)

(rh) (rl) - (rh) (rl) + 1

The content of the register pair rp is incremented by one. Note: No condition flags are affected,

States:

Addressing: register Flags: none

DCX rp (Decrement register pair)

(rh) (rt)  $\leftarrow$  (rh) (rt) - 1

The content of the register pair rp is decremented by one, Note: No condition flags are affected.

1 States:

Addressing: register

> Flags: none

DAD rp (Add register pair to H and L)

(H) (L) ← (H) (L) + (rh) (rl)

The content of the register pair rp is added to the content of the register pair H and L. The result is placed in the register pair H and L. Note: Only the CY flag is affected. It is set if there is a carry out of the double precision add; otherwise it is reset.

Cycles:

States: 10

Addressing: register

Flags: CY DAA (Decimal Adjust Accumulator)

The eight-bit number in the accumulator is adjusted to form two four-bit Binary-Coded-Decimal digits by the following process:

- If the value of the least significant 4 bits of the accumulator is greater than 9 or if the AC flag is set, 6 is added to the accumulator.

- 2. If the value of the most significant 4 bits of the accumulator is now greater than 9, or if the CY flag is set, 6 is added to the most significant 4 bits of the accumulator.

NOTE: All flags are affected.

Cycles: 1

States: 4

Flags: Z.S.P.CY.AC

# Logical Group:

This group of instructions performs logical (Boolean) operations on data in registers and memory and on condition flags.

Unless indicated otherwise, all instructions in this group affect the Zero, Sign, Parity, Auxiliary Carry, and Carry flags according to the standard rules,

ANA r (AND Register)

(A) ← (A) ∧ (r)

The content of register r is logically anded with the content of the accumulator. The result is placed in the accumulator. The CY flag is cleared.

Cycles: 1

States: 4

Addressing: register

> Flags: Z.S.P.CY.AC

ANA M (AND memory)

(A) ← (A) ∧ ((H) (L))

The contents of the memory location whose address is contained in the H and L registers is logically anded with the content of the accumulator. The result is placed in the accumulator. The CY flag is cleared.

Cycles: 2

States:

Addressing: rea, indirect

> Flags: Z,S,P,CY,AC

ANI data (AND immediate)

(A) ← (A) ∧ (byte 2)

The content of the second byte of the instruction is logically anded with the contents of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 2 States: 7

Addressing: immediate Flags: Z.S.P.CY.AC

## XRA r (Exclusive OR Register)

(A) ← (A) ∀ (r)

The content of register r is exclusive-or'd with the content of the accumulator. The result is placed to the accumulator. The CY and AC flags are cleared.

Cycles: 1

States: 4

Addressing: register

Flags: Z.S.P.CY.AC

# XRA M (Exclusive OR Memory)

(A)  $\longleftarrow$  (A)  $\forall$   $\{(H)(L)\}$

The content of the memory location whose address is contained in the H and L registers is exclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 2 States: 7

Addressing: reg, indirect

Flags: Z,S,P,CY,AC

# XRI data (Exclusive OR immediate)

(A) ← (A) ∀ (byte 2)

The content of the second byte of the instruction is exclusive-QR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 2 States: 7

Addressing: immediate Flags: Z,S,P,CY,AC

#### ORAr (OR Register)

(A) - (A) V (r)

The content of register r is inclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 1

States: 4

Addressing: register

Flags: Z,S,P,CY,AC

#### ORAM (OR memory)

(A) ← (A) V ((H) (L))

The content of the memory location whose address is contained in the H and L registers is inclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 2 States: 7

Addressing: reg. indirect Flags: Z,S,P,CY,AC

#### ORI data (OR Immediate)

(A) ← (A) V (byte 2)

The content of the second byte of the instruction is inclusive OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

Cycles: 2 States: 7

Addressing: immediate Flags: Z.S.P.CY.AC

#### CMP r (Compare Register)

(A) = (c)

The content of register r is subtracted from the accumulator. The accumulator remains unchanged. The condition flags are set as a result of the subtraction. The Z flag is set to 1 if (A) = (r). The CY flag is set to 1 if (A) < (r).

Cycles: 1

States: 4

Addressing: register

Flags: Z,S,P,CY,AC

#### CMP M (Compare memory)

(A) = ((H) (L))

The content of the memory location whose address is contained in the H and L registers is subtracted from the accumulator. The accumulator remains unchanged. The condition flags are set as a result of the subtraction. The Z flag is set to 1 if (A) = ((H) (L)). The CY flag is set to 1 if (A) < ((H) (L)).

Cycles: 2 States:

Addressing: reg. indirect Flags: Z.S.P.CY.AC

#### CPI data (Compare immediate)

(A) — (byte 2)

The content of the second byte of the instruction is subtracted from the accumulator. The condition flags are set by the result of the subtraction. The Z flag is set to 1 if (A) = (byte 2). The CY flag is set to 1 if  $(A) \le (byte 2)$ .

2 Cycles: States:

Addressing: immediate Flags: Z,S,P,CY,AC

#### RLC (Rotate left)

$(A_{n+1}) - (A_n) : (A_0) - (A_7)$

(CY) - (A7)

The content of the accumulator is rotated left one position. The low order bit and the CY flag are both set to the value shifted out of the high order bit position. Only the CY flag is affected.

Cycles: States: Flags: CY

#### RRC (Rotate right)

$(A_n) \leftarrow (A_{n-1}) ; (A_7) \leftarrow (A_0)$ (CY) - (A<sub>0</sub>)

The content of the accumulator is rotated right one position. The high order bit and the CY flag are both set to the value shifted out of the low order bit position, Only the CY flag is affected.

Cycles: States: Flags: CY

#### RAL (Rotate left through carry)

$$(A_{n+1}) \leftarrow (A_n) : (CY) \leftarrow (A_7)$$

$(A_0) \leftarrow (CY)$

The content of the accumulator is rotated left one position through the CY flag. The low order bit is set equal to the CY flag and the CY flag is set to the value shifted out of the high order bit. Only the CY flag is affected.

Cycles: States: Flags: CY

#### RAR (Rotate right through carry)

$$(A_n) \leftarrow (A_{n+1})$$

;  $(CY) \leftarrow (A_0)$

$(A_7) \leftarrow (CY)$

The content of the accumulator is rotated right one position through the CY flag. The high order bit is set to the CY flag and the CY flag is set to the value shifted out of the low order bit. Only the CY flag is affected.

Cycles: States: Flags: CY

#### CMA (Complement accumulator)

(A) --- (A)

The contents of the accumulator are complemented (zero bits become 1, one bits become 0). No flags are affected.

Cycles: 1 States: Flags: none CMC

(Complement carry)

$(CY) \leftarrow (\overline{CY})$

The CY flag is complemented. No other flags are affected.

Cycles: 1 States: 4 Flags: CY

STC (Set carry)

(CY) - 1

The CY flag is set to 1. No other flags are affected.

Cycles: 1 States: 4 Flags: CY

### Branch Group:

This group of instructions after normal sequential program flow.

Condition flags are not affected by any instruction in this group.

The two types of branch instructions are unconditional and conditional. Unconditional transfers simply perform the specified operation on register PC (the program counter). Conditional transfers examine the status of one of the four processor flags to determine if the specified branch is to be executed. The conditions that may be specified are as follows:

| CON | DITION                                  | CCC |

|-----|-----------------------------------------|-----|

| ΝZ  | — not zero (Z = 0)                      | 000 |

| Z   | <ul><li>zero (Z = 1)</li></ul>          | 001 |

| NC  | — no carry (CY = 0)                     | 010 |

| С   | — carry (CY = 1)                        | 011 |

| PO  | <ul><li>parity odd (P = 0)</li></ul>    | 100 |

| PΕ  | <ul><li>— parity even (P ≈ 1)</li></ul> | 101 |

| P   | — plus (5 = 0)                          | 110 |

| M   | - minus (S = 1)                         | 111 |

JMP addr (Jump)

(PC) ← (byte 3) (byte 2)

Control is transferred to the instruction whose ad-

dress is specified in byte 3 and byte 2 of the current instruction.

Cycles: 3 States: 10

Addressing: immediate

Jeondition addr (Conditional jump)

If (CCC),

(PC) ← (byte 3) (byte 2)

If the specified condition is true, control is transferred to the instruction whose address is specified in byte 3 and byte 2 of the current instruction; otherwise, control continues sequentially.

Cycles: 3 States: 10

Addressing: immediate Flags: none

CALL addr (Call)

((SP) = 1) → (PCH)

((SP) = 2) ← (PCL)

(SP) ← (SP) = 2

(PC) ← (byte 3) (byte 2)

The high-order eight bits of the next instruction address are moved to the memory location whose address is one less than the content of register SP. The low-order eight bits of the next instruction address are moved to the memory location whose address is two less than the content of register SP. The content of register SP is decremented by 2. Control is transferred to the instruction whose address is specified in byte 3 and byte 2 of the current instruction.

Cycles: 5 States: 17

Addressing: immediate/reg, indirect

Flags: none

# Condition addr (Condition call) If (CCC), ((SP) = 1) ← (PCH)

((SP) = 1) ← (PCH) ((SP) = 2) ← (PCL)

(SP) ← (SP) - 2

(PC) → (byte 3) (byte 2)

If the specified condition is true, the actions specified in the CALL instruction (see above) are performed; otherwise, control continues sequentially.

Cycles: 3/5 States: 11/17

Addressing: immediate/reg. indirect

Flags: none

####

The content of the memory location whose address is specified in register SP is moved to the low-order eight bits of register PC. The content of the memory location whose address is one more than the content of register SP is moved to the high-order eight bits of register PC. The content of register SP is incremented by 2.

Cycles: 3 States: 10

Addressing: reg, indirect

Flags: none

Rcondition (Conditional return)

If (CCC)

(PCL) - ((SP))

(PCH) → ((SP) + 1) (SP) → (SP) + 2

If the specified condition is true, the actions specified in the RET instruction (see above) are performed; otherwise, control continues sequentially.

Cycles: 1/3 States: 5/11

Addressing: reg. indirect

Flags: none

RST n (Restart) ((SP) = 1) ---- (PCH) ((SP) = 2) ---- (PCL) (SP) ---- (SP) = 2 (PC) ---- 8 \* (NNN)

The high-order eight bits of the next instruction address are moved to the memory location whose address is one less than the content of register SP. The low-order eight bits of the next instruction address are moved to the memory location whose address is two less than the content of register SP. The content of register SP is decremented by two. Control is transferred to the instruction whose address is eight times the content of NNN.

Cycles: 3 States: 11

Addressing: reg. indirect

Flags: none

Program Counter After Restart

PCHL (Jump H and L indirect — move H and L to PC) (PCH) ← (H)

(PCL) + (L)

The content of register H is moved to the high-order eight bits of register PC. The content of register L is moved to the low-order eight bits of register PC.

Cycles: 1

States: 5

Addressing: register

Flags: none

## Stack, I/O, and Machine Control Group:

This group of instructions performs I/O, manipulates the Stack, and alters internal control flags.

Unless otherwise specified, condition flags are not affected by any instructions in this group.

| D <sub>7</sub> | 06 | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D, | $D_{\mathbf{G}}$ |

|----------------|----|----------------|----------------|----------------|----------------|----|------------------|

| s              | z  | 0              | AC             | 0              | Р              | 1  | ÇY               |

FLAG WORD

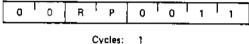

The content of the high-order register of register pair rp is moved to the memory location whose address is one less than the content of register SP. The content of the low-order register of register pair rp is moved to the memory location whose address is two less than the content of register SP. The content of register SP is decremented by 2. Note: Register pair rp = SP may not be specified.

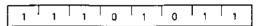

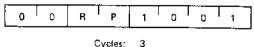

| 1 | 1 | R | P   | 0 | 1 | 1 0 | 1 |

|---|---|---|-----|---|---|-----|---|

|   |   |   | : 3 |   |   |     |   |

Cycles: 3 States: 11

Addressing: reg. indirect Flags: none

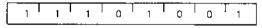

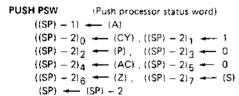

The content of register A is moved to the memory location whose address is one less than register SP. The contents of the condition flags are assembled into a processor status word and the word is moved to the memory location whose address is two less than the content of register SP. The content of register SP is decremented by two.

|  | 1 1 | 1 1 | 0 1 | 0 | 1 |

|--|-----|-----|-----|---|---|

|--|-----|-----|-----|---|---|

Cycles: 3 States: 11

Addressing: reg. indirect

| POP rp | (Pop)      |

|--------|------------|

| (rl)   | ((SP))     |

| (rh)   | {(SP) + 1} |

| (SP)   | (SP) + 2   |

The content of the memory location, whose address is specified by the content of register SP, is moved to the low-order register of register pair rp. The content of the memory location, whose address is one more than the content of register SP, is moved to the high-order register of register pair rp. The content of register SP is incremented by 2. Note: Register pair rp = SP may not be specified.

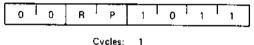

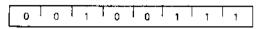

| 1 | 1 | R | P | 0 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|---|

|   | • | • |   | • |   |   |   |

Cycles: 3 States: 10

Addressing: reg. indirect

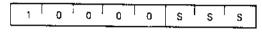

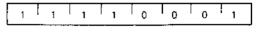

POP PSW (Pop processor status word)

(CY) ← ((SP))<sub>0</sub>

(P) ← ((SP))<sub>2</sub>

(AC) ← ((SP))<sub>4</sub>

(Z) ← ((SP))<sub>6</sub>

(S) ← ((SP))<sub>7</sub>

(A) ← ((SP) + 1)

(SP) ← (SP) + 2

The content of the memory location whose address is specified by the content of register SP is used to restore the condition flags. The content of the memory location whose address is one more than the content of register SP is moved to register A. The content of register SP is incremented by 2.

Cycles: 3 States: 10

Addressing: reg. indirect Flags: Z,S,P,CY,AC XTHL

(Exchange stack top with H and L)

(L) --- ((SP))

(H) -- ((SP) + 1)

The content of the L register is exchanged with the content of the memory location whose address is specified by the content of register SP. The content of the H register is exchanged with the content of the memory location whose address is one more than the content of register SP.

Cycles: 5

States: 18

Addressing: reg. indirect

Flags: none

SPHL

(Move HL to SP)

(SP) + (H) (L)

The contents of registers H and L (16 bits) are moved to register SP.

Cycles: 1

States: 5

States.

Addressing: register

Flags: none

IN port (Input)

(A) → {data}.

The data placed on the eight bit bi-directional data bus by the specified port is moved to register A.

3

Cycles:

States: 10

Addressing: direct

Flags: none

OUT port

(Output)

(data) ← (A)

The content of register A is placed on the eight bit bi-directional data bus for transmission to the specified port.

Cycles:

3

States:

es: 10 na: direct

Addressing: dir

Flags: none

#### Ei (Enable interrupts)

The interrupt system is enabled following the execution of the next instruction.

Cycles: 1

States: 4

Flags: none

#### DI (Disable interrupts)

The interrupt system is disabled immediately following the execution of the DI instruction.

Cycles: 1

States: 4

Flags: none

# HLT (Halt)

The processor is stopped. The registers and flags are unaffected.

Cycles: 1

States: 7

Flags: none

#### NOP (No op)

No operation is performed. The registers and flags are unaffected.

Cycles: 1

States: 4

Flags: none

#### INSTRUCTION SET

#### Summary of Processor Instructions

|                  |                                       |                |     | Inst | ructi | an C | o de | ı   |                  | Clack .   |            |                                       |     |     | Inst | t u Çtir | on C | ode . |     |       | Clock 2 |

|------------------|---------------------------------------|----------------|-----|------|-------|------|------|-----|------------------|-----------|------------|---------------------------------------|-----|-----|------|----------|------|-------|-----|-------|---------|

| Meamonic         | Description                           | D <sub>7</sub> | 06  | 05   | Dd    | D;   | 02   | D   | , D <sub>U</sub> | Cycles    | Mnemonic   | Description                           | 0,  | 06  | 05   | 04       | 03   | 0,    | D   | , Deg | €ycles  |

| MDV              | Move register to legister             | g              | 1   | 0    | D     | ٥    | s    | s   | s                | 5         | AZ         | Return on Zerg                        | 1   | 1   | 9    |          | ,    | D     | ç   | j -   | 5 11    |

| MDV M            | Move register to memory               | č              | i   | ĭ    | 1     | D    | Š    | Š   | s                | ī         | RNZ        | Réturn an na zera                     | i.  | i.  | é    | -        | å    | Ď     | ć   | 2     | 5 11    |

| MOV: M           | ♥ave memary to register               | 2              | 1   | a    | D     | D    | ī    | 1   | Ď                | ī         | <b>н</b> Р | Return on positive                    | i.  | 1   | í    | - 7      | 1    | Đ     | ò   | 2     | 5 11    |

| H <sub>E</sub> T | Hair                                  | Ü              | i.  | 1    | 1     | Ö    | 1    | Ť   | ō                | 1         | RM         | Peturn on minus                       | i   | i   | - ;  |          | ·    | Ď     | ě   |       | 5 ! 1   |

| WVII             | Move immediate register               | 3              | q   | 0    | 0     | Ď    | 4    | !   | ō.               | 7         | RPE        | Return on panny even                  | i.  | i.  |      | -        |      | Ď     | Ē   | á     | 5.11    |

| WVI M            | Move immediate memory                 | 2              | 0   | 1    | 1     | ŋ    | 1    | ł   | 3                | I D       | HPD        | Return on parity odd                  | i.  | 1   |      | -        | 6    | Ō     | :   | 5     | 5 11    |

| WRI              | : crement régislés                    | 0              | c   | t]   | П     | D    | 5    | D   | G                |           | RST        | Restari                               | - 1 | 1   | A    | 5        | Ą    | 1     |     | :     | 11      |

| CCAr             | Decrement register                    | 2              | 0   | .1   | מ     | Ü    | 1    | 0   | 1                | 5         | 18         | traut                                 | - 1 | 1   | 9    |          |      | U     |     |       | 10      |

| YR M             | Intriment memory                      | U              | 0   | 1    | 1     | 0    | i    | 0   | 2                | :0        | TC 0       | 3.4501                                | - 1 | 1   | - :  | :        | 9    | D     |     |       | 10      |

| JUR M            | Decrement memory                      | U              | Ď   | -1   | 1     | Π    | 1    | D   | 1                | : 0       | ( ×1 8     | Load immediate register               | :   | ۵   | ē    | 2        | 9    | ٥     | 1   | -     | 10      |

| 40D7             | Acd register to A                     |                | D   | Ģ.   | 0     | Û    | 3    | 5   | 5                | 4         |            | Pair 8 8 C                            |     |     |      |          |      |       |     |       |         |

| ADDI             | And register to A with carry          | 1              | 9   | G    | ū     | 1    | S    | 2   | S                |           | .x o       | Load immediate register               | - 0 | g   | G    | ,        | 2    | 6     | (   | 1     | :0      |

| SUB              | Subtract register from A              | 1              | D   | ö    | 1     | 0    | 5    | 5   | 5                | 1         |            | Pair 0 & E                            |     |     |      |          |      |       |     |       |         |

| 1882             | Submediregister from A<br>with borrow | 1              | 0   | 3    | 1     | 1    | S    | S   | S                | +         | ľ XI H     | Load immediate register<br>Pair H & ( | 2   | C   | 1    | :        | )    | D     | 2   | -     | 10      |

| ANA r            | And register with A                   | 1              | 0   | -1   | 0     | û    | 9    | S   | S                | 4         | LXI SP     | Licad immediate stack pointer         | 0   | 0   | 1    |          | ŋ    | 9     | ٥   | 7     | 10      |

| ARA 1            | Exclusive Or register with A          | 1              | D   | 1    | 0     | -1   | 5    | 5   | 3                | 4         | PUSH B     | Push register Pair 8 8 C an           | 1   | ī   | ò    | -        | 0    | 1     | ç   | 1     | 11      |

| O F.A.r          | Or register with A                    | 1              | 0   | -1   | 1     | ũ    | S    | S   | S                | :         | *          | srack                                 |     |     | -    | -        | -    |       | -   |       |         |

| ÇMP r            | Compare register with A               | 1              |     | -1   | 1     | 1    | \$   | 5   | 5                | 4         | PUSH 0     | Prish register Pair O & £ on          | :   | 1   | 0    |          | 0    | 1     | 5   | 1     | 11      |

| ADO M            | Add memory to A                       | 1              | 0   | e    | 0     | 0    | 1    | 1   | 0                | - (       |            | stack                                 |     |     | -    |          |      | -     | -   |       |         |

| ADC M            | Add memory to A with carry            | 1              | ù   | 6    | 0     | 1    | 1    | 1   | D                | I .       | PUSH R     | Posh register Pan H & L on            | - 1 | 1   | 1    | 2        | 0    | 1     | 0   | 1     | 11      |

| SUB M            | Subtract memory from A                | 1              | 0   | 9    | - 1   | 0    | 7    | 1   | 9                | 7         |            | stack                                 |     |     |      |          |      |       |     |       |         |

| 588 <b>M</b>     | Subtract memory from A with buttons   | - 1            | 0   | Ð    | ı     | 1    | 1    | 1   | n                | ;         | PUSH PSW   | Push A and Flags<br>on stack          | 1   | 1   | 1    | 1        | 0    | 1     | 0   | 1     | 11      |

| AMAM             | And memory with A                     | - 1            | ŋ   | 1    | 0     | a    | 1    | 1   | a                | 1         | POP8       | Progregister pair B & C off           |     | 1   | 9    | 5        | ŋ    | D     | ŋ   | •     | 10      |

| XPA W            | Exclusive Or memory with A            | - 1            | 0   | 1    | 0     | 1    | 1    | 1   | U                | 1         |            | tack                                  |     |     | ,    | •        | ,    |       |     |       |         |

| BRAM             | Or memory with 4                      | - 1            | ū   | 1    | - 1   | 4    | 1    | 1   | a                | 1         | POP 0      | Pog register gan D.R.E. alf           | - 1 | 1   | 7    |          | a    | 0     | Ò   | 1     | 16      |

| C MP M           | Compare memory with A                 | - 1            | 0   | 1    | - 1   | -1   | -1   | 1   | 0                | 1         |            | Mack                                  |     |     |      |          | -    | -     | -   |       |         |

| ADI              | And immediate to A                    | - 1            | 1   | 0    | 0     | -    | -1   | -1  | Π                | 1         | POP H      | Pop register som H & s. n.l.          |     | 1   |      | 1        | a    | 0     | 9   | 1     | 10      |

| ACI              | Allow A or aredamin bbA               |                | 1   | n.   | Ð     | •    | - 1  | -1  | 0                | 1         |            | Mack                                  |     |     |      |          |      |       |     |       | -       |

|                  | GP5                                   |                |     |      |       |      |      |     |                  |           | POP PSW    | Pop A and Flags                       | 1   | 1   | :    |          | 3    | 0     | 0   | :     | 10      |

| ZUI              | Submack invined are from A            | - 1            | -1  | η    | - 1   | Π    | 1    | - 1 |                  | 7         |            | elf stack                             |     |     |      |          |      |       |     |       |         |

| 581              | Subtract immediate from A             |                | •   | 9    | 1     | - 1  |      | 1   | 0                |           | STA        | Store Althrect                        | D.  | 0   |      |          | -    | 0     | 1   | -     | 13      |

|                  | A-th dorraw                           |                |     |      |       |      |      |     |                  |           | LDA        | Enad Airlinest                        | 0   | 0   |      |          |      | 0     | 1   | -     | 13      |

| 451              | And immediate with A                  | 1              | 1   | - 1  | u     | IJ   |      | ,   | 9                | 1         | × () + ( ) | Exchange D & €, M & L                 | 1   | 1   |      | - :      | - 1  | 0     | •   |       | 4       |

| A 31             | Exclusive Orlimmed at+ with           | 1              | 1   | - 1  | - 0   | 1    | •    | 1   | 0                |           |            | Fley Mers                             |     |     |      |          |      |       |     |       |         |

|                  | <u> a</u>                             |                |     |      |       |      |      |     |                  |           | XTHI       | Exercise top of stack H. R. L.        | - 1 | 1   |      |          | 2    | D     |     |       | 18      |

| 0 P :            | Sr. Inmediate with A                  | 1              | 1   |      | 1     | 3    | 1    | ١   | 0                | 1         | SPHL       | H& L to stack pointer                 | - 1 | - 1 |      | •        |      | ū     | Ξ   |       | 5       |

| 521              | Compare immediate with A              | - 1            | 1   | Ċ    | 1     | !    |      | - 1 | 0                | - 1       | PUHL       | H.S. L. in program counter            | 1   | 1   |      | 1        |      | 9     | 5   |       | Ē       |

| 94C              | Porate A tels                         | 0              | 0   | 0    |       | 2    | ÷    | 1   | 1                | •         | JADB       | A4d 5 & C to H & c                    | 9   | С   | - :  | -        | :    | ß     | -   |       | 13      |

| -                | Pittare Airight                       | - :            | a   | а    | D     | Ċ    |      | - 1 | ı                | <u> -</u> | 0 A D D    | Add D & E to M & L                    |     | J   | Ş    | •        |      | 5     | ξ   | 1     | 10      |

| RAL              | Aprare A left through carry           | - 3            | 9   | 0    | - 3   | 9    | - 1  | - 1 | !                | •         | 3 A D 4    | Add H & L to H & L                    | 0   | ٥   | :    | 2        | 1    | 0     | -   |       | 15      |

| AAR              | Actate A right through                | 9              | 0   | 0    | 1     | - )  | :    | - 1 | - 1              | 1         | 0 A O SP   | Add stack pointer to H & c            | 3   | 5   | 1    |          | :    | 0     | 5   |       | 10      |

| JWP              | Carry                                 |                |     | _    |       |      |      |     |                  |           | BXATE      | State A indirect                      | û   | 0   | Ð    | 5        | ŋ    | ۵     | 1   | 3     | ,       |

|                  | ,,≁p oicenditionai                    |                |     | Ç    | 0     | 0    | 0    | - ! | !                | 10        | STAX D     | Store A indirect                      | 5   | ÷,  | 0    | •        | 9    | 0     | •   | 3     | 7       |

| iC<br>uuc        | Sumplan carry                         | 1              |     | 5    | - !   | 1    | 0    | 1   | 9                | ID.       | LOAXB      | Load A indirect                       | 0   | Ð   | G    | 0        | - 1  | 0     | 1   | :     | 1       |

| ;NC              | IL TO OR NO CORTY                     | 1              | 1   | 9    | 1     | a    | 0    | 1   | 2                | 10        | LDAX D     | Load A indirect                       | 0   | 3   | 0    | •        | 1    | C     | 1   | 3     | 7       |

| .Z<br>:NZ        | .c. mp an zero                        | 1              | 1   | D    | 9     | 1    | 0    | 1   | 0                | 10        | INXB       | increment 8 & Cregisters              |     | 0   | C    | 3        | 3    | G     | ,   |       | 5       |

|                  | 24 TO 31 NO 1840                      | 1              | 1   | Ò    | g     | 0    | 0    | 1   | Ď                | .0        | INXID      | norament D& Eregisters                | Ď   | Ď   | û    | 1        | 2    | Ç     |     |       | 5       |

| .P<br>.M         | Jump an pasitive                      | 1              | 1   |      | - 1   | ÷    | 0    | 1   | 0                | .0        | INXH       | norement H & Livegisters              | 0   | D   |      | 2        | 3    | G     |     |       | 5       |

| JM<br>JPE        | Jump no minus                         | 1              | 1   | 1    | 2     | -!   | 0    | 1   | 0                | 10        | INX SP     | increment stack pointer               | D   | Û   | - 1  | •        | 3    | 0     | •   |       | 5       |

|                  | Joing on parity even                  | 1              | 1   | 1    | 0     | 1    | 0    | 1   | 0                | :0        | DC×8       | Decrement B & C                       | 0   | 0   | :    | 2        | - 1  | g.    | :   | •     | 5       |

| ∌PO              | Jump on parity odd                    |                | 1   | 1    | Ď     | 0    | 0    | 1   | 0                | 13        | DCX 0      | Decrement D & E                       | 0   | 0   | :    | •        | - 1  | 0     | - 1 |       | 5       |

| CALL             | Ca-I unconditional                    | !              | 1   | 0    | 0     | 1    | - 1  | 0   | 1                | 17        | OCX H      | Decrement H & L                       | 0   | 0   | - 5  | 9        | !    | g     |     | -     | 5       |

| CC               | Call on carry                         | !              | 1   | 0    |       | 1    | !    | 0   | 0                | 11 17     | DCX \$P    | Degrement stack pointer               | 0   | Ō   | :    | 1        | - 1  | 0     | ,   |       | 5       |

| CNC              | Calloning carry                       | ŀ              |     | 0    | 1     | 0    | !    | G   | 0                | 11 17     | CMA        | Cumplement A                          | 0   | 0   |      | 2        | - 1  | 1     | 1   |       | 4       |

| CZ               | Cail on zero                          | - [            | 1   | 0    | 0     | 1    | - !  | 0   | 0                | 11 17     | 210        | Set parry                             | 0   | 0   | 1    | •        | ;    | 1     | •   |       | 4       |

| CN2<br>SP        | Ce! an no zera                        | !              | - 1 | Q    | 0     | 0    | 1    | 0   | G.               | 31.17     | CMC        | Complement carry                      | g   | 0   |      | 1        | - 1  | 1     | 1   | •     | 4       |

| CM               | Call on positive                      | •              | - ! | 1    | 1     | 0    |      | 0   | 0                | 11/17     | CAA        | Decime adjust A                       | 0   | 0   | ١    | - 3      | 3    | - 1   | 1   | •     | 4       |

| CPE              | Call on minus                         | 1              | - 1 | - 1  | 1     | 1    | 1    | 0   | •                | 11.17     | SHLD       | Store # & L direct                    | 0   | đ   | 1    | Ĉ        | 0    | a     | 1   | :     | 16      |

| CPE<br>CPO       | Call on parity even                   |                | 1   | 1    | 0     | 1    | 1    | Ò   | 0                | 11/17     | PALD       | Load H & L direct                     | a   | Ü   | •    | 2        | •    | 0     | 1   | :     | 16      |

| RET              | Call on parity odd                    | :              |     | 1    | 0     | 0    | 1    | 0   | 9                | 11/17     | Εi         | Enable Interrupts                     |     | 1   | 1    | 1        | •    | 0     | :   |       | 4       |

| RC RC            | Reluen                                | !              | :   | 0    | 0     | 1    | 0    | 0   | ŧ                | 10        | DΙ         | Orsable interrupt                     | - 1 | - 1 | 3    |          | Ð    | 0     | - 1 | •     | 4       |

| ANC              | Rejust on carry                       | 1              | 1   | 0    | 1     | 1    | 0    | 0   | 0                | 5:11      | NOP        | Na-aperation                          | 3   | ٥   | 0    | ÷        | Ş    | 3     | :   | ;     | 4       |

|                  | Reluin on no carry                    | 1              | 1   | 0    | 1     | g    | 0    | 0   | 0                | 5-11      |            |                                       |     |     |      |          |      |       |     |       |         |

NOTES. 1. DOD or SSS - 000 B = 001 C = 010 D = 011 E = 100 H  $\div$  101 L = 110 Memory = 111 A.

<sup>2.</sup> Two possible cycle times, (5/11) indicate instruction cycles dependent on condition flags.

# CHAPTERS MCS-80 NCS-80NENT FAMILY COMPONENT FAMILY

| CPU | l Group                                     |       |

|-----|---------------------------------------------|-------|

| 8   | 3224 Clock Generator,                       | 5-1   |

|     | 3228 System Controller , , , ,              | 5-7   |

|     | 3080A Central Processor                     | 5-13  |

| 8   | 3080A-1 Central Processor (1.3µs)           | 5-20  |

| 8   | 3080A-2 Central Processor (1.5µs)           | 5-24  |

| N.  | M8D80A Central Processor (-55° to +125°C) , | 5-29  |

| RO  | Ms .                                        |       |

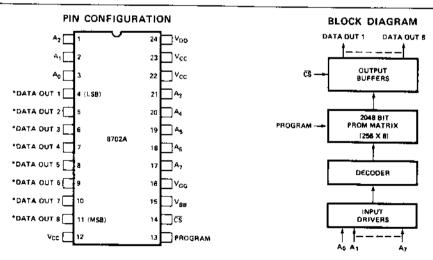

| 8   | 3702A Erasable PROM (256 x 8)               | 5-37  |

| 8   | 3708/8704 Erasable PROM (1K x 8)            | 5-45  |

| 8   | 3302 Mask ROM (256 x 8)                     | 5-51  |

|     | 3308 Mask ROM (1K x 8)                      | 5-59  |

| 8   | 3316A Mask ROM (2K x 8)                     | 5-61  |

| RAI | Ms                                          |       |

| 8   | 3101-2 Static RAM (256 x 4)                 | 5-67  |

| 8   | 3111-2 Static RAM (256 x 4)                 | 5-71  |

| 8   | 3102-2 Static RAM (1K x 1)                  | 5-7   |

| 8   | 3102A-4 Static RAM (1K x 1)                 | 5-79  |

| 8   | 31078-4 Dynamic RAM (4K x 1)                | 5-83  |

| 5   | 5101 Static CMOS RAM (256 x 4)              | 5-9   |

| 8   | 3210 Dynamic RAM Driver                     | 5-9   |

| 8   | 3222 Dynamic RAM Refresh Controller         | 5-99  |

| I/O |                                             |       |

| 8   | 8212 8-Bit I/O Port                         | 5-10  |

|     | B255 Programmable Peripheral Interface      | 5-113 |

| 8   | 8251 Programmable Communication Interface   | 5-13  |

|     | ipherals                                    |       |

|     | 8205 One of Eight Decoder                   | 5-14  |

| 8   | 8214 Priority Interrupt Control Unit        | 5-15  |

| 8   | 9216/8226 4-Bit Bi-Directional Bus Driver   | 5-16  |

|     | ning Soon                                   |       |

| 8   | 8253 Programmable Interval Timer            | 5-169 |

|     | 8257 Programmable DMA Controller            | 5-17  |

| 8   | 8259 Programmable Interrupt Controller      | 5-17  |

Microcomputer tems

# **CPU** Group

8224 8080A-1 8228 8080A-2 8080A M8080-A

# Schottky Bipolar 8224

# CLOCK GENERATOR AND DRIVER FOR 8080A CPU

- Single Chip Clock Generator/Driver for 8080A CPU

- Power-Up Reset for CPU

- Ready Synchronizing Flip-Flop

- Advanced Status Strobe

- Oscillator Output for External System Timing

- Crystal Controlled for Stable System Operation

- Reduces System Package Count

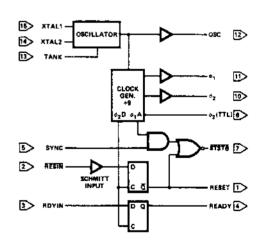

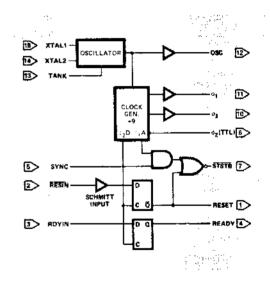

The 8224 is a single chip clock generator/driver for the 8080A CPU. It is controlled by a crystal, selected by the designer, to meet a variety of system speed requirements.

Also included are circuits to provide power-up reset, advance status strobe and synchronization of ready.

The 8224 provides the designer with a significant reduction of packages used to generate clocks and timing for 8080A.

#### PIN CONFIGURATION

#### **BLOCK DIAGRAM**

#### **PIN NAMES**

| RESIN | RESET INPUT                |

|-------|----------------------------|

| PESET | RESET OUTFUT               |

| ROYIN | READY INPUT                |

| READY | READY OUTPUT               |

| 2AMC  | SYNC INPUT                 |

| STSTE | STATUS STB<br>(ACTIVE LOW) |

| ėτ    | 8000                       |

| 92    | CLOCKS                     |

| XTAL 1          | CONNECTIONS             |

|-----------------|-------------------------|

| XTAL 2          | FOR CRYSTAL             |

| TANK            | USED WITH OVERTONE XTAL |

| osc             | OSCILLATOR OUTPUT       |

| \$2 (TTL)       | 92 CLK (TTL LEVEL)      |

| Vcc             | +1/                     |

| V <sub>DD</sub> | +127                    |

| GND             | - av                    |

#### **FUNCTIONAL DESCRIPTION**

#### General

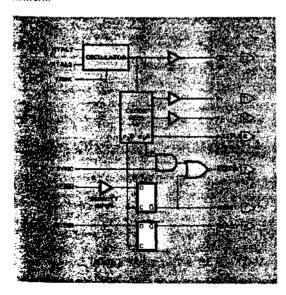

The 8224 is a single chip Clock Generator/Driver for the 8080A CPU. It contains a crystal-controlled oscillator, a "divide by nine" counter, two high-level drivers and several auxiliary logic functions.

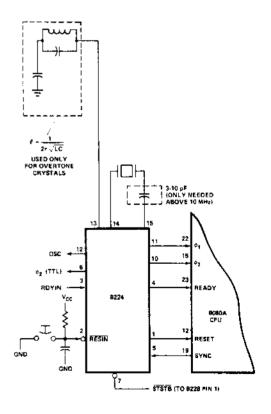

#### Oscillator

The oscillator circuit derives its basic operating frequency from an external, series resonant, fundamental mode crystal. Two inputs are provided for the crystal connections (XTAL1, XTAL2).

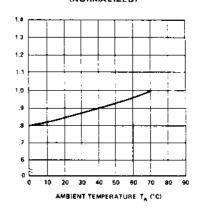

The selection of the external crystal frequency depends mainly on the speed at which the 8080A is to be run at. Basically, the oscillator operates at 9 times the desired processor speed.

A simple formula to quide the crystal selection is:

Crystal Frequency =  $\frac{1}{t_{CY}}$  times 9

Example 1: (500ns toy)

2mHz times 9 = 18mHz\*

Example 2: (800ns toy)

1.25mHz times 9 = 11.25mHz

Another input to the oscillator is TANK. This input allows the use overtone mode crystals. This type of crystal generally has much lower "gain" than the fundamental type so an external LC network is necessary to provide the additional "gain" for proper oscillator operation. The external LC network is connected to the TANK input and is AC coupled to ground. See Figure 4.

The formula for the LC network is:

$$F = \frac{1}{2\pi \sqrt{LC}}$$

The output of the oscillator is buffered and brought out on OSC (pin 12) so that other system timing signals can be derived from this stable, crystal-controlled source.

"When using crystals above 10mHz a small amount of frequency "trimming" may be necessary to produce the exact desired frequency. The addition of a small selected capacitance (3pF - 10pF) in series with the crystal will accomplish this function.

# **Clock Generator**

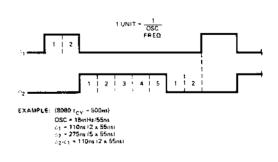

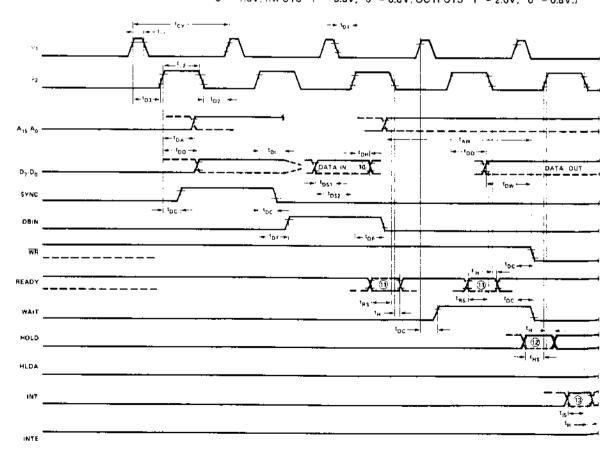

The Clock Generator consists of a synchronous "divide by nine" counter and the associated decode gating to create the waveforms of the two 8080A clocks and auxiliary timing signals.

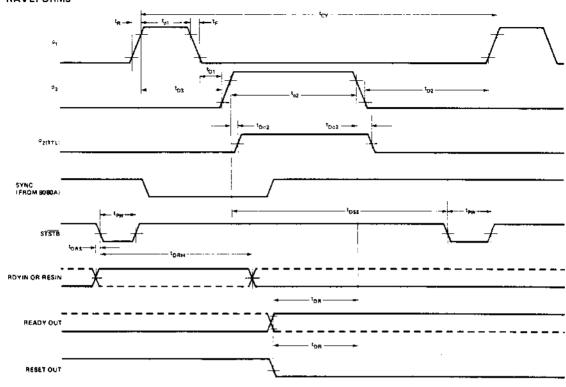

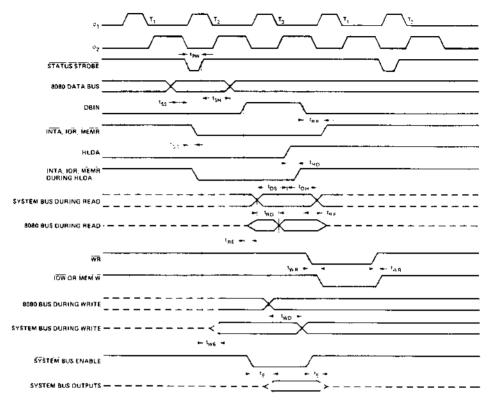

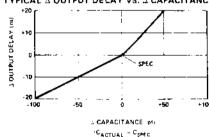

The waveforms generated by the decode gating follow a simple 2-5-2 digital pattern. See Figure 2. The clocks generated; phase 1 and phase 2, can best be thought of as consisting of "units" based on the oscillator frequency. Assume that one "unit" equals the period of the oscillator frequency. By multiplying the number of "units" that are contained in a pulse width or delay, times the period of the oscillator frequency, the approximate time in nanoseconds can be derived.

The outputs of the clock generator are connected to two high level drivers for direct interface to the 8080A CPU, A TTL level phase 2 is also brought out  $\phi_2$  (TTL) for external timing purposes. It is especially useful in DMA dependant activities. This signal is used to gate the requesting device onto the bus once the 8080A CPU issues the Hold Acknowledgement (HLDA).

Several other signals are also generated internally so that optimum timing of the auxiliary flip-flops and status strobe (STSTB) is achieved.

# STSTB (Status Strobe)

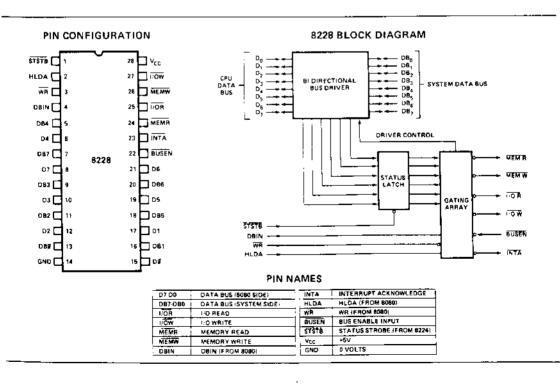

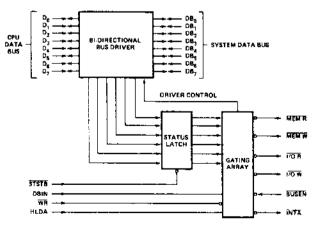

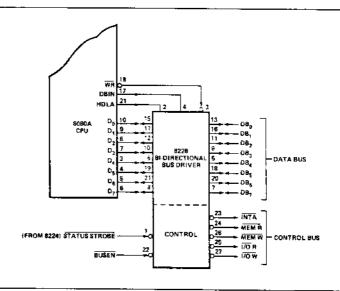

At the beginning of each machine cycle the 8080A CPU issues status information on its data bus. This information tells what type of action will take place during that machine cycle. By bringing in the SYNC signal from the CPU, and gating it with an internal timing signal ( $\phi$ 1A), an active low strobe can be derived that occurs at the start of each machine cycle at the earliest possible moment that status data is stable on the bus. The STSTB signal connects directly to the 8228 System Controller.

The power-on Reset also generates STSTB, but of course, for a longer period of time. This feature allows the 8228 to be automatically reset without additional pins devoted for this function.

# Power-On Reset and Ready Flip-Flops

A common function in 8080A Microcomputer systems is the generation of an automatic system reset and start-up upon initial power-on. The 8224 has a built in feature to accomplish this feature.