### PARTS LIST: 4KRA STATIC READ/WRITE MEMORY

|               | Item                                                                                                                                            | Quantity              |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|               | 4KRA printed circuit board                                                                                                                      | 1                     |

| IC pack #1:   | DM7400N or SN74LS00N<br>DM74L00N or SN74LS00N<br>DM7432N or SN74LS32N<br>DM8097N or 8T97B<br>DM8131N<br>DM8836N<br>DM8837N                      | 1<br>1<br>2<br>1<br>1 |

| MOS IC packs: | AM91L02APC or SYP21L02B 4 packs/ 8 per pa                                                                                                       | ack = 32              |

| Bag #1:       | 6-32x½" pan head screws 6-32 hex nuts #6 lock washers LM340T-5.0 IC regulator 100 ohm 5% ½W resistor 2.2K ohm 5% ½W resistor solder jumper wire | 3<br>3<br>1<br>2<br>2 |

| Bag #2:       | 0.1 mfd disk ceramic capacitor<br>1 mfd 20VDC tantalum electrolytic capacitor<br>15 mfd 20VDC tantalum electrolytic capacitor                   | 26<br>1<br>1          |

| Bag #3:       | heatsink                                                                                                                                        | 1                     |

#### ASSEMBLY INSTRUCTIONS - 4KRA

#### MOS Cautionary Information

Care is necessary in the handling of the MOS devices used in this kit. Many MOS devices are sensitive to static electricity and leakage voltages which may be present on ungrounded soldering irons, etc. While most of these devices incorporate internal protection against overvoltage damage, it is important to remember that damage is a possibility. Cotton clothing should be worn rather than synthetics when handling MOS devices. Soldering irons having grounded tips (through a three-wire cord) are preferable. Keep the MOS devices inside their anti-static carriers until ready for use. Static sensitivity decreases after the devices are soldered into a circuit card.

- 1. Board Orientation: The front surface of the printed circuit card is indicated by the word "FRONT" just above the center of the edge connector fingers. All components will be inserted from this side.

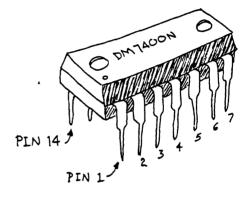

- 2. TTL Device Loading: Refer to the diagram of component location enclosed, and to the section on "Loading DIP Devices." Insert the following I.C.'s in the following locations:

| ( ) DM74LOON                                                                                         | ation |

|------------------------------------------------------------------------------------------------------|-------|

| or DM8214 (Note: This I.C. is used only in the 4KRA-1 4KRA-2 versions. The location is left blank in | IC 41 |

| (Note: This I.C. is used only in the 4KRA-1 4KRA-2 versions. The location is left blank in           | IC 40 |

| 4KRA-2 versions. The location is left blank in                                                       |       |

|                                                                                                      |       |

| AVDA A nameion                                                                                       | the   |

|                                                                                                      |       |

| ( ) DM8836N                                                                                          |       |

| ( ) DM8097N                                                                                          |       |

| ( ) DM8097N I                                                                                        |       |

| ( ) DM7432N I                                                                                        | C 36  |

| ( ) DM7400N I                                                                                        | C 35  |

| ( ) DM8131N I                                                                                        | C 34  |

| ( ) DM8837N I                                                                                        | .C 33 |

Pin 1 is located at the lower left hand corner of these locations, and is indicated by a small etched "1" on all locations except 35.

3. ( ) Solder these I.C.'s to the card, being careful to avoid solder bridges between pins.

NOTE: Solder at the back side of the board only. All holes are plated through.

4. MOS device loading: Refer to the component location diagram. Positioning the devices so that pin 1 is at the lower left hand corner, insert 91LO2APC I.C.'s starting at location 1 and proceeding across the board to the left. There will be 8, 16, or 32 of these I.C.'s included with the kit:

| kit version | number of I.C.'s | number of rows filled |

|-------------|------------------|-----------------------|

| ( ) 4KRA-1  | 8                | 1                     |

| 4KRA-2      | 16               | 2                     |

| 4KRA-4      | 32               | 4                     |

- ( )After these I.C.'s have been loaded, solder them to the card, being careful to observe the precautions concerning MOS devices as well as avoiding solder bridges.

- 5. Disc capacitor loading:

- ( ) Insert 0.1 uf disc ceramic capacitors in the following locations:

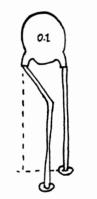

- ( ) C1 through C30. Note: position C2 through C8 and C10 through C30 so that they fit between the I.C.'s without touching. This requires that the leads be bent as shown in fig. (1). Hold each capacitor in place as it is installed by bending the leads apart underneath the board. Don't be alarmed if you can't find C9; there is no C9.

- ( ) Insert C33 through C42 in their proper positions.

- ( ) Solder the leads of all the capacitors and trim the excess lead lengths as close to the board as possible.

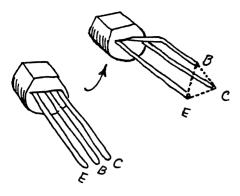

#### LOADING DIP (DUAL IN-LINE PACKAGE) DEVICES

Most DIP devices have their leads spread so that they can not be dropped straight into the board. They must be "walked in" using the following procedure:

- (1) Orient the device properly. Pin 1 is indicated by a small embossed dot on the top surface of the device at one corner. Pins are numbered counterclockwise from pin 1.

- (2) Insert the pins on one side of the device into their holes on the printed circuit card. Do not press the pins all the way in, but stop when they are just starting to emerge from the opposite side of the card.

- (3) Exert a sideways pressure on the pins at the other side of the device by pressing against them where they are still wide below the bend. Bring this row of pins into alignment with its holes in the printed circuit card and insert them an equal distance, until they begin to emerge.

- (4) Press the device straight down until it seats on the points where the pins widen.

- (5) Turn the card over and select two pins at opposite corners of the device. Using a fingernail or a pair of long-nose pliers, push these pins outwards until they are bent at a 45 degree angle to the surface of the card. This will secure the device until it is soldered.

#### SOLDERING TIPS

- (1) Use a low-wattage iron -25 watts is good. Larger irons run the risk of burning the printed-circuit board. Don't try to use a soldering gun, they are too hot.

- (2) Use a small pointed tip and keep it clean. Keep a damp piece of sponge by the iron and wipe the tip on it after each use.

- (3) Use 60-40 rosin-core solder ONLY. DO NOT use acid-core solder or externally applied fluxes. Use the smallest diameter solder you can get.

- NOTE: DO NOT press the top of the iron on the pad or trace. This will cause the trace to "lift" off of the board which will result in permanent damage.

- (4) In soldering, wipe the tip, apply a light coating of new solder to it, and apply the tip to both parts of the joint, that is, both the component lead and the printed-circuit pad. Apply the solder against the lead and pad being heated, but not directly to the tip of the iron. Thus, when the solder melts the rest of the joint will be hot enough for the solder to "take," (i.e., form a capillary film).

- (5) Apply solder for a second or two, then remove the solder and keep the iron tip on the joint. The rosin will bubble out. Allow about three or four bubbles, but don't keep the tip applied for more than ten seconds.

- (6) Solder should follow the contours of the original joint. A blob or lump may well be a solder bridge, where enough solder has been built upon one conductor to overflow and "take" on the adjacent conductor. Due to capillary action, these solder bridges look very neat, but they are a constant source of trouble when boards of a high trace density are being soldered. Inspect each integrated circuit and component after soldering for bridges.

- (7) To remove solder bridges, it is best to use a vacuum "solder puller" if one is available. If not, the bridge can be reheated with the iron and the excess solder "pulled" with the tip along the printed circuit traces until the lump of solder becomes thin enough to break the bridge. Braid-type solder remover, which causes the solder to "wick up" away from the joint when applied to melted solder, may also be used.

#### **IDENTIFICATION OF COMPONENTS**

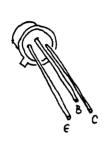

transistor - TO-92 package (plastic)

transistor - TO-18 package (metal can)

dipped tantalum electrolytic capacitor

ceramic disc capacitor

NOTE: PIN 1 MAY BE INDICATED

BY CORNER DOT OR

CUT-OUT.

dual-inline-package (DIP) integrated circuit 8,14,16,24 or 40 pins (14 pin shown)

carbon film resistor 5% (gold) or 10% (silver)

metal film 1% precision resistor

regulator IC or power transistor (TO-220)

- 6. Tantalum capacitor installation:

- () Install 1.0 uf, 20 volt tantalum capacitors C31 and C32 as shown on the component location diagram. The positive lead of these capacitors, as indicated by a "+" on the body of the capacitor, is connected to the printed circuit traces on the top side of the board.

- ( ) Bend the leads outwards underneath the board and solder. Trim the leads as close to the board as possible.

- () Install the 15 uf, 20 volt tantalum capacitor C43 in the location shown in the component location diagram. The positive lead connects to the printed circuit trace on the bottom side of the card, through the hole which has a square area around it on the top side.

- ( ) Bend and solder the leads to this capacitor as above. Trim the leads as close to the board as possible.

fig. 1 - lead formation,

capacitors C2-C8, C10-C30

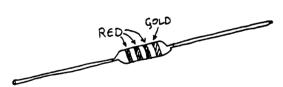

7. Resistor Installation: Referring to the component location diagram, install resistors R1 through R4 as follows:

| resistor value                         | color code                                 | location         |

|----------------------------------------|--------------------------------------------|------------------|

| ( ) ( ) 2,200 ohms<br>( ) ( ) 100 ohms | red-red-red-gold<br>brown-black-brown-gold | R1, R2<br>R3, R4 |

| ( ) Solder and trim leads.             | brown-black-brown-gold                     | 110, 114         |

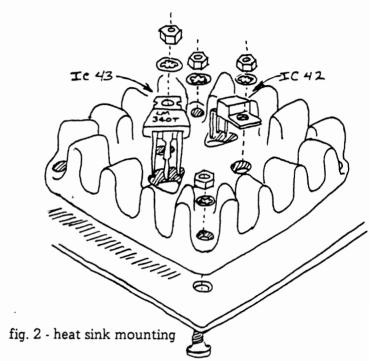

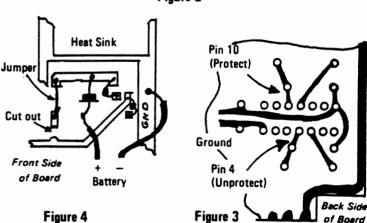

- 8. Heat Sink Installation:

- () Install the black, finned heat sink on the top side of the card, flat face down, with all holes lined up. Secure the heat sink to the card with the two 6-32 machine screws, using lockwashers underneath the nuts. Install the screws with their heads on the underside of the card. Do not tighten screws completely until regulator I.C.'s are installed.

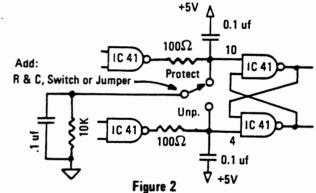

- 9. Regulator Installation: Refer to Fig. 2. Position I.C.'s 43 and 42 (LM340T-5.0) over their mounting locations on the heat sink and observe how the leads must be bent to engage their holes on the card. The center lead must be bent at a point approximately 0.2 inches further away from the body of the regulator. Use of silicone heatsink compound is recommended between the regulator I.C.'s and the heatsink.

- ( ) Bend the leads and adjust them, if necessary, so that the regulators may be mounted to the heat sink without the leads touching the heat sink.

- ( ) Secure the regulators with 6-32 machine screws, using lockwashers under the nuts. Insert the screws from the bottom side of the card.

- ( ) Solder the leads of the regulators and clip the excess off as close to the card as possible.

- 10. ( ) Install Augat receptacle pins in address-select holes as follows:

- ( ) Wedge the board between two objects so that it stands slightly off vertical with the top side up.

- ( ) The Augat receptacle pins are mounted on a DIP-style metal carrier. Pull off one pin and insert it from the top side of the board into one of the address-selection holes. The fit will be loose.

- ( ) Carefully solder the pin to the pad. The pin will end up out of perpendicular to the board.

- () Insert a component lead into the receptacle. Reheat the solder and, using the component lead, adjust the position of the receptacle until it is more nearly perpendicular to the board. Allow the solder to solidify while holding the pin as steady as possible. A mottled or crystallized solder joint indicates a "cold joint" and should be reheated.

- ( ) When all the pins have been installed, check carefully for cold joints or solder bridges.

#### 4KRA — OPERATING RESTRICTIONS

- 1. Take care not to attach clip leads to the top edge of the card when the unit is powered. This will short the +8 volt bus to ground.

- 2. Due to regulator current limitations, no more than 8 additional standard 2102 type RAM chips may be installed on a -1 or -2 versions. Low power units, available from Processor Technology, are necessary for operation of a full card (4K).

- 3. If RAM chips with worst case access times of greater than 500 nsec and less than 1.0 microsecond are used, the board must be strapped for one waiting state.

- If RAM chips with worst case access times of 1.0 to 1.5 microseconds are used, the board must be strapped for two waiting states.

## 4KRA ADDRESS RANGE SELECTION

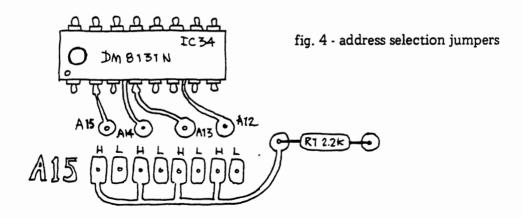

The starting address of the 4KRA is selected by the connection of four jumpers at the lower right-hand corner of the board. Each of the four round pads on the upper row has two oval pads below it. The left-hand pad of the pair on the bottom row is connected to a trace on the top side of the card. This set of pads will be designated H. The other set of pads, which connect to the ground trace on the bottom side of the board, will be designated L. (See fig. 4).

Using short lengths of bare wire,#24or 26, make the connections as indicated in the chart below. Only the indicated addresses are available for starting addresses; no intermediate addresses may be used.

| 200001116 11 | aar coo |     |     |     |         |

|--------------|---------|-----|-----|-----|---------|

| Decimal      | Octal   | A15 | A14 | A13 | A12     |

| 0            | 0       | L   | L   | L   | L       |

| 4,096        | 10,000  | L   | L   | L   | H       |

| 8,192        | 20,000  | L   | L   | H   | ${f L}$ |

| 12,288       | 30,000  | L   | L   | H   | Н       |

| 16,384       | 40,000  | L   | H   | L   | L       |

| 20,480       | 50,000  | L   | H   | L   | H       |

| 24,576       | 60,000  | L   | H   | H   | L       |

| 28,672       | 70,000  | L   | H   | H   | H       |

| 32,768       | 100,000 | H   | L   | L   | L       |

| 36,864       | 110,000 | H   | L   | L   | H       |

| 40,960       | 120,000 | H   | L   | H   | L       |

| 45,056       | 130,000 | H   | L   | H   | H       |

| 49,152       | 140,000 | Н   | H   | L   | L       |

| 53,248       | 150,000 | Н   | H   | L   | H       |

| 57,344       | 160,000 | Н   | Н   | H   | L       |

| 61,440       | 170,000 | H   | Η . | H   | H       |

|              |         |     |     |     |         |

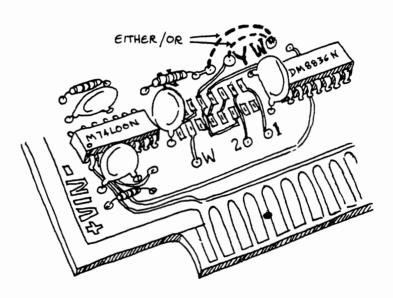

#### WAIT STATE SELECTION (See fig. 3)

Since the RAM chips shipped by Processor Technology are specified for operation at 500 nanoseconds, no waiting time is required. The circuit is set up for this condition by connecting a jumper wire between the "W" pad above I.C.39 and the "N" pad to its left just next to the 2.2K resistor.

If slower RAM chips are installed in a -1 or -2 card, the waiting time may have to be enabled. To do this, the jumper is removed from "N" to "W", and a jumper is installed from "Y" to "W". The number of wait states, each .5 micro-second, is determined by the numbered pad (2 or 1) connected to the "W" pad below the I.C. 40. If waiting time is enabled, one of these must be connected.

W = wait

N = no

Y = yes

fig. 3 - optional wait state jumpers connect from "W" to "N" for normal operation connect from "W" to "Y" for wait states (IC 40 must be installed)

#### THEORY OF OPERATION - 4KRA

Address lines AØ through A9 are connected directly from the bus to the 10 address input pins of each random-access memory (RAM) chip on this module. Likewise, each line of the data-out bus DO Ø through 7 connects directly to one chip in each "page" of memory represented by eight chips. Each chip in the page therefore stores one bit of the word.

Only one page is selected at a time, however, and that page alone reads information to or writes information from the data busses. The data outputs of the RAMs are "tri-state" types which "float" in a high-impedance condition when they are not selected. They may therefore be connected in parallel from one page to the next, so that only that bit of the selected page sends data out.

Data from the RAMs is sent out to the 8097 tri-state bus drivers IC37 and IC38. These drivers are enabled only if the output from pin 6 of IC36 is low. IC36 is a 7432 positive-OR gate which can also be viewed as a negative-AND gate, whose output will be "low" only if both inputs are "low". Thus, the output pin 6 will be "low" only if pins 1, 2, and 5 are also "low".

This condition exists when (a) SMEMR is "high", (b) PDBIN is "high", and (c) the output pin 9 of comparator IC34 is "low". (a) and (b) occur when the processor requests memory data. (c) occurs when the address bits on address bus line A12 through A15 match the setup of the jumpers 12 through 15. Thus, the first two conditions occur for any memory read operation, but condition (c) occurs only when this particular memory module is addressed.

Address bits A10 and A11 choose the page of memory to be accessed. They are decoded into one of four outputs by IC33 and IC35. A "select page" signal from IC35 is a "low" level and may occur on only one of its outputs at a time. Each output of IC35 is connected to all the "chip enable" pins of a page of RAM.

Thus, A12 through A15 select the card, A10 and A11 select the page, and A0 through A9 select the word within the page to be read. The data is presented to the bus drivers IC37 and IC38, which gate the data out to the DI bus when that data is requested by the processor (SMEMR and PDBIN).

The RAM chips supplied with the 4KRA are guaranteed to provide settled data within one CPU cycle time (500 nanoseconds). When such fast RAMs are used, the "W" jumper which selects waiting time is connected to the "N" terminal, which connects a "high" level to pin 12 of IC38. When this section of the bus driver is enabled ("low" level on pin 15) by a "low" level on the output (pin 9) of the 8131 comparator IC34, the XRDY signal to the bus is driven "high". Therefore, the memory card sends a "ready" signal back as soon as it is addressed. The data will be ready before the processor is.

If, however, other 2102-type RAM chips are used having slower access time, one or two "wait" cycles must be allowed to pass before the CPU is allowed to accept the data. 74109 IC40 comprises a two-bit shift register which may be selected to give a "high" level at pin 6 after one or two PSYNC pulses. The 74109 IC40 is a dual J-K flip-flop with positive clock. The outputs of each section change on the low-to-high transition of the clock signal depending on the condition of the J and  $\overline{K}$  inputs. The changes occur according to the following table:

|               | no change                        |

|---------------|----------------------------------|

|               | Q goes "high"                    |

|               | Q goes "low"                     |

| J high, K low | Q changes to the opposite level. |

When PSYNC goes "high" section 2 is reset, if it was not already reset. Pin 6 goes "low" and since both J and  $\overline{K}$  inputs to section 1 are now "low", section 1 Q goes "low" on the high-to-low transition of  $\phi 2$  clock.

When PSYNC goes "low" section 2 may change state on the next high-to-low  $\phi 2$  transition. If the J input (pin 2) is high, section 2 will be "set" on the next high-to-low transition of  $\phi 2$ . This will happen if the jumper is connected from W to "1". The same clock transition will cause section 1 to change state. Note that the "old" data at the output of section 2 is what counts for this clock transition. The "new" data does not appear at the outputs until some time after the clock transition.

Now both sections are set. Since pin 2 is now "low" and pin 3 "high", section 2 will remain this way until PSYNC resets it. The same conditions hold true at the inputs to section 1, so it will remain without changing state.

If the jumper was connected to "2" (pin 10), then section 2 would not set on the first clock pulse after PSYNC. Section 1 would still change state on this transition, however. The conditions would then be correct to allow section 2 to set on the next clock pulse. Section 1 would change state again on that transition. The two sections would then "lock up" with section 1 reset and section 2 set.

Thus, if IC40 is installed and the wait states are jumpered in, pin 6 will go "high" on the first high-to-low transition of  $\phi 2$  after PSYNC if 1 wait state is selected. Pin 6 will go "high" on the second high-to-low transition of  $\phi 2$  after PSYNC if 2 wait states have been selected. Pin 6 will in either case remain "high" until the next PSYNC.

The "write" sequence of events is similar to the "read" sequence except that "MWRI" is high instead of "SMEMR". The output drivers IC 37 and IC 38 are disabled, and the low-active "write" input of the RAMs is driven "low" for the duration of MWRI pulse. The timing of this pulse is controlled by the CPU.

In order for this to happen, pin 8 of IC 41 must be "low". IC 41 is wired as a latch which may be set or reset by the PROT or UN PROT inputs when the board is selected (pin 9 of IC 34 "low"). The resistor-capacitor networks guard against noise pulses setting the latch. When the latch is set by the "PROT" input, pin 8 is "high" and pin 6 is "low". This inhibits the "write" pulse and sends a low-active PS signal out via IC 38. This signal notifies the CPU that the page of memory is protected.

Since no "master clear" signal exists on the card, it is necessary to issue the proper "protect" and "unprotect" signals to memory when first powering the computer.

#### **4K MEMORY TEST PROGRAM**

The 4K memory test program provides an effective test of any 4K segment of memory. The incrementing pattern used for the test will find errors in any but the most cantankerous, pattern sensitive, dynamic memory.

The test is performed in two segments, write and read. Write begins at the bottom of the 4K address (LOAD) writing zero and then writes an incrementing bit pattern to the "top." After each location is then read and compared to its proper pattern, and if no errors are found, the starting pattern is incremented and the test is performed again.

This read, write sequence continues until an error is found or the machine is halted. If an error is found all information relating to the error is saved in locations 000–006.

#### **ADDRESS**

- 5 High Address Error Pointer

- 4 Low Address Error Pointer

- 3 Write Data

- 2 Read Data (Error)

- 1 Page Down Count

To use the program clear memory locations 0000-0006 and load the hex code starting from location 0007. As the code is entered check the address for each input as a test of proper code and location. After all code is entered check each location for the proper bits.

Then press the reset and run switches and the test should then proceed as indicated by the address lights.

NOTE: A full test of all 256 bit patterns to all 4096 locations takes about 30 seconds with fast memory. This test should be repeated for one hour with the cover to the computer in place.

#### APPENDIX I

```

0000

0000 *

<<< 4K MEMORY TEST PROGRAM

>>>

0000

0001 *

0002 * ASSEMBLED ON SOFTWARE PACKAGE #1

0000

0003 *

0000

PROCESSOR TECHNOLOGY CORP.

0000

0004 *

0005 * 2465 FOURTH STREET

0006 * BERKELEY, CALIF. 94710

0000

0000

0007 *

0000

0000

0008 LOAD EQU 4096

0009 TOP EQU 32

0000

0010 SP EQU 6

0000

0015 *

0000

0020 ORG 7

0000

0025 *

0007

0030 START LXI SP, 6 SET UP ERROR CATCH

0007 31 06 00

0035 XRA A CLEAR REG A

000A AF

MOV B, A CLEAR B

000B 47

0040

0045 *

000C

0050 OVER LXI H, LOAD LOAD ADDRESS

0053 MOV C,B FIRST WRITE DATA

000C 21 00 10

000F 48

0055 WRITE MOV M,C PUT IN MEMORY

0010 71

0060 INX H NEXT ADDR

0065 INR C NEXT WRIT

0011 23

0065

0070

0075

0080

NEXT WRITE DATA

0012 0C

H A VOM

0013 7C ·

CPI TOP IS H OVER THE TOP?

0014 FE 20

JNZ WRITE IF NOT THEN MORE

0016 C2 10 00

0081 *

0019

0082 * READ TEST ROUTINE

0019

0083 *.

0019

0085

MOV A,B GET FIRST WRITE DATA

MVI C,4 C HOLDS PAGE COUNT

0019 78

0090

001A 0E 04

001C 21 00 10

LXI H, LOAD LOAD ADDRESS

0095

0096 *

001F

0100 NEXT LXI D,

0110 READ CMP M

D. 1024 D-E COUNT K'S

001F 11 00 04

IS DATA OK?

0022 BE

JNZ

ERROR IF NOT CATCH IT

0023 C2 3B 00

0112

DCR E

0115

0026 1D

.0118

JNZ OKTES

DCR D

0027 C2 2E 00

0120

ANOTHER PAGE DOWN

002A 15

JZ ONEK COUNT K'S

0125

002B CA 33 00

0133 *

00SE

0135 OKTES INX H

NEXT ADDRESS

00SE 53

INR A

0140

002F 3C

JMP READ

0030 C3 22 00

0145

0146 #

0033

0150 ONEK DCR C

ONE MORE K DOWN

0033 0D

JNZ NEXT MORE K'S TO COUNT

0034 C2 1F 00

0155

0037 04

0157

INR

В

0038 C3 0C 00

0160

JMP OVER

0170 *

003B

0175 *

ERROR STUFF ROUTINE

003B

0180 *

003B

0185 * ADDRESS

0038

0186 *

5 HAS HIGH ERROR ADDR

003B

0187 * 4 HAS LOW * *

003B

0188 * 3 HAS WRITE DATA

0189 * 2 HAS READ DATA (ERROR)

0190 * 0 HAS PAGE DOWN COUNT

003B

003B

003B

0210 *

003B

0215 *

003B

0216 ERROR PUSH H

STUFF ADDRESSES

003B E5

MOV D.A GET WRITE DATA

003C 57

0550

MOV E,M GET READ DATA

0225

003D 5E

0230

PUSH D PUT ON STACK

003E D5

PUSH B ALL OF IT

003F C5

STOP THIS NONSENSE

0240 AHHHH HLT

0040 76

0245 *

0041

0250 *

0041

© Processor Technology Corp.

```

:

| - |  |

|---|--|

| × |  |

| 2 |  |

| Z |  |

| ш |  |

| ۵ |  |

| ۵ |  |

| ٥ |  |

| CONSTANT     | DEFINITION |             | CBDH   | 1AH / Hex  | -         | -            | 1050 ( Decimal | 105 / 060111411 |         | _       | Octal  | 720     |     | 110118 | Out 10B   Binary | 2      | -       | ASCII     | . B. V. | -        |       | OPERATORS  |          |             |             |             | <b>+</b> | •            |            |          |         |     | STANDARD    | SETS        |         | A SET 7  | B SET 0   | SET    |          | SET     |        | SFT       |             | , CE 1   | 3            | 361    |           |         |   |                                                           |                            |                                                                            |

|--------------|------------|-------------|--------|------------|-----------|--------------|----------------|-----------------|---------|---------|--------|---------|-----|--------|------------------|--------|---------|-----------|---------|----------|-------|------------|----------|-------------|-------------|-------------|----------|--------------|------------|----------|---------|-----|-------------|-------------|---------|----------|-----------|--------|----------|---------|--------|-----------|-------------|----------|--------------|--------|-----------|---------|---|-----------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

|              |            | ΧΗ <b>Χ</b> | XRX    | XBA        | XBA       |              |                |                 | XHA     |         |        | a Aac   |     | OHA    |                  | ORA E  | ORA     | A C       |         | A C      | ORA A |            | E :      | CMP         |             | CMP E       | CMP      | CMP          | CMP        |          |         |     | PSEUDO      | INSTRUCTION |         | ORG Adr  | _         | N D16  | •        | 5 D16   | . 08   | V D16 1 1 |             |          |              |        |           |         |   |                                                           |                            | eii riags except CARRT affected;<br>(exception: INX & DCX affect no Flags) |

| LATOR*       | ,          | <b>10</b>   | ပ      | ۵          | E AB      | . 3          | Ε.             | _               | M       | <       |        | 8       |     | ، د    | ٥                | E 83   | I       | _         | , 2     | ٤ •      | A B7  | 0          |          |             | ٥           | ш           | _        | ر            | Σ          |          |         | 60  | ပ           | 0           | ш       |          | END       |        | <        | SO      | 8 08   | OM<br>C   | ٥           | ш        |              |        |           | Σ ∢     | • | Adr = 16 bit address                                      |                            | (exception: INX & DCX affect no I                                          |

| ACCUMULATOR* |            |             |        | 82 ADD     | 83 ADD    |              |                |                 | 86 ADD  | 87 ADD  |        | 88 ADC  |     |        |                  | 8B ADC | 8C ADC  | 8D ADC    |         |          |       |            |          |             |             | 93 SUB      | 94 SUB   | 95 SUB       | 96 SUB     |          |         |     | 99 SBB      | 9A SBB      | 98 888  | 9C SBB   | 9D SBB    | 9E SBB | 9F SBB   |         | AO ANA | A1 ANA    | A2 ANA      |          |              |        |           |         |   | Adr = 16                                                  | •                          | i                                                                          |

| MOVE (cont)  | Š          | 2           | S<br>W | <b>№</b>   | MOV E.E   | 2            |                | 2               | WO<br>W | MOV E.A |        | MOV H.B | NO. | 2 3    | NO<br>MO         |        | MOV H.H | MOV       | NO.     |          |       | - AOM      |          | 2           | Ş<br>W<br>W | Ş<br>₩      | ΑOΑ      | Ş<br>W<br>O∧ |            | MOV      |         | WO\ | MOV M.C     | MOV         | MOV M.E |          | MOV M.L   | •      | MOV M.A  |         | MOV    | MOV A.C   | <b>M</b> O∨ | WO<br>W  | <b>Q</b>     | 2      | 2         | 2 2     |   | hat evaluates                                             |                            |                                                                            |

|              | 9          |             |        | 2 <b>V</b> | <b>28</b> |              | 3 5            | 2               |         | ا<br>5  |        | 8       |     |        | 62               | 63     | 64      | 65        | y       | 2 2      | 6     | 88         | ) C      | ָ<br>מים    | B.D         | <b>B</b> .E | В'н      | B.L          | 8.™        | V B,A 6F |         | C.B | V C.C 71    | C.D         | C.E     | C.H      | V C.L 75  | C.M    | V C.A 77 |         | D.B    |           | 0,0         | V D.E 7B | D,H          | 10     | 2         |         | Š | constant, or logical/arithmetic expression that evaluates |                            |                                                                            |

| ROTATE       | 20         |             |        |            | 1F RAR    |              |                |                 |         | CONTROL |        | OO OO   |     |        |                  | E      |         |           |         | MOVE     |       | 40 MOV     | ? 7      | ; ;         |             |             |          |              | 46         | 47 MOV   |         |     | 49 MOV      |             | 4B MOV  |          | 4D MOV    | 4E MOV | 4F MOV   |         |        |           |             | 53 MCV   | 54 MOV       |        |           | 57 MOV  |   | or logical/arithm                                         | to a 16 bit data quantity. | only CARRY affected                                                        |

| RESTART      | C7 RST 0   | 100         | 2      | 2          | RST       |              | FF RST 5       | 2               | 42.     | HST     |        |         |     |        |                  |        |         | STACK OPS |         | פונסו ס' | ב מ   | DS PUSH    | 2        | F5 PUSH PSW |             | C1 POP B    | 90       | 00           |            | <b>.</b> | F3 XTHI |     |             |             |         | SPECIALS |           |        |          |         | 37 STC |           |             |          | INPUT/OUTPUT |        | D3 OUT D8 | Z       |   | D16 - constant, c                                         | to a 16 bit                | t - only CARF                                                              |

| RETURN       | RET        | NA Z        |        | 7.         | HNC       | ٦,           | RPO            | 500             |         | Ŧ       | Æ.     |         |     |        |                  |        | 9       | IMMEDIATE |         |          | 5 2   | LX: U. D16 |          | -SP.        | •           |             |          |              | DOUBLE ADD | DAD B    | DAD     |     |             |             |         |          | OAD/STOBE | 30000  |          | 2 2 2 2 |        | `         | LDA Adr     |          |              | STAX D | SHLD Adr  | STA Adr |   | evaluates                                                 |                            |                                                                            |

| RET          | 65         |             | 3 8    |            | _         | <b>→</b> Adr | EO             |                 |         |         | F8     |         |     |        |                  |        |         | ,         |         | 5        | :     | - 7        | -        | 15 BO       | <u> </u>    |             |          | _            | 00         | 60       | 61      |     | NT**        |             | α       |          | ء د       | ט נ    |          | Ξ.      | 2 ر    | Σ •       |             |          | B 05         | ٥      |           | SP 32   |   | constant, or logical arithmetic expression that evaluates |                            |                                                                            |

| CALL         | CD CALL    |             | 20 00  |            |           | ဋ            | E4 CPO         |                 |         | 7 5     | ე<br>S |         |     |        |                  |        | Acc     | IMMEDIATE |         | Ce ADI   |       |            |          |             | <b>E</b> 6  |             | F6 ORI   | FE CPI       |            |          |         |     | DECREMENT   |             | 90 PO   |          |           |        |          |         |        |           | SO OS       |          | OB DCX       |        |           | 38 DCX  |   | logical arithmeti                                         | to an a bit hara quantity. | all Flags (C.Z.S.P) affected                                               |

|              |            |             |        |            |           | Ť            | 5              |                 |         |         |        |         |     |        |                  |        |         |           |         | -        | ٠-    |            | <u>-</u> | $\hat{}$    | _<br>I      | _           | _        | _            |            |          |         |     | INCREMENT"* |             |         |          |           |        |          |         |        |           |             |          |              |        | I         |         |   | 5                                                         | Ĕ                          | Ö                                                                          |

|    |                 |        |          |          | 8        |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            | 3        | <u> </u>   | •        |        |            |                                                                                     |        |            |              |             |             |

|----|-----------------|--------|----------|----------|----------|---------------|----------|------------|------|----------|------------|------------|----------|----------|---------------|--------|----------|---------|------|----------|----------------|----------|-----------------|--------|--------------|----------|-----------|------------|------------|----------|------------|----------|--------|------------|-------------------------------------------------------------------------------------|--------|------------|--------------|-------------|-------------|

|    |                 |        | acters   | @        | spa      | _             | •        | •          | Ü    | ď        | ۰ م        | <b>5</b> . | ,        |          | ٠.            | 1      | •        | • _     |      | . ~      |                |          | ٠ ٧             | , H    | 1            | . ~      | ٠ _       | • . •      | _          |          | - 1        |          |        |            |                                                                                     |        |            |              |             |             |

|    | ABLE            |        | Cha      | Ş        | ୡ        | 21            | 8        | 23         | 24   | ķ        | 3 6        | 2 6        | 3 6      | 3 8      | 60            | מ מ    | ָ<br>נ   | ָ<br>מַ | 3 K  | 1 4      | , <b>&amp;</b> | ğ        | Ş               | 2      | i<br>E       | i ii     | 20        | S. C.      | S          | 35       | 3          | ;        |        |            |                                                                                     |        |            |              |             |             |

|    | HEX-ASCII TABLE |        |          |          |          |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            |          |            |          |        |            |                                                                                     |        |            |              |             |             |

|    | EX-A            |        | 9        | 0        | -        | ~             | က        | 4          | · vo | · (c     | ,          | ٠ ۵        |          | ,        | 4             | α .    | <b>.</b> | ) (     | u    | u        | . ლ            | ) I      | : -             |        | <b>×</b>     | : _      | 2         | z          | 0          | ۵        | 0          | Œ        | S      | -          | =                                                                                   | >      | . ≥        | ×            | <b>&gt;</b> | 7           |

|    | I               |        | Print    | 8        | 3        | 35            | 33       | 34         | 32   | 9        | 3 6        | 5 8        | 3 8      | 3        | 41            | . 6    | 4        | ? ;     | 4    | 4        | 47             | 8        | 9               | ₹      | 48           | <b>Q</b> | 9         | <b>4</b> E | 4          | S        | 5          | 52       | 8      | 54         | 55                                                                                  | 8      | 24         | 8            | 29          | ₹           |

|    |                 |        |          |          | L        |               | _        |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          | u               | ļ      |              |          |           |            |            |          |            |          |        |            |                                                                                     |        |            |              |             |             |

|    |                 | PSW    | ₹        |          |          |               | 80       |            | ,    |          | ₹          |            | Ą        | 2        | 2             | }      |          |         |      |          |                |          | HEX-ASCII TABLE |        | 0            | b        | _         |            |            |          |            | 5        |        | _          |                                                                                     |        |            |              | MODE        | 5           |

|    | 윤               | Š      | ٩        | ٥        | g<br>G   | PUS           | S<br>E   | RST        | 2    | SPH      | 2          | <u>.</u>   | į        | ; ;      | g             | RST    |          |         |      |          |                |          | - ASCI          |        | Von-Printing |          | NULL      | BELL       | <b>1</b> 8 | 5        | 5          | FOR      | 8      | Š          | TAPE                                                                                | X-OFF  |            | ESC          | ALT         | <b>B</b> UB |

| ٠, | ß               | Ξ      | F2       | £        | I        | FS            | 9        | F7         | FB   | E G      | ¥.         | <u> </u>   | ָר<br>בי | 9        | Щ             | i ii   |          |         |      |          |                |          | HEX             |        | Non          |          | 8         | 0          | 8          | S        | 8          | 8        | 8      | Ξ          | 12                                                                                  | 13     | 7          | <b>⊕</b>     | 6           | 7.          |

|    |                 |        |          |          | Þ        | Þ             | 8        |            |      |          | Þ          | 8          | Þ        |          | 8             |        |          |         | Þ    | 8        | Αď             |          | 8               |        |              |          | ğ         |            | Þ          |          | 8          |          |        |            | ğ                                                                                   |        | þ          |              | <b>8</b>    |             |

|    |                 | _      |          |          | `        | <u>-</u><br>ب | _        | -          | 0    | ٥        | •          | _          |          | OH       | _             | ~      |          |         | `    | _        | _              |          | _               | ر<br>ق | 0            | I        | `         | Į.         | CPO Adr    | エエ       | _          | ▼        |        | ¥          | `<br>                                                                               | ပ္     | `          |              | _           | ro<br>C     |

|    |                 |        |          |          |          |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            | ž        | ₹          | RS       | RPE    | Ş          | E E                                                                                 | XCHG   | CPE        | •            | X           | HS          |

|    | ပီ              | ပိ     | ပ်       | 8        | ပ္ပ      | 2             | 벙        | Ç          | 8    | ā        | DS         | 2          | 0        | 05       | 90            | 0      | 80       | 60      | ۵    | 08       | 8              | 8        | 9               | O.     | EO           | Ē        | E2        | E3         | m<br>4     | ES       | <b>E</b> 6 | E7       | E      | E3         | Ā                                                                                   | EB     | Я          | <b>E</b>     | Ш           | Ħ           |

|    | _               |        | _        |          | _        |               | _        | _          | _    | <i>~</i> | ^          |            | _        |          | ~             | _      | _        |         | _    |          | _              |          | 5               | _      | <b>.</b>     |          | ^         |            | _          |          | ~          | _        |        | <b>.</b>   | ¥ď                                                                                  | Υď     | Ā          | _            | 80          | ٥           |

|    | ¥               | v<br>¥ | ₹        | ¥        | ¥        | -<br>¥        | ¥        | Y<br>Y     | Æ    | ₽        | R          | Æ          | R<br>T   | <u>₹</u> | ¥.            | ₽<br>Y | A<br>E   | ₹       | ₹    | Ā        | ¥              | RAL      | ¥               | ¥<br>ĕ | MP           | ₽        | MP        | ΜP         | CMP        | MP<br>MP | Z<br>Z     | MP<br>MP | ZNE    | ğ          | NZ                                                                                  | Ā      | ZNZ        | SHE          | ₫           | ST          |

|    | ₹<br>9          | ₹<br>5 | ₹<br>8   | ۲<br>ا   | <b>4</b> | ¥ 9           | ۷<br>9   | ¥          | × 81 | × 6      | ×          | × 8/       | ×        | ×        | ×             | ×      | 8        |         | B2 O | _        |                | 35       | 98              | 37 0   | 38<br>C      | _        | S<br>S    |            | ပ္ထ        | _        |            | ۳<br>د   | œ<br>8 | _          | 5<br>8                                                                              | ጛ<br>ይ | о<br>7     | 55           | <b>Y</b> 90 | 7.<br>H     |

|    | •               | `      | •        | •        | •        | `             | •        | •          | `    | •        | `          | `          | `        | •        | `             | `      | _        | _       | _    |          | _              | _        | _               | _      | _            | _        | _         | _          |            | _        | _          | _        | •      | •          | Ŭ                                                                                   | Ū      | Ŭ          | •            | •           | •           |

|    | Α.              | Y.     | A.D      | A.       | ¥.       | A.L           | Σ        | <b>∀</b> . | 8    | ပ        | ۵          | ш          | I        | ı        | Σ             | ∢      | 83       | ပ       | ۵    | ш        | I              | ب        | Σ               | <      | 8            | ပ        | ٥         | ш          | I.         | ۰        | <b>∑</b>   | ⋖        | œ      | ပ          | ۵                                                                                   | w      | I          | _            | Σ           | <           |

|    | Š<br>Ž          | Š<br>V | <b>≥</b> | <b>≥</b> | Ş<br>Ş   | Š<br>Ž        | <b>Ş</b> | <b>≥</b>   | ADD  | ADD      | ADD        | ADD        | ADD      | ADD      | ADD           | ADD    | ADC      | ADC     | ADC  | ADC.     | Apc            | ADC      | ₽<br>Q          | ADC    | SUB          | SUB      | SUB       | SUB        | SUB        | SUB      | SUB        | SUB      | SBB    | <b>SBB</b> | <b>888</b>                                                                          | SBB    | <b>SBB</b> | SBB          | SBB         | SBB         |

|    | 78              | 20     | <b>*</b> | 78       | 2        | 2             | <b>H</b> | 7F         | 80   | 18       | 82         | 83         | 84       | 85       | 98            | 87     | 88       | 88      | 8    | 88       | ပ္ဆ            | 8D       | 8E              | 8F     | 8            | 9        | 95        | 93         | 9          | S        | 8          | 97       | 98     | 66         | <b>∀</b> 6                                                                          | 98     | င္တ        | 6            | 96          | 5           |

|    |                 |        | _        |          |          |               | _        |            |      |          |            |            |          |          | _             |        |          |         |      |          |                |          | _               |        |              |          |           |            |            |          |            |          |        |            | _                                                                                   |        | _          |              |             |             |

|    |                 |        |          |          |          |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            |          |            |          |        |            |                                                                                     |        |            | M.L          |             |             |

|    | Ş<br>X          | Q i    | 2        | Q<br>N   | \$       | Q !           | <b>S</b> | Š          | Š    | Š        | Ó<br>M     | Ó          | Ø        | Θ<br>Q   | Ó             | Ý      | Ó<br>M   | ğ       | Š    | Ó<br>N   | Š              | Ó<br>Ž   | Š               | Š      | Š            | §        | Ó<br>M    | Š          | <b>§</b> : | 2        | <b>S</b> : | 2        | Q :    | Q :        | Š                                                                                   | Š      | S :        | <b>Q</b>     | =           | <b>∑</b> .  |

|    | 8               | 5      | 25       | 23       | 3        | S             | 9        | 21         | 28   | 29       | <b>2</b> A | <b>2B</b>  | ၁၄       | 20       | 2E            | 55     | 90       | 61      | 62   | 63       | 64             | 65       | 99              | 67     | 89           | 69       | <b>6A</b> | <b>6B</b>  | ပ္မွ ဖ     | 3 9      | מ מ        | P !      | 2 ;    | <b>7</b>   | 7.5                                                                                 | 73     | 7          | 25 5         | 9 1         | ž           |

|    |                 |        | ₹.       | _        |          |               | <b>8</b> |            | 1    | P.D16    | Adr        | <u>م</u>   | -        | _        | 8Q'\          |        |          | م.      | ₽ď   | <u>م</u> | _              | _        | . D8            | 1      | <b>8</b> 9.  | o i      | a.        | w :        | I.         | : ب      | Σ. •       | ξ (      | n (    | ې د        | ָי בָּ                                                                              | щ :    | Į,         | ָרָר<br>מיני | Σ.          | <u>&lt;</u> |

|    |                 | _      |          |          |          |               | _        |            |      |          |            |            | _        | _        | _             |        |          |         |      |          | •              | -        |                 |        | _            | _        | _         |            |            |          |            | _ `      | -      | _          |                                                                                     | _      | _          |              | _           | _           |

|    |                 |        |          |          |          |               |          | _          |      | _        |            | _          |          | _        |               | -      |          |         |      | _        |                |          | _               |        |              |          |           |            |            |          | _          |          |        | _          |                                                                                     |        |            | 5 i          | _           |             |

| •  |                 |        |          |          |          |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            |          |            |          |        |            |                                                                                     |        |            |              |             | T           |

|    |                 |        |          |          |          |               |          |            |      |          |            |            |          |          |               |        |          |         |      |          |                |          |                 |        |              |          |           |            |            |          |            |          |        |            |                                                                                     |        |            | 2            |             |             |

| 9  | <u>}</u>        | 3      | X >      | ¥ (      |          | 3             | ¥ ā      | ו          | : 6  | Q¥0      | LDAX       | SCX        | Z<br>Z   | E CH     | > \<br>\<br>\ | RHC    | :        | Ž       | STAX | ×        | H C            | 3        | Ž ;             | ¥<br>¥ | : 6          | Q ?      | LOAX<br>S | Š          | 2 2        | 3        |            |          | 2      | 3 3        | ֭֡֝֜֝֜֜֜֜֜֜֓֓֓֓֜֜֜֜֓֓֓֓֓֜֜֜֓֓֓֓֓֡֓֜֜֜֜֓֓֡֓֜֜֡֓֡֓֜֜֡֓֡֓֡֓֡֡֡֡֓֡֓֡֓֡֡֡֡֡֓֡֡֡֡֡֓֡֡֡֡֡֡ | ¥ 2    | 2 2        | 3 3          |             | {           |

| 8  | 3 8             | 5 8    | 3 8      | 3 3      | 3 8      | 3 8           | 2 8      | 3 8        | 8 8  | <b>9</b> | <b>∀</b>   | 8          | ႘        | 9        | 9             | 9.     | 2        | =       | 2 :  | 5        | 4 1            | <u>.</u> | ! م             | 2 9    | <b>20</b> (  | 2 ;      | ٧ (       | 2 9        | ָבַ בַ     | ñ        | ññ         | : 8      | ;      | • ?        | 3 6                                                                                 | 3 2    | <b>5</b> 7 | 0 %          | 9 6         | j           |

<del>.....</del>

...

D16 = constant, or logical/arithmetic expression that evaluates to a 16 bit data quantity.

D8 = constant, or logical/arithmetic expression that evaluates

to an 8 bit data quantity.

Adr = 16 bit address

Processor Technology Corp. 6200 Hollis Emeryville, Ca. 94608 (415) 652-8105

APPENDIX II

#### CORRECTIONS - 2KRO AND 4KRA

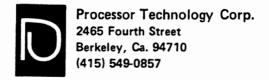

In an effort to make our devices completely pin-compatible with the original manufacturer's equipment, a design error of the original equipment was incorporated into the design of our cards. The signal which is driving pin 72, PRDY, should instead be driving pin 3, XRDY; Method 2. This correction may be accomplished using one of two methods (BUT NOT BOTH).

#### MASTER BOARD CORRECTION - METHOD 1

- ( ) Locate the cable wire going to point 72 on the Mother Board within the computer.

- ( ) Remove the wire from point 72 and solder into point 3 on the Mother Board.

#### PROCESSOR TECHNOLOGY BOARD CORRECTION - METHOD 2

To correct this, refer to the enclosed diagram and perform the following modifications:

- ( ) Locate pin 72 on the back side of the board. Cut the trace between this pin and the feed-through hole above it.

- ( ) Cut a piece of solid insulated wire, 24 gauge or smaller, long enough to reach from this feed-through to pin 3.

- ( ) Strip one end of this wire to a length of 1/8 inch and tin it. Solder this end from the top side of the card to the feed-through hole.

- ( ) Strip the other end of the wire to a length of 1/16 inch and tin it.

- ( ) Bending the wire so that it will lie close to the card, position this end so that it will lie in contact with the rounded end of pin 3.

- ( ) Using very little solder and taking care to avoid spreading solder too far down the pin, tin a small area at the rounded end of pin 3.

- ( ) Place the wire end in contact with this tinned area of pin 3 and heat the two with the soldering iron until the solder melts. Remove the iron and allow the solder to solidify while holding the wire steady.

NOTE: When soldering to gold-plated printed-circuit connector contacts it is essential that the soldering iron not make contact with any area which will enter the connector. Solder coatings cannot be removed from gold and defeat the purpose of the gold plating, which is to prevent oxidation of contacts.

On the device schematic diagram, change pin 72, PRDY to pin 3, XRDY.

Processor Technology Corp. 2465 Fourth Street Berkeley, Ca. 94710 (415) 549-0857

# **Technical Bulletin**

#### **PROBLEM**

The unpredictability of power failure in a volatile memory system can result in a loss of irreplaceable information. Hours of work, as represented by a nicely debugged program, can be wiped out in an instant with a power failure lasting only long enough for the lights to blink.

#### SOLUTION

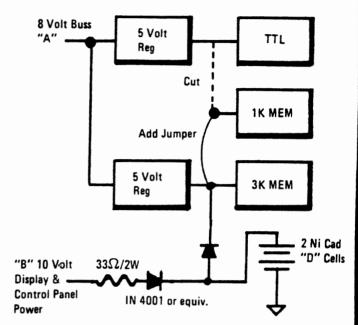

The simple modification described in this bulletin can prevent the loss of stored data during loss-of-power and power interrupt conditions. This is accomplished with the use of low-power 91L02A Memory I.C.'s provided with the Processor Technology 4KRA. These I.C.'s will operate in a low power stand-by mode which further reduces energy requirements.

In the stand-by mode, the memory supply power is reduced to approximately 2 volts, which is provided by a storage battery. The battery is continuously charged during normal operation at a 10 to 30 hour rate from the CPU Display and Control Panel Supply, and automatically changes to the standby mode when normal power is interrupted or removed.

Data integrity will be retained as long as the stand-by power is available; each 4K memory card consumes slightly over one watt of power. If a 4 Amp Hr battery is used, it will provide from five to ten hours of stand-by power. This time can be extended by the use of a battery with greater storage capacity.

Retaining data with stand-by power will be useless if, when power is restored to the CPU, a random operation rewrites retained data improperly. This problem is solved by using an initializing circuit to set the memory "protect" mode. This is accomplished with an RC network: Parallel a .1 Mfd disc capacitor with a 10K resistor. Ground one end and connect the other end to pin 10 of IC 41. Refer to Figures 2 and 3.

NOTE: If some applications require a "non-protect" initializing, this can be accomplished by connecting the same network to pin 4 instead of pin 10 of IC 41. A simple switch could be used to implement mode selection from "protect" to "non-protect" power-up initialization.

#### **LIMITATIONS**

The battery backup supply described in this bulletin is not by itself adequate for complete power-fail protection. When battery backup is used, the 4KRA memory modules will retain data correctly only if the computer is in the stopped condition. For complete power-fail protection, a priority interrupt to the processor is necessary, along with suitable software routines for storing the CPU status in non-volatile memory and appropriate circuitry for fast detection of actual power failure. A comprehensive discussion of power fail-restart interrupt operation is beyond the scope of this bulletin.

Figure 1

PROCESSOR TECHNOLOGY CORP.

6200 Hollis. Emeryville, California 94608