## **DC5 Design Description**

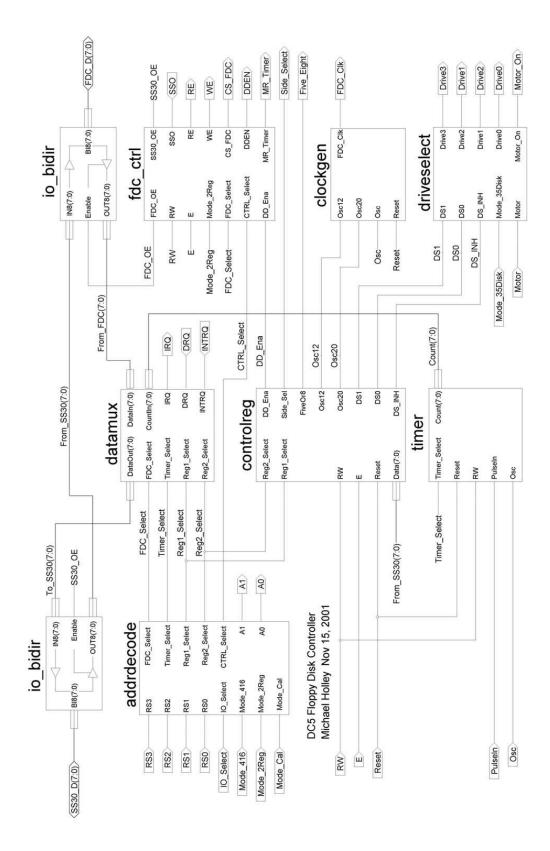

The two major components in the DC5 are U1, the WD2797 Floppy Disk Controller, and U2, the Xilinx XC9572 programmable logic device. The operation of the WD2797 is provided in a separate data sheet. The operation of the XC9572 is given below.

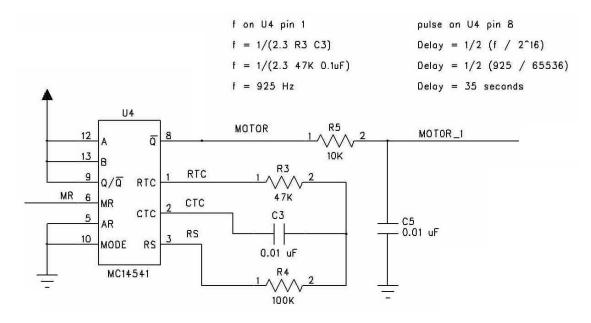

The motor run timer is triggered (U4 pin 6) whenever the WD2797 FDC is accessed (8018-801B or E018-E01B). The motor will run for about 30 seconds after the last access. The time is controlled by the values of R3, R4 and C3. See the MC14541 data sheet for details on adjusting the time. The output of this timer is also used for the Ready signal in the "00" setting of J5. The motor control is from U4 pin 8 while R5 and C5 provide a delay for the Ready signal.

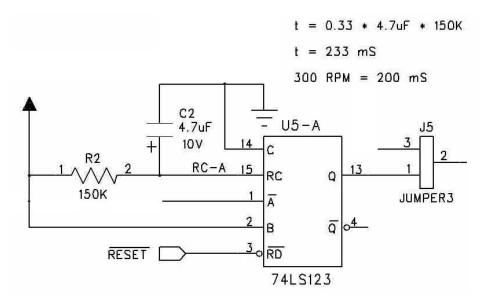

The index pulse detector is triggered (U5 pin 1) by the IP signal from the floppy drive. At 300 RPM this pulse occurs every 200 ms. The detector is set at 233 ms and its output will be high as long as the disk is spinning. (Newer 3.5 inch drives mask the IP signal when the drive is changing tracks and the output of U5A will go low.) The output of U5A is use in the "09" setting of J5.

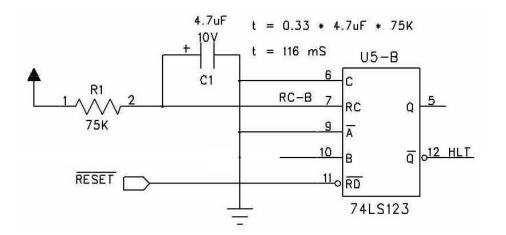

The head load timer is triggered (U5 pin 10) when the HLD signal from U1 goes high. The output on U5 pin 12 goes low for about 100 ms then stays high. This is connected to the HLT pin on U1. The head load feature is for 8-inch disk drives and this circuit satisfies the delay required by the WD2797 FDC.

The pull-up resistors R8, R9, R10 and R11 are 150 ohms as specified in for the original 5.25 floppy drives. These can be replaced with 330 ohms or 1000 ohms resistors if desired. Current production drives use 1000 ohms pull-up resistors but work with 150 ohms.

The output buffers U7 and U8 are 74LS06 open-collector inverters that could be replaced with 74LS04 or 74HC04 inverters. The floppy drives are designed for open-collector parts but many new designs use a standard inverter.

C15 is an optional 100 pf capacitor that was used on many SWTPC designs. It is not required.

The voltage regulators in the lower right hand corner are only used with the FD1771 chip.

The capacitor C6 is mislabeled on the silk screen as C5. C6 is above U1, WD2797, and to the left of R6. The real C5 is next to R5.

The optional jumper to the left of the U9 is to disable the output of the oscillator. This is not required.

The XC9572 design is described in the Verilog hardware description language. It is similar to the "C" programming language and the ABEL PLD language. A complete language description is provided with the Xilinx design software.

# XC9572 Design Description

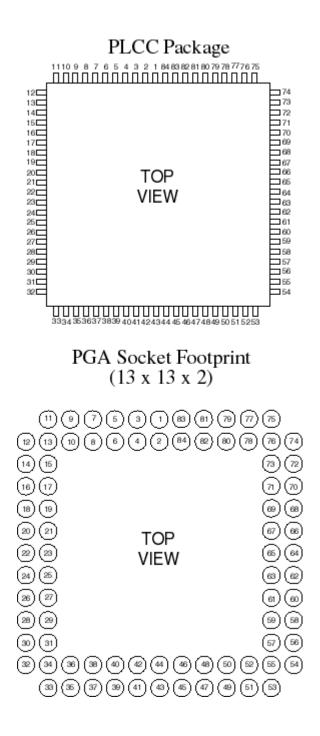

|                                                                                                                                                                                           | F<br>D<br>C<br>-D<br>-<br>0<br>>                                                                                                                                                             | A<br>1 | M<br>o<br>t<br>o<br>r | G<br>N<br>D      | F D C _ D < 1 >    | F D C   D < 2 > | F D C   D < 3 >  | FDC  D < 4 >     | F D C  D < 5 >   | FDC  D < 6 > | F D C   D < 7 >  | P<br>G<br>N<br>D | I<br>N<br>T<br>Q                | P<br>G<br>N<br>D | D<br>R<br>Q | P<br>G<br>N<br>D | D<br>D<br>E<br>N | V<br>C<br>C      | M<br>R<br>T<br>i<br>m<br>e<br>r | P<br>u<br>l<br>s<br>e<br>I<br>n | Five<br>Eight                                                                                                                          |                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|------------------|--------------------|-----------------|------------------|------------------|------------------|--------------|------------------|------------------|---------------------------------|------------------|-------------|------------------|------------------|------------------|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Osc<br>RE<br>CS_FDC<br>WE<br>GND<br>A0<br>Mode_416<br>PGND<br>Mode_35Disk<br>Mode_22Reg<br>VCC<br>PGND<br>Mode_Cal<br>PGND<br>GND<br>GND<br>TDI<br>TDI<br>TMS<br>TCK<br>PGND<br>IO_Select | /111<br>  12<br>  13<br>  14<br>  15<br>  16<br>  17<br>  18<br>  19<br>  20<br>  21<br>  22<br>  23<br>  24<br>  25<br>  26<br>  27<br>  28<br>  29<br>  30<br>  31<br>  32<br>  33<br>  32 |        |                       | 36               | 37                 | 38              | 39               | 40               |                  | 2<br>C95     |                  | 15-1             | PC8                             | 1                |             |                  |                  |                  |                                 |                                 | 75<br>74<br>73<br>72<br>71<br>70<br>69<br>68<br>67<br>66<br>63<br>62<br>61<br>60<br>59<br>58<br>57<br>56<br>55<br>55<br>55<br>54<br>53 | Reset<br>VCC<br>FDC_C1k<br>PGND<br>SSO<br>PGND<br>Drive1<br>PGND<br>Drive0<br>PGND<br>VCC<br>PGND<br>Drive3<br>PGND<br>GND<br>TDO<br>Drive2<br>PGND<br>Motor_On<br>IRQ<br>Side_Select |

|                                                                                                                                                                                           | R<br>W                                                                                                                                                                                       | E      | S<br>S<br>3<br>0      | S<br>S<br>3<br>0 | S<br>S<br>3<br>0   | V<br>C<br>C     | S<br>S<br>3<br>0 | S<br>S<br>3<br>0 | S<br>S<br>3<br>0 | G<br>N<br>D  | S<br>S<br>3<br>0 | P<br>G<br>N<br>D | S<br>S<br>3<br>0                | P<br>G<br>N<br>D | R<br>S<br>O | R<br>S<br>1      | G<br>N<br>D      | P<br>G<br>N<br>D | R<br>S<br>3                     | P<br>G<br>N<br>D                | R<br>S<br>2                                                                                                                            |                                                                                                                                                                                       |

|                                                                                                                                                                                           |                                                                                                                                                                                              |        | _<br><<br>7<br>>      | D<br>< 6<br>>    | _<br>D<br>< 5<br>> |                 | <br>< 4<br>>     | _<br><<br>3<br>> | _<br><br>        |              | <br>< 1<br>>     |                  | _<br>_<br>_<br>_<br>_<br>_<br>_ |                  |             |                  |                  |                  |                                 |                                 |                                                                                                                                        |                                                                                                                                                                                       |

This footprint is from Emulation Technology, Inc. http://www.emulation.com/footprints/84-PCC5.gif

# **Address Decoding**

The original SWPTC 6800 systems had I/O slots with 4 address locations. The DC1 floppy disk controller plugged into slot 6 (8018 to 801B) but it needed 5 address locations. To do this you had to jumper the adjacent I/O select (slot 5 – 8014 to 8017) to the UD3 line. The SWTPC 6809 systems mapped slot 6 to E018 to E01B and mapped slot 5 to E014 to E017.

The SWTPC 6809 systems could be configured with 16 address locations for each I/O slot. The UD3 and UD2 lines became the RS2 and RS3 lines. Because 6809 systems could have 4 or 16 address I/O slots the DC3 and DC4 floppy disk controllers had a 4 or 16 address jumper. In the 16-address location mode the card in I/O slot 1.

This card emulates this with the Mode\_416 control pin. When this pin is high (SW1 position 3 OFF) the address decoding uses RS3 and RS2 as address lines. When the pin is low, RS2 is treated as an I/O select.

The 8014 to 8017 (E014 to E017) address range is used to write to the drive select control register and read the INTRQ and DRQ status. The 8018 to 801B (E018 to E01B) address range is used to read and write the WD2797 FDC chip (or calibration counter/timer).

```

module AddrDecode(RS3,RS2,RS1,RS0,IO Select,Mode 416,Mode 2Reg,Mode Cal,

FDC_Select, CTRL_Select, Reg1_Select, Reg2_Select, Timer_Select, A1,A0);

input RS3, RS2, RS1, RS0;

input IO_Select;

input Mode 416, Mode 2Reg, Mode Cal;

output FDC_Select, CTRL_Select;

output Reg1 Select, Reg2 Select, Timer Select;

output A1, A0;

wire E018 B, E014 7;

wire E014, E015, E016, E017;

assign E018_B = Mode_416 & ~IO_Select & RS3 & ~RS2

~Mode_416 & ~IO_Select;

assign E014_7 = Mode_416 & ~IO_Select & ~RS3 & RS2

| ~Mode 416 & ~RS2;

assign E014 = Mode 416 & ~IO Select & ~RS3 & RS2 & ~RS1 & ~RS0

~Mode_416 & ~RS2

& ~RS1 & ~RS0;

assign E015 = Mode_416 & ~IO_Select & ~RS3 & RS2 & ~RS1 & RS0

/ ~Mode 416 & ~RS2

& ~RS1 & RS0;

assign E016 = Mode_416 & ~IO_Select & ~RS3 & RS2 & RS1 & ~RS0

~Mode 416 & ~RS2

& RS1 & ~RS0;

assign E017

= Mode_416 & ~IO_Select & ~RS3 & RS2 & RS1 & RS0

| ~Mode_416 & ~RS2

& RS1 & RS0:

// Outputs

assign CTRL Select = E014 7 | Timer Select;

assign FDC Select

= E018 B & (Mode Cal == 1'b1);

assign Timer_Select = E018_B & (Mode_Cal == 1'b0);

assign Reg1 Select = (Mode_2Reg == 1'b1) & E014_7 |

(Mode_2Reg == 1'b0) & (E014 | E015);

assign Reg2 Select = (Mode 2Reg == 1'b0) & (E016 | E017);

assign A1 = RS1;

assign A0 = RS0;

endmodule

```

# **Control Registers**

The SWTPC floppy disk controllers had one control register that selected the disk drive. It was located at I/O address 8014 on the 6800 systems and E014 on the 6809 systems. This register was not decoded to a single address; it used 4 address from E014 to E017 (8014 to 8017). Most FLEX software used just the single address so an additional control register can be added at E016-E017 (8016-8017).

The Mode 2Reg pin enables this second register. When the pin is low (SW1 position 2 ON) REG1 is at E014-E015 (8014-8015) and REG2 is at E016-E017 (8016-8017). When the pin is low REG1 is at E014 to E017 (8014 to 8017).

| Control Register 1 |          |        |         |       |       |       |      |  |  |  |

|--------------------|----------|--------|---------|-------|-------|-------|------|--|--|--|

| Bit 7              | Bit 6    | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit0 |  |  |  |

| DS_INH             | Side_Sel | Х      | Х       | х     | х     | DS1   | DS0  |  |  |  |

|                    |          |        |         |       |       |       |      |  |  |  |

| Control Register 2 |          |        |         |       |       |       |      |  |  |  |

| Bit 7              | Bit 6    | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit0 |  |  |  |

| Х                  | Х        | DD Ena | FiveOr8 | Osc20 | Osc12 | Х     | Х    |  |  |  |

The bits Osc20 and Osc12 control the clock divider circuit. The FiveOr8 is connected to the WD2797 5/8 pin.

```

module ControlReg(Reg1_Select, Reg2_Select, RW, E, Data, Reset,DS_INH,

Side Sel, DD Ena, FiveOr8, Osc20, Osc12, DS1, DS0);

input Req1 Select, Req2 Select;

input RW, E;

input

[7:0] Data;

input Reset;

output DS INH, Side Sel, DS1, DS0;

output DD Ena , FiveOr8, Osc20, Osc12;

wire Clk1, Clk2;

reg DS INH, Side Sel, DS1, DS0;

reg DD Ena , FiveOr8, Osc20, Osc12;

// Control Register 1

assign Clk1 = Reg1 Select & ~RW & ~E;

always @(posedge Clk1 or negedge Reset) begin

if(Reset == 'b0)

{DS INH,Side Sel,DS1,DS0} = 4'b0000;

else

\{DS INH, Side Sel, DS1, DS0\} = \{Data[7], Data[6], Data[1], Data[0]\};

end

// Control Register 2

assign Clk2 = Reg2 Select & ~RW & ~E;

always @(posedge Clk2 or negedge Reset) begin

if(Reset == 'b0)

{DD Ena, FiveOr8, Osc20, Osc12} = 4'b0000;

else

{DD Ena,FiveOr8,Osc20,Osc12} = {Data[5],Data[4],Data[3],Data[2]};

end

endmodule

```

#### **Data Multiplexer**

The FDC data and the INTRQ / DRQ status lines are multiplexed onto the SS30 data bus. During the read cycle when RW is high and the address is between E014 and E01B (8014 and 801B) the buffers to SS30 data bus are enabled. The FDC data is present except when the address is between E014 and E017 (8014 and 8017).

The SS30 data bus to routed to the FDC data pins. The buffers to the FDC are tri-state except when RW is low and the address is between E018 and E01B (8018 to 801B.)

Normally the status of DRQ and INTRQ are read between locations E014 and E017 (8014 and 8017). When in the 2-register mode, the design version number will be read at E016 and E017 (8016 and 8017). Revision 1 was only at E016 (8016)

When in the calibration mode the Counter/Timer is read instead of the FDC chip.

```

module DataMux (DataIn, CountIn, DRQ, INTRQ,

FDC_Select, Reg1_Select, Reg2_Select, Timer_Select,

IRQ, DataOut);

input [7:0] DataIn;

input [7:0] CountIn;

input DRQ;

input INTRQ;

input FDC Select, Timer Select, Req2 Select, Req1 Select;

output IRQ;

req IRQ;

output [7:0] DataOut;

reg [7:0] DataOut;

always @(FDC Select or Timer Select or Reg2 Select or

DataIn or CountIn or DRQ or INTRQ) // synthesis parallel case

begin

if (FDC Select)

DataOut = DataIn;

else if (Timer Select)

DataOut = CountIn;

else if (Reg2_Select)

DataOut = 8'b00000010; // Version

else // Reg1 Select

DataOut = \{DRO, INTRO, 6'b000000\};

end

// Emulate open drain signal for SS-30 bus

always @(DRQ) begin

if (~DRQ)

IRQ = 1'b0;

else

IRQ = 1'bz;

end

endmodule

```

## WD2797 Interface

This module generates the active low WE, RE and CS for the WD2797as well as the Bi-directional buffer control signals. The Motor Run timer (MR\_Timer) is pulsed whenever the WD2797 is accessed. The DDEN is an inverted SSO when in the default SWTPC mode. When in the 2 register mod it is controlled by a register bit.

module FDC\_Ctrl(E,RW,FDC\_Select,CTRL\_Select,Mode\_2Reg,DD\_Ena,SSO, MR Timer, WE, RE, CS FDC, DDEN, FDC OE, SS30 OE); input E, RW, FDC Select, CTRL Select, Mode 2Reg, DD Ena, SSO; output MR\_Timer, WE, RE, CS\_FDC, DDEN, FDC\_OE, SS30\_OE; assign MR Timer = FDC Select; assign DDEN = (Mode 2Reg == 1'b0) ? ~DD Ena : ~SSO; assign WE = ~(E & ~RW & FDC Select); assiqn RE  $= \sim (E \& RW \& FDC Select);$ assign CS FDC = ~FDC Select; assign FDC OE = FDC Select & ~RW; assign SS30 OE = (FDC Select | CTRL Select) & RW & E; endmodule

## **Disk Drive Outputs**

The motor starts when the FDC accessed. Reading or writing the addresses E018 to E10B (8018 to 801B) resets the timer. The motor runs for over 30 seconds and the timer is reset after each access.

The control register determines which floppy drive is selected. The select is only active if the motor is on or the DS\_ENA bit is high. The Side\_Sel bit is for double-sided drives.

The Drive0, Drive1, Drive2, Drive3 and Side\_Select outputs are acitve low. The MR\_Timer is active high and connects to pin 6 (MR) of the MC14541 timer.

New 3.5 inch drives are all hard wired to Drive 1 and need an IBM PC twisted cable as follows:

| Pin | IBM PC         | SWTPC and standard drives |

|-----|----------------|---------------------------|

| 10  | Motor Enable A | Drive Select 0            |

| 12  | Drive Select B | Drive Select 1            |

| 14  | Drive Select A | Drive Select 2            |

| 16  | Motor Enable B | Motor Enable all drives   |

Note: Drive A is after twist at the end of the cable.

```

module DriveSelect(DS1, DS0, DS INH, Motor, Mode 35Disk,

Drive3, Drive2, Drive1, Drive0, Motor On);

input DS1, DS0;

input DS INH, Motor, Mode 35Disk;

output Drive3, Drive2, Drive1, Drive0;

output Motor On;

reg Drive2, Drive0;

always @(Mode 35Disk or Motor or DS1 or DS0 or DS INH)

// synthesis parallel case

begin

if (Mode 35Disk == 1'b0) // Switch 3 ON - Logic Low

begin

Drive0 = Motor;

// Motor

Drive2 = ~DS1 & ~DS0 & ~DS INH & Motor; // Drive 0

end

else

begin

Drive0 = ~DS1 & ~DS0 & ~DS INH & Motor; // Drive 0

Drive2 = DS1 & ~DS0 & ~DS INH & Motor; // Drive 2

end

end

assign Drive1 = ~DS1 & DS0 & ~DS INH & Motor; // Drive 1

assign Drive3 = DS1 & DS0 & ~DS INH & Motor; // Drive 3

assign Motor On = Motor;

endmodule

```

#### **FDC Clock Circuit**

The FDC clock is derived from a 12 MHz external oscillator. The standard 5.25 inch floppy requires 1.0 MHz, the 3.5 inch floppy drive requires 1.2 MHz and the 8 inch floppy drive requires 2.0 MHz. Osc20 is bit 3 (^h08) of Reg2 and Osc12 is bit 2 (^h04). Note: Xilinx App Note 104 recommends disconnecting all clocks during programming the CPLD

This is implemented by a programmable divider (3,5 or 6) followed by a divide by 2 to give a 50% duty cycle.

| Osc12 | Osc20 | Divide by | Frequency  |

|-------|-------|-----------|------------|

| 0     | 0     | 12        | 1.0 MHz    |

| 1     | 0     | 10        | 1.2 MHz    |

| 0     | 1     | 6         | 2.0 MHz    |

| 1     | 1     | Х         | Don't Care |

```

module ClockGen(Osc12,Osc20,Osc,Reset,FDC Clk);

input Osc12, Osc20, Osc, Reset;

output FDC Clk;

reg [2:0] Q; // programmable divider

req Q3;

// divide by 2

always@(posedge Osc or negedge Reset)

begin

if(~Reset)

begin

Q = 3'b000;

Q3 = 1'b0;

end

else if(Osc20 && Q == 3'b010) // Divide by 3 (0 to 2)

begin

Q = 3'b000;

Q3 = ~Q3;

end

else if(Osc12 && Q == 3'b100) // Divide by 5 (0 to 4)

beqin

Q = 3'b000;

Q3 = ~Q3;

end

else if(~Osc12 && Q == 3'b101) // Divide by 6 (0 to 5)

begin

Q = 3'b000;

Q3 = ~Q3;

end

else

Q = Q + 1;

end

assign FDC Clk = Q3;

endmodule

```

#### **Counter/Timer**

The input signal, PulseIn, is synchronized to the 12 MHz clock. The new signal, Pulse, is the trigger for the state machine. When Pulse goes low the state machine advances to state Wait\_2. This resets the count. When Pulse goes high the counting starts and runs until Pulse goes low. The value in the counter is held until there is a write to Timer\_Select address.

```

module Timer(Osc,Timer Select,RW,PulseIn,Reset,Count);

input Osc, Timer Select, RW, PulseIn, Reset;

output [7:0] Count;

reg [7:0] Count;

reg Pulse;

// State Register

reg [2:0] current_state /* synthesis state_machine */;

reg [2:0] next_state;

// Define States

Wait_1 = 3'b000,

Wait_2 = 3'b001,

parameter Wait 1

Counting = 3'b010,

= 3'b100;

Done

always @(Pulse or Timer_Select or RW or current_state)

begin

case(current_state)

Wait 1:

if(~Pulse)

next state = Wait 2;

Wait 2:

if(Pulse)

next_state = Counting;

Counting:

if(~Pulse)

next state = Done;

Done:

if (Timer Select & ~RW) next state = Wait 1;

endcase

end

always @ (posedge Osc or negedge Reset) // State Machine Registers

begin

if (~Reset)

begin

current state = Wait 1;

Pulse = 0;

end

else

begin

current state = next state;

Pulse = PulseIn; // Sync to common clock

end

end

always@(posedge Osc) // Counter Registers

begin

if(current state == Wait 2)

Count = 8'b000000;

else if(current state == Counting)

Count = Count + 1;

end

endmodule

```