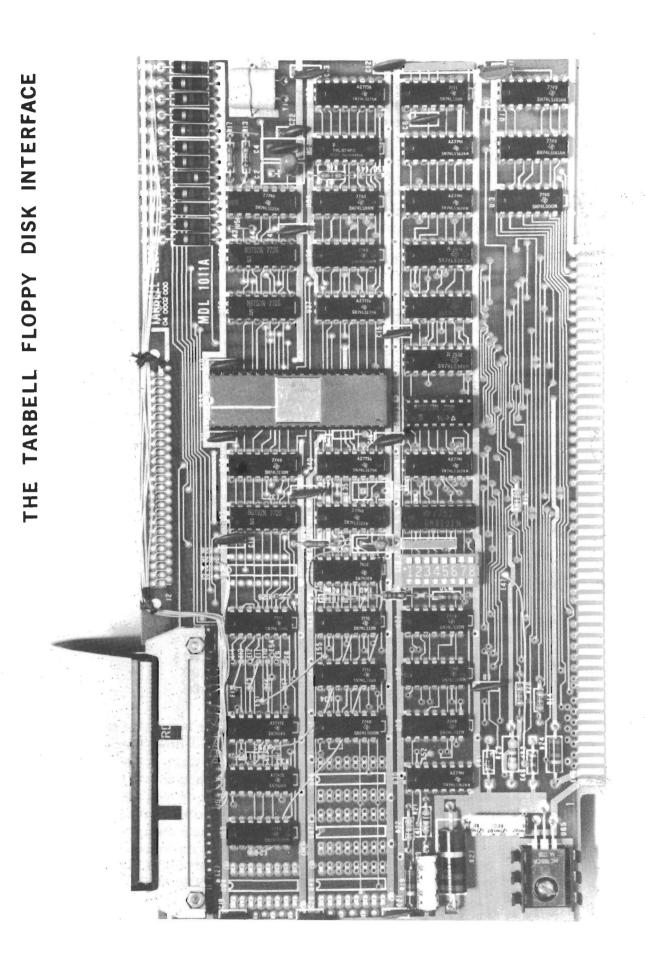

# The Tarbell Floppy Disk Interface

(213) 538-4251

(213) 538-2254

# This Document was scanned and contributed by:

Barry A. Watzman

20620 South Leapwood Avenue, Suite P Carson, California 90746

(213) 538-4251 (213) 538-2254

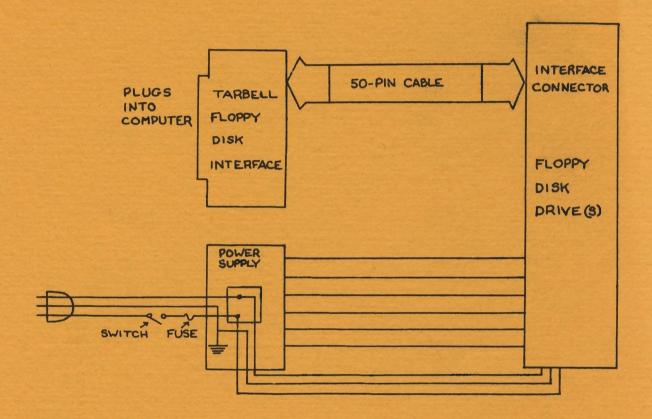

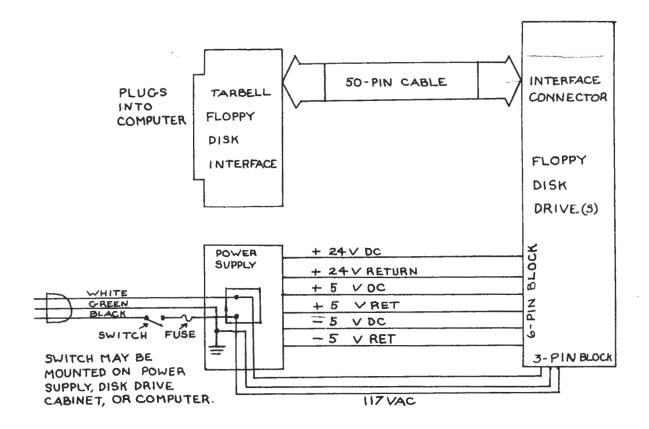

The Tarbell Floppy Disk Interface is a programmed-data-transfer (not DMA) device. It plugs into your IMSAI or ALTAIR\* computer, and is designed to work with a variety of standard-size floppy disk drives. It includes a 32-byte ROM bootstrap program, which is automatically enabled when the computer RESET button is pushed, and which switches itself out after the bootstrap has run. In this way, no part of your memory needs to be dedicated to Read-Only-Memory (ROM). The interface runs at the standard speed of 250,000 bits per second, and the normal formatted capacity per diskette is 256 kilobytes. Places for two connectors are provided on the board. One 50-pin header connector and a cable with the mating connector are provided with the interface kit. The drive end of the cable has no connector, but a 50-pin edge connector may be added for \$10.00. There are four extra IC slots to allow you to do your own thing, and the connector pins come out to jumper pads, so you can adapt to different drives. The manual has the connections detailed for popular drives. An on-board dip-switch is used to select the device address, disable the bootstrap, and write-protect. Circuitry is included to run up to four drives, and eight can be accessed by using the spare IC slots.

The Tarbell Floppy Disk Interface and other related items can be bought in pieces, so that it's not necessary to make a single large outlay of cash. Because of this policy, the 6-month warranty will be limited to only those items traceable to Tarbell Electronics. Notice that we are offering the CP/M floppy disk operating system, which is described on another page. An owner's manual for the interface is included with the kit or the bare board, and is also available separately.

| Floppy Disk Interface Kit<br>CP/M Operating System (on disk)<br>CP/M System Manual Set (6)<br>BASIC-E Compiler Manual<br>GSI 110 Floppy Disk Drive<br>Power Supply for 1 GSI 110                                                                                                                                                                                          | 190.00<br>70.00<br>25.00<br>5.00<br>525.00<br>75.00                                                | NOTE: These prices are<br>subject to change without<br>notice. There are no discount    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Floppy Disk Interface Manual Bare Floppy Disk Interface Board Kit with all parts except 1771 Western Digital 1771 FDC IC Assembled Floppy Disk Interface PerSci 270 Dual Floppy Disk Drive Power Supply for PerSci 270 Blank Formatted Diskette BASIC-E Source Listing (PL/M) Additional Charge for Special Cable Package of IC Sockets (35) CBASIC on disk CBASIC manual | 5.00<br>40.00<br>150.00<br>60.00<br>265.00<br>1295.00<br>10.00<br>15.00<br>10.00<br>10.00<br>85.00 | for complete systems; just add the prices together to find the total for your purchase. |

Since Tarbell Electronics does not wish to get into the business of selling complete systems, we encourage you to buy your system, including the floppy disk drive, from your local dealer. If you add up the prices of the first six items, however, you can see that a complete floppy disk system including software and hardware can be had for less than a thousand dollars. Note that the Tarbell Floppy Disk Interface is not designed to work with double-density or mini-floppys, although it will work with multiple and double-sided drives. The drives that it has worked with so far include the Shugart 800/801, the Innovex 410, the Innovex 220 (modified by a jumper change), the GSI 110, the CDC 803, and the PerSci 270, the PerSci 70, the Wangco/Orbis 76, the Pertec 400, and the Calcomp 140. The on-board bootstrap may not work reliably with some Z-80 CPU's and some dynamic memories. Ask your local dealer about possible conflicts, as it may be necessary to use ROM on another board.

The first deliveries were made July 2, 1977. Delivery from the factory is 3-4 weeks after receiving your order, and individuals must send cash in advance. For faster delivery, check with your local dealer.

<sup>\*</sup> ALTAIR is a trademark/tradename of MITS, Inc.

## CP/M™ BY DIGITAL RESEARCH — A COMPLETE FLOPPY DISK OPERATING SYSTEM FOR THE TARBELL FLOPPY DISK INTERFACE.

The CP/M Disk operating system has been in existence for over two years in various manufacturer's products, and thus has had extensive field testing. It is now being made available to the hobby community. It is licensed software, and copying for other individuals is prohibited. We feel this is justified, as the cost, \$100, is low for such a good system.

The following commands are built in to the operating system:

DIR List all or selected portions of the directory (file list)

TYPE Type the contents of an ASCII file on the console

REN Rename a file to a different name

ERA Erase a file or files from the disk

SAVE Save memory on disk for later load

The following programs are included on the disk, and are invoked just like commands by typing the name:

PIP Peripheral Interchange Program moves files around

SUBMIT Batch processing program for predefined list of commands

ED A really nice, string-oriented text editor

ASM Assembler to convert assembly language to machine code

DDT Dynamic Debugging Tool for memory dumps, loads, traces

LOAD Convert hex file to memory image file

DUMP Dump file in hex onto console

SYSGEN Generates new CP/M systems for backup

BASIC BASIC-E compiler has both sequential and random file access

RUN Run-time interpreter for BASIC-E programs

STAT Prints the amount of disk storage still available and amount used for each file

CPM Generates different sized CP/M systems

COPY Copies from one disk onto another, track by track

TAPELIB Provides extensive disk-to-cassette facilities.

The following source files are included on the disk:

CASDSK Transfers the named file from Tarbell cassette to disk

DSKCAS Transfers the named file from disk to Tarbell cassette

SBOOT Cold-Start loader which is loaded by bootstrap program

CBIOS Customer's Basic Input/Output System includes all drivers

FORMAT Reformats crashed diskettes

COPY Assembly language source for program above

Tarbell Electronics provides the system modified to work with the Tarbell floppy disk interface and a simple console interface, such as a teletype. The console is addressed with port O for status and port 1 for data. Bit O of status low means keyboard ready, and bit 7 of status low means printer ready. It is set up to work in 24 kbytes. The documentation includes a listing of the BIOS, and instructions which will enable you to patch the CBIOS for your own system.

As of March 1, 1978 the CP/M User's Group had 24 diskettes full of software. It costs \$4 to get on the mailing list, and the diskettes are \$8 each.

### DOCUMENTATION:

CP/M FEATURES AND FACILITIES MANUAL

CP/M EDITOR, ASSEMBLER, AND DEBUGGER MANUALS

CP/M INTERFACE GUIDE

CP/M SYSTEM ALTERATION GUIDE

TARBELL CP/M USER'S GUIDE

### **BASIC-E Compiler Description**

This compiler is a public-domain piece of software written by Gordon E. Eubanks, Jr. As provided by Tarbell Electronics, it is meant to work with the CP/M<sup>™</sup> Disk Operating System. With the CP/M, it requires about 20K bytes of main memory. Since it is a compiler, as opposed to an interpreter, it has some advantages: 1) the program will probably run faster than with an interpreter, 2) the program will probably use less memory than with an interpreter. There are also some disadvantages: 1) it is not as easy to develop a program, because editing must be done separately, 2) it cannot be easily used with a cassette, because there are several steps that are not easily and quickly performed by a cassette unit, 3) In this version there is no PEEK or POKE, no PRINT USING, no CALL to machine code programs, and no LPRINT. These are all available in CBASIC, which costs \$100.00.

The following statements are valid in BASIC-E:

FOR, NEXT, FILE, CLOSE, GOSUB, GOTO, INPUT, LET, ON, PRINT, READ, RESTORE, RETURN, RANDOMIZE, OUT, STOP, DATA, DEF, DIM, END, IF, REM, ELSE, THEN.

The following built-in functions are valid in BASIC-E:

ABS, ASC, ATN, CHR\$ COS, COSH, FRE, INP, INT, LEFT\$, LEN, LOG, MID\$, POS, RIGHT\$, RND, SGN, SIN, SINH, STR\$, SQR, TAB, TAN, VAL, EXP.

The following logical connectives are available: AND, EQ, GE, GT, LE, LT, NE, NOT, OR, <, >, =.

There are 26 compiler error messages, and 23 run-time error messages, all of two characters each.

Disk files may be read, written or updated by the BASIC-E program using both sequential and random access. There are blocked and unblocked files. The program can select any disk available to CP/M.

Using the BASIC-E compiler consists of three main steps:

- 1) The source program is created on disk using the Editor.

- 2) The source is compiled by the compiler, which produces an intermediate file.

- 3) The intermediate file is then run by the run-time monitor.

Line numbers need only be used on statements to which control is passed, and do not have to be in ascending order. Using identifiers longer than two characters and indenting statements to enhance readability does not affect the size of the object file created by the compiler. The first 31 characters of identifiers are used by the compiler.

The 40-page manual is available for \$5.00.

The compiler and run-time monitor are included on our CP/M diskette, and are also available separately on a diskette for \$10.00.

The complete listing, which is written mostly in PL/M, is available for \$15.00.

| 1                        | OVERVIEW                                                                                                                                                                                       |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4 | Introducing the Tarbell Floppy Disk Interface<br>Operating Instructions/General Notes<br>Important Cautions<br>Software Support                                                                |

| 2                        | THEORY OF OPERATION                                                                                                                                                                            |

|                          | (helpful to read before assembly or operation but not a necessity)                                                                                                                             |

| 3                        | ASSEMBLING THE INTERFACE BOARD (KIT UNITS)                                                                                                                                                     |

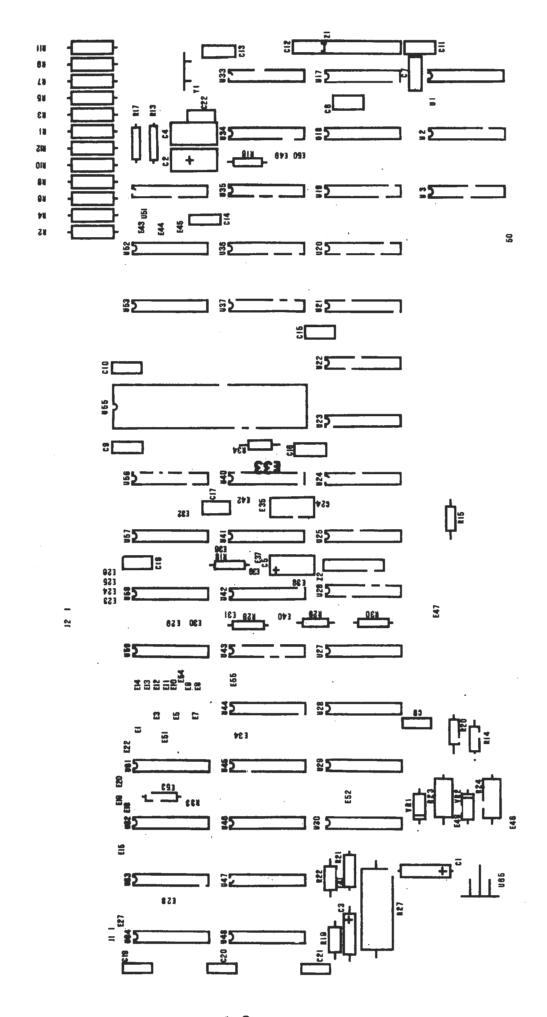

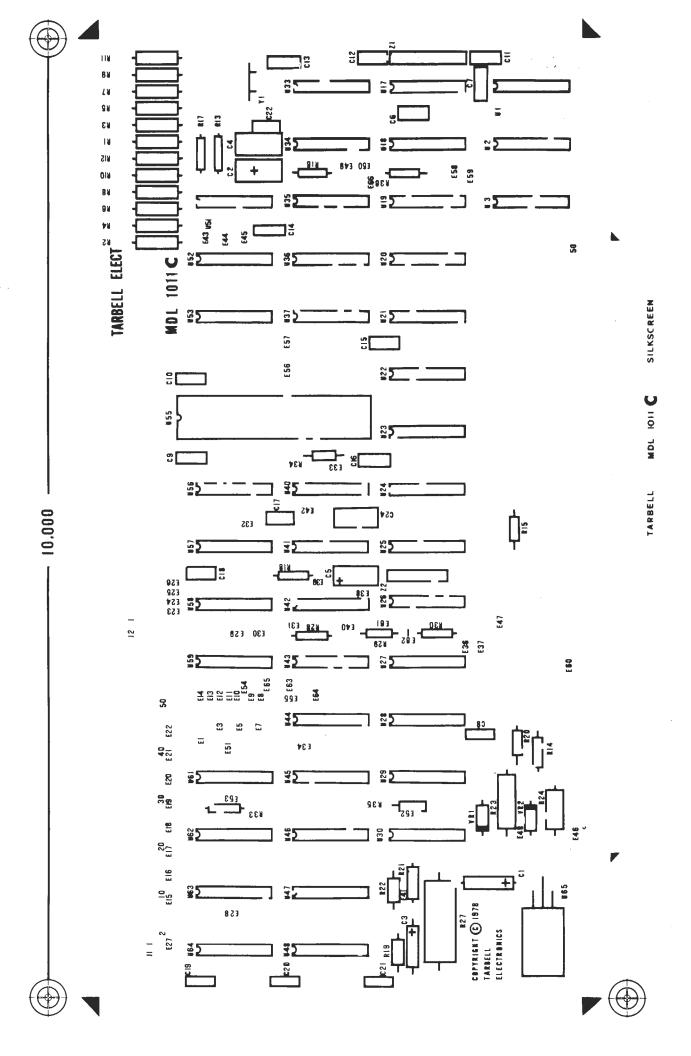

| 3-1<br>3-2<br>3-3        | Parts Drawing Parts List Step-by-step Assembly                                                                                                                                                 |

| 4                        | SETTING THE JUMPERS                                                                                                                                                                            |

| 4-1<br>4-2               | Using the Jumper Pads<br>Jumper Set-Ups for                                                                                                                                                    |

|                          | a) CDC BR803A i) Pertec FD511 b) Innovex 210 j) Calcomp 140 c) Innovex 410 k) Calcomp 143 d) GSI/Siemens l) Pertec FD400 FDD 100-8 & 220-8 m) Memorex 550 e) PerSci 270/277 f) Shugart 800/851 |

| 5                        | CHECKOUT                                                                                                                                                                                       |

| 5-1<br>5-2<br>5-3<br>5-4 | Visual Inspection<br>Installing the 1771<br>Interconnecting Drive and Interface<br>Operational Tests                                                                                           |

| 6                        | FIRMWARE AND DRIVERS                                                                                                                                                                           |

| 6-1<br>6-2               | The Hardware Bootstrap<br>Writing Driver Routines                                                                                                                                              |

| 7                        | REFERENCE INFORMATION                                                                                                                                                                          |

| 7-3<br>7-4<br>7-5        | Schematic Pin Function List Warranty Statement If you have problems                                                                                                                            |

The Tarbell Floppy Disk Interface is a programmed-data-transfer (not DMA) device. It plugs into your IMSAI or ALTAIR\* computer, and is designed to work with a variety of standard-size floppy disk drives. It includes a 32-byte ROM bootstrap program, which is automatically enabled when the computer RESET button is pushed, and which switches itself out after the bootstrap has run. In this way, no part of your memory needs to be dedicated to Read-Only-Memory (ROM). The interface runs at the standard speed of 250,000 bits per second, and the normal formatted capacity per diskette is 256 kilobytes. Places for two connectors are provided on the board. One 50-pin header connector and a cable with the mating connector are provided with the interface kit. The drive end of the cable has no connector, but a 50-pin edge connector may be added for \$10.00. There are four extra IC slots to allow you to do your own thing, and the connector pins come out to jumper pads, so you can adapt to different drives. The manual has the connections detailed for popular drives. An on-board dip-switch is used to select the device address, disable the bootstrap, and write-protect. Circuitry is included to run up to four drives, and eight can be accessed by using the spare IC slots.

The Tarbell Floppy Disk Interface and other related items can be bought in pieces, so that it's not necessary to make a single large outlay of cash. Because of this policy, the 6-month warranty will be limited to only those items traceable to Tarbell Electronics. Notice that we are offering the CP/M floppy disk operating system, which is described on another page. An owner's manual for the interface is included with the kit or the bare board, and is also available separately.

| Floppy Disk Interface Kit<br>CP/M Operating System (on disk)<br>CP/M System Manual Set (6)<br>BASIC-E Compiler Manual | 190.00<br>70.00<br>25.00<br>5.00 |                                                          |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------|

| GSI/Siemens 110 8" Floppy Disk Drive                                                                                  | 525.00                           | NOTE: These prices are                                   |

| Power Supply for 1 GSI 110                                                                                            | 75.00                            | subject to change without notice. There are no discounts |

| Floppy Disk Interface Manual                                                                                          | 5.00                             | for complete systems; just                               |

| Bare Floppy Disk Interface Board                                                                                      | 40.00                            | add the prices together to find                          |

| Kit with all parts except 1771                                                                                        | 150.00                           | the total for your purchase.                             |

| Western Digital 1771 FDC IC                                                                                           | 60.00                            |                                                          |

| Assembled Floppy Disk Interface                                                                                       | 265.00                           |                                                          |

| PerSci 270 Dual Floppy Disk Drive                                                                                     | 1295.00                          |                                                          |

| Power Supply for PerSci 270                                                                                           | 125.00                           |                                                          |

| Blank Formatted Diskette                                                                                              | 10.00                            |                                                          |

| BASIC-E Source Listing (PL/M)                                                                                         | 15.00                            |                                                          |

| Additional Charge for Special Cable                                                                                   | 10.00                            |                                                          |

| Package of IC Sockets (35)                                                                                            | 10.00                            |                                                          |

| CBASIC on disk                                                                                                        | 85.00                            |                                                          |

| CBASIC manual                                                                                                         | 15.00                            |                                                          |

Since Tarbell Electronics does not wish to get into the business of selling complete systems, we encourage you to buy your system, including the floppy disk drive, from your local dealer. If you add up the prices of the first six items, however, you can see that a complete floppy disk system including software and hardware can be had for less than a thousand dollars. Note that the Tarbell Floppy Disk Interface is not designed to work with double-density or mini-floppys, although it will work with multiple and double-sided drives. The drives that it has worked with so far include the Shugart 800/801, the Innovex 410, the Innovex 220 (modified by a jumper change), the GSI 110, the CDC 803, and the PerSci 270, the PerSci 70, the Wangco/Orbis 76, the Pertec 400, and the Calcomp 140. The interface may not work reliably with some dynamic memories.

The first deliveries were made July 2, 1977. Delivery from the factory is 3-4 weeks after receiving your order, and individuals must send cash in advance. For faster delivery, check with your local dealer.

<sup>\*</sup> ALTAIR is a trademark/tradename of MITS, Inc.

### OPERATING INSTRUCTIONS

One nice thing about using a floppy disk is that the operation of the hardware is fairly simple:

- 1. Turn on computer power.

- 2. Turn on disk power.

- 3. Put a diskette into the drive and close the door.

- 4. Press the reset button on the computer.

- 5. Press the run button on the computer.

At this time, the hardware bootstrap routine automatically reads in the first sector of track zero, and runs it. This 128 byte module contains a more sophisticated loader which brings in the main operating system and runs it. Therefore, you should see the header that the operating system prints when it first comes up. In CP/M, this is something like "CPM V1.3". From this point on, you need to refer to your manual on CP/M (or whatever operating system you're using).

When you're all done, the shut-down procedure is as follows:

- 1. Open the disk drive door and remove the diskette.

- 2. Turn off the power to the disk drive.

- 3. Turn off the computer power.

### GENERAL NOTES ABOUT USING YOUR DISK SYSTEM

- 1. In general, floppy disk drives are a very reliable method of storing data if nothing else goes wrong in the computer. As with any external medium, however, there will be some errors. These are normally detected by the interface and the software. The manual on your disk drive should have some figures as to the reliability of your particular unit. As a rule, you can expect the Tarbell floppy disk interface and your floppy disk drive to work for many days at a time without an error.

- 2. On the other hand, remember that your floppy disk interface is an on-line device; that is, the computer can write onto it any time, unless the write-protect is on. This has its advantages, but it also means that the disk is always subject to wipe-out,

destroying some or all of the information on it. All it takes is a software error, power-line glitch or a temporary hardware malfunction to lose many hours, days, and even weeks of work if you only have that single copy.

It is therefore desirable to keep frequent back-ups of your files. This can be done by copying files to another diskette or to cassette. In this way, only the information entered since the last backup can be destroyed.

- 3. When first using any operating system, including CPM, run it in the write-protected mode for a little bit. Then make a back-up copy as soon as possible.

- 4. Note that CP/M always loads a program for execution at 100 hex. If it is desired to run a program at zero, such as basic, it must first be loaded at 100 hex and then moved down.

- 5. When the bootstrap switch (7) is on, a reset will gate the bootstrap program onto the bus. Even programs that run in other parts of the memory may be adversely affected if you attempt to run them before the bootstrap is disabled. Although the bootstrap is normally disabled automatically, there may be times when you want to disable it manually. This can be done by putting front panel data switch 5 to the upposition and doing an examine, or by turning off dip-switch 7.

- 6, There is a difference in the reliability of different manufacturer's diskette media. We at Tarbell Electronics have not yet decided which ones are the best. Ask your friends who know. Try several kinds. You will find that you get more errors on some than on others.

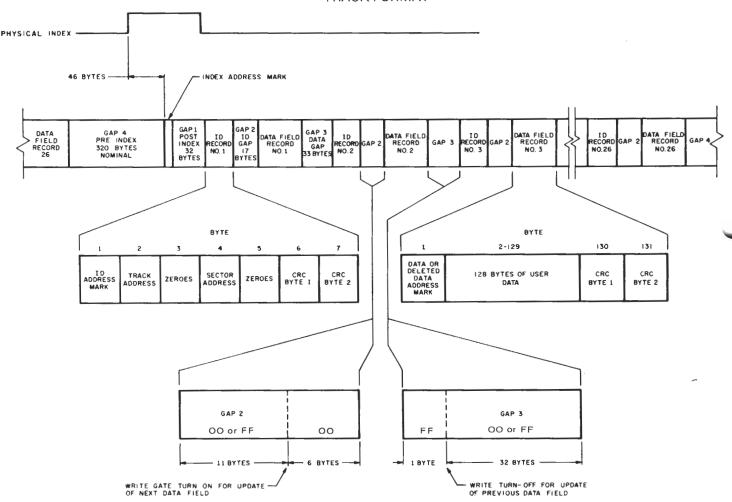

- 7. Diskettes are usually initialized by the manufacturer in some way. IBM format dictates a certain sequence of information about track number, sector number, fill characters, etc. on each track. The proper format for IBM compatibility is shown in the 1771 data sheet.

- 1. All RAM boards used in this disk operating system must have no wait states.

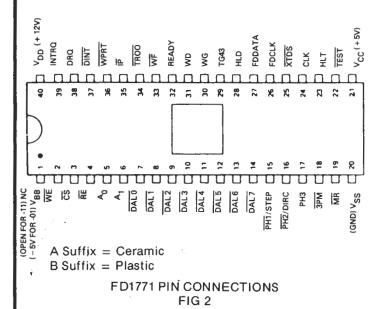

- 2. Take extreme care in handling the FD1771B-01 integrated circuit. Being a MOS device, it is liable to destruction from static charge induced by excessive handling--and it's expensive.

- 3. Before removing or installing the floppy disk interface board or any board in your computer, turn off the power and wait for at least ten seconds to let the capacitors discharge.

- 4. Before turning the computer power or the disk power on or off, be sure that the disk door is open, and preferably that the diskette is removed—so any transients won't wipe out the disk.

- 5. Always turn on the computer power before the disk power, and turn off the disk power before the computer power.

### **BASIC-E Compiler Description**

This compiler is a public-domain piece of software written by Gordon E. Eubanks, Jr. As provided by Tarbell Electronics, it is meant to work with the CP/M™ Disk Operating System. With the CP/M, it requires about 20K bytes of main memory. Since it is a compiler, as opposed to an interpreter, it has some advantages: 1) the program will probably run faster than with an interpreter, 2) the program will probably use less memory than with an interpreter. There are also some disadvantages: 1) it is not as easy to develop a program, because editing must be done separately, 2) it cannot be easily used with a cassette, because there are several steps that are not easily and quickly performed by a cassette unit, 3) In this version there is no PEEK or POKE, no PRINT USING, no CALL to machine code programs, and no LPRINT. These are all available in CBASIC, which costs \$100.00.

The following statements are valid in BASIC-E:

FOR, NEXT, FILE, CLOSE, GOSUB, GOTO, INPUT, LET, ON, PRINT, READ, RESTORE, RETURN, RANDOMIZE, OUT, STOP, DATA, DEF, DIM, END, IF, REM, ELSE, THEN.

The following built-in functions are valid in BASIC-E:

ABS, ASC, ATN, CHR\$ COS, COSH, FRE, INP, INT, LEFT\$, LEN, LOG, MID\$, PO\$, RIGHT\$, RND, SGN, SIN, SINH, STR\$, SQR, TAB, TAN, VAL, EXP.

The following logical connectives are available: AND, EQ, GE, GT, LE, LT, NE, NOT, OR, <, >, =.

There are 26 compiler error messages, and 23 run-time error messages, all of two characters each.

Disk files may be read, written or updated by the BASIC-E program using both sequential and random access. There are blocked and unblocked files. The program can select any disk available to CP/M.

Using the BASIC-E compiler consists of three main steps:

- 1) The source program is created on disk using the Editor.

- 2) The source is compiled by the compiler, which produces an intermediate file.

- 3) The intermediate file is then run by the run-time monitor.

Line numbers need only be used on statements to which control is passed, and do not have to be in ascending order. Using identifiers longer than two characters and indenting statements to enhance readability does not affect the size of the object file created by the compiler. The first 31 characters of identifiers are used by the compiler.

The 40-page manual is available for \$5.00.

The compiler and run-time monitor are included on our CP/M diskette, and are also available separately on a diskette for \$10.00.

The complete listing, which is written mostly in PL/M, is available for \$15.00.

# CP/M™ BY DIGITAL RESEARCH — A COMPLETE FLOPPY DISK OPERATING SYSTEM FOR THE TARBELL FLOPPY DISK INTERFACE.

The CP/M Disk operating system has been in existence for over two years in various manufacturer's products, and thus has had extensive field testing. It is now being made available to the hobby community. It is licensed software, and copying for other individuals is prohibited. We feel this is justified, as the cost, \$100, is low for such a good system.

The following commands are built in to the operating system:

DIR List all or selected portions of the directory (file list)

TYPE Type the contents of an ASCII file on the console

REN Rename a file to a different name

ERA Erase a file or files from the disk

SAVE Save memory on disk for later load

The following programs are included on the disk, and are invoked just like commands by typing the name:

PIP Peripheral Interchange Program moves files around

SUBMIT Batch processing program for predefined list of commands

ED A really nice, string-oriented text editor

ASM Assembler to convert assembly language to machine code

DDT Dynamic Debugging Tool for memory dumps, loads, traces

LOAD Convert hex file to memory image file

DUMP Dump file in hex onto console

SYSGEN Generates new CP/M systems for backup

BASIC BASIC-E compiler has both sequential and random file access

RUN Run-time interpreter for BASIC-E programs

STAT Prints the amount of disk storage still available and amount used for each file

CPM Generates different sized CP/M systems

COPY Copies from one disk onto another, track by track

TAPELIB Provides extensive disk-to-cassette facilities.

The following source files are included on the disk:

CASDSK Transfers the named file from Tarbell cassette to disk

DSKCAS Transfers the named file from disk to Tarbell cassette

SBOOT Cold-Start loader which is loaded by bootstrap program

CBIOS Customer's Basic Input/Output System includes all drivers

FORMAT Reformats crashed diskettes

COPY Assembly language source for program above

INV Basic inventory program

Tarbell Electronics provides the system modified to work with the Tarbell floppy disk interface and a simple console interface, such as a teletype. The console is addressed with port O for status and port 1 for data. Bit O of status low means keyboard ready, and bit 7 of status low means printer ready. It is set up to work in 24 kbytes. The documentation includes a listing of the BIOS, and instructions which will enable you to patch the CBIOS for your own system.

As of March 1, 1978 the CP/M User's Group had 24 diskettes full of software. It costs \$4 to get on the mailing list, and the diskettes are \$8 each. The address is 164 West 83rd Street, New York, New York 10024.

### DOCUMENTATION:

CP/M FEATURES AND FACILITIES MANUAL

CP/M EDITOR, ASSEMBLER, AND DEBUGGER MANUALS

CP/M INTERFACE GUIDE

CP/M SYSTEM ALTERATION GUIDE

TARBELL CP/M USER'S GUIDE

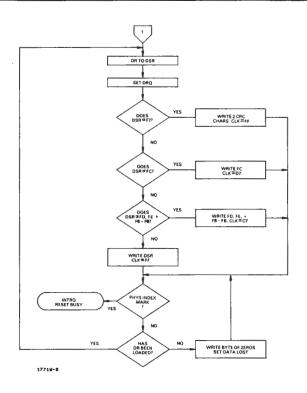

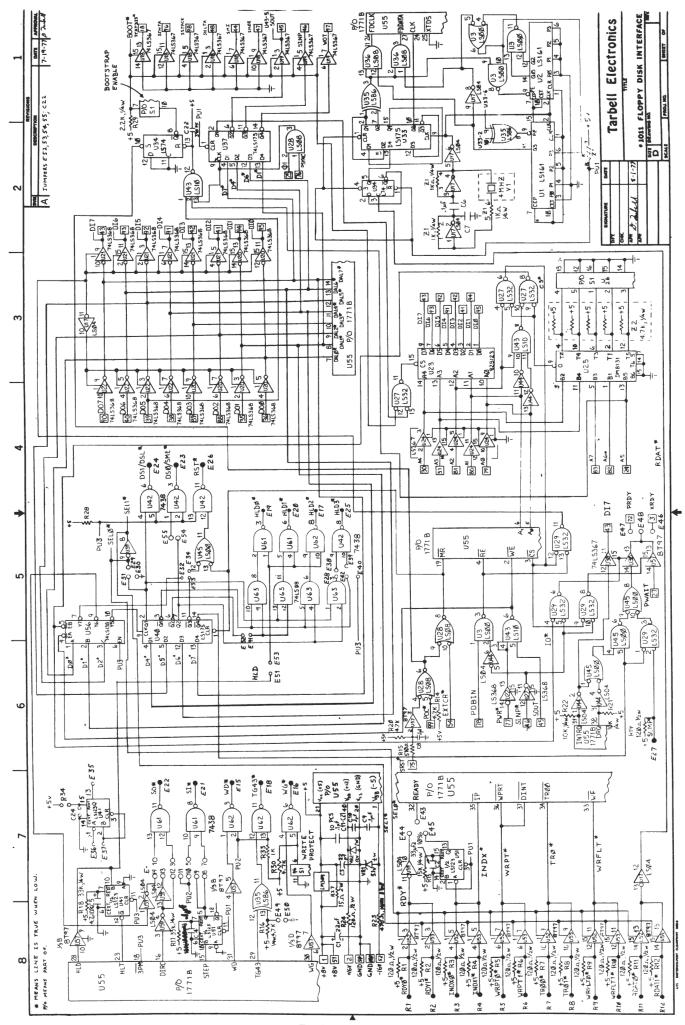

### THEORY OF OPERATION

The internal operation of a floppy disk system is probably the most complicated part of a micro-computer system. The hardware and software interact very closely. For best understanding, you should be familiar with both the 8080 machine/assembly language, and the common logic operations. Some understanding of the S-100 bus is also desirable. Remember to take into account any differences in your system's I/O setup as you follow the circuit.

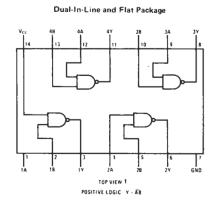

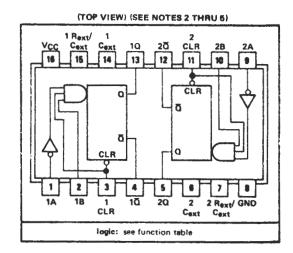

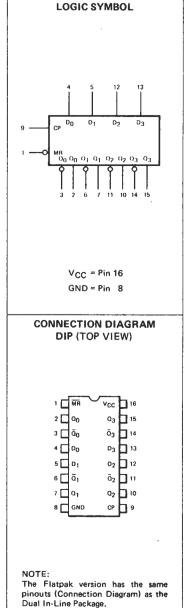

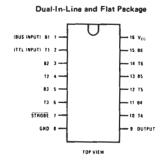

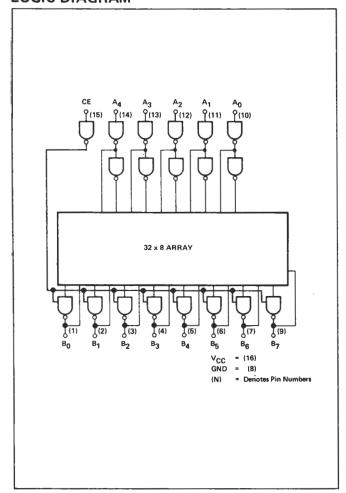

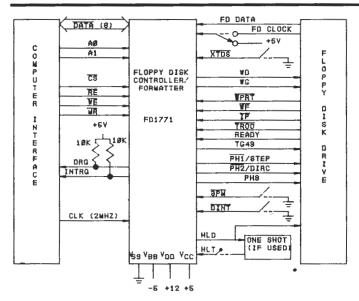

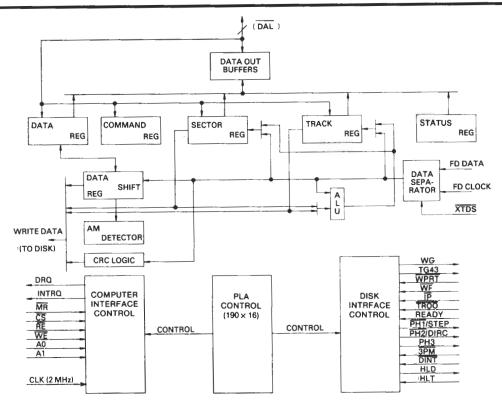

Since the Tarbell Floppy Disk Interface is designed around the Western Digital 1771 Floppy Disk Integrated Circuit, it would be helpful to skim over the data sheets (reproduced in the appendix with the manufacturer's permission). The main thing is to get a feeling for what the 1771 does in order to get a perspective of how it fits into the circuit.

ABOUT READING THE SCHEMATIC: note that lines of most drives are true when low--that is, a low voltage is a logic one. Active low lines have an asterisk following their name (e.g., RDY\*). The convention of this schematic is that a darkened dot is a possible connection to a floppy disk drive; an open circle is a pad for a possible jumper wire; a little square with a number in it is a pin on the 100-pin S-100 bus; and a line with none of these, but a name close to it, is a connection to another line with the same name.

To see what we need in the interface, let's see what it must connect to on each side. On the computer side, we have two simple instructions: input a byte (IN), and output a byte (OUT).

On the side of the floppy disk, we have many different things to be concerned with. First, the data lines going to and from the floppy drive are serial (one bit at a time). Thus we must have some way to convert parallel computer data to serial data on the drive side.

Next, the drive has several control lines. These are lines that tell the drive what to do. For example, there are two lines to tell the drive to move the head in or out. There's another line that tells the drive to engage the head against the disk surface (normally the head is not in contact to reduce wear on the disk and on the head). Another control line is usually used to reset the drive electronics and return the head back to the zero (outside) track. There's a set

of lines on some drives to select one drive out of several on a "daisy-chain" bus.

Still other lines tell the drive whether to read or write, and to write with how much current. All of these control lines need to be driven by the interface, normally at high-current TTL levels.

There are also a set of status lines which originate in the drive and come back to the interface. These lines tell the interface what is going on in the drive.

There is usually a ready line, set true when the drive is up to speed and a disk is in place. The index line has a pulse on it that indicates when the index hole in the diskette passes by the opening made for it. This is used by the interface to determine which sector is which on the track.

Some drives have a way to detect a notch cut out of the diskette holder, which indicates that disk is not to be written upon (write protected). There is usually a line going back to the interface to indicate this condition, so the controller can feed the information back to a program, and so the interface won't try to write to the disk. Another line indicates when the head is at track zero. Some drives have a write-fault flip-flop, which is set by an attempt to write when it was not possible. The output of this flip-flop is sometimes a status line.

You may begin to see now one reason why the floppy disk system is complicated: there are a lot of status and control lines to keep up with.

### DEVICE-SELECTION (BOARD ADDRESSING)

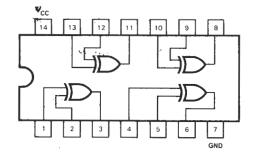

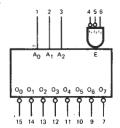

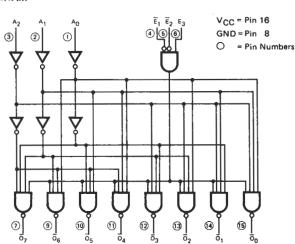

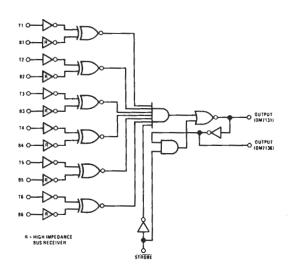

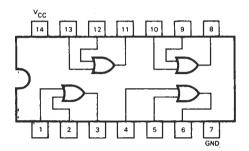

The first task of the interface is to recognize when the program sets the hardware for a read or a write operation to the disk. Selection circuitry is used to recognize 5 of the 256 possible I/O addresses. In this way, the floppy disk interface will respond only to the I/O instructions given to it, and not to those intended for other interfaces. The components associated with this process are located in the lower part of the schematic, slightly to right of the middle. These are dip-switch S-1 (5 positions used here), DM8131 U25 (a 6-bit comparator), 74LS32 OR gates U27, a 3-input NAND gate from 74LS10 U43, plus a few inverters.

The comparator checks for a match between the 5 high bits of the device address (lines A3, A4, A5, A6, and A7) and the bit pattern set on the dip switch. If the five lines (B1-B5) on the left each have the same logic level as the ones on the right (T1-T5), then the

comparator output at pin 9 goes low, indicating the disk interface is being selected. For any other combination, pin 9 goes high, and the instruction on the bus if left for some other interface.

Since the lower three address bits (A0, lAl and A2) can be any one of eight combinations, eight I/O ports out of the possible 256 are selected for use with the disk interface. Which set of eight depends on the upper five bits selected by the dip-switch.

From now on, let's assume that the upper five bits match—that is, an input or output instruction has been put on the bus with the correct address for the disk interface, so that the comparator output goes low). Note that this output goes up to an input on each of two OR gates (these gates are drawn as AND gates, to indicate that because of the inverted input signals, the AND function is being performed—ie. when both inputs of a gate are low, the output of the gate is low. On the top one of these two gates, pin 4 is connected to address line A2. So when A2 is low (and we've already said pin 5 is low), the gate's output at pin 6 is also low (active). This line is called CS\*, for chip—select—not, and is connected to the 1771 chip—select line. This line, then, will be active anytime there is a transfer to be made between the computer and the 1771.

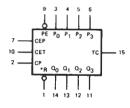

A similar decoding scheme sets each of the other individual operations. The table below shows how the address decoding scheme is set up, and the lines that are active for each situation.

| A2 | Al | A0 | FUNCTION OUT    | FUNCTION IN LIN  | NE ACTIVE   |

|----|----|----|-----------------|------------------|-------------|

| 0  | 0  | 0  | Command to 1771 | Status from 1771 | CS*         |

| 0  | 0  | 1  | Track to 1771   | Track from 1771  | CS*         |

| 0  | 1  | 0  | Sector to 1771  | Sector from 1771 | CS*         |

| 0  | 1  | 1  | Data to 1771    | Data from 1771   | CS*         |

| 1  | 0  | 0  | decoded by U56  | see table below  | U43-6,U27-8 |

| 1  | 0  | 1  | Not used        | Not used         |             |

| 1  | 1  | 0  | Not used        | Not used         |             |

| 1  | 1  | 1  | Not used        | Not used         |             |

Notice that no further decoding of address bits A0 and A1 is required to perform the first four functions in the table. That's because these functions are decoded inside the 1771. Notice also that U-55 pin 4 is fed by U3-3, which is true when PDBIN is high and SINP\* is low (both true). This indicates to the 1771 that an input (1771-to-computer) operation is taking place. U55-2 is fed by U43-6, which is true when an output (computer-to-1771) transfer is taking place; PWR\* and SOUT are both true.

If A2, A1 and A0 are 1, 0 and 0 respectively, and the other five I/O address bits match the setting of

switch S1, gates U44, U43, U27 and U25 (all in lower right) pull line IO\* down. This line, along with an active low signal from U43 (when SOUT and PWR\* inverted are true) enables U56 (a 3-to-8 line decoder). This is the fifth state given in the table above. Enabling U56 allows it to pull one of its output lines low in accordance to the state of the three least-significant data-out lines, D0, D1, and D2 which are the inputs to the decoder. Only the top three of the available 8 outputs are used: Y5, Y6, and Y7. This actually decodes the bottom three combinations of D0, D1, and D2, since these lines are active low (inverted). The table below shows what these combinations are used for:

| D2 | D1 | D0 | Y | U56- | FUNCTION DESCRIPTION                     |

|----|----|----|---|------|------------------------------------------|

| 0  | 0  | 0  | 7 | 7    | Pad E-32, can be used to pulse RST* line |

|    |    |    |   | 9    | Inverted, then to E-14 for SO* line      |

| 0  | 1  | 0  | 5 | 10   | Strobes data bits 4,5,6,7 into latch U40 |

### BUFFERS

Once the board has been selected and the operation decoded, the actual data transfers are done by a series of buffers.

The buffers in this interface have three main purposes: 1) To protect the expensive LSI chip (1771 IC) from voltage transients on external lines; 2) To provide sufficient drive current for the lines that need it; 3) To provide multiplexing (switching) of two data paths. The signal that comes out of a buffer is either the same signal that went in or simply the inverted form of what went in.

Looking in the lower left corner of the schematic, we see a row of 12 buffers. All the data inputs for these buffers come from the disk drives(s), and all the outputs go someplace in the interface. The line on the top of each buffer is the control line. When this line is low, the buffer is active--that is, the output equals the input for that buffer. When the control line is high, the output for that buffer is floating in an open state so it does not affect any connecting circuits. Notice that every other buffer is hooked to the same control line, and that there are two main control lines. One control line activates the buffers that have signals from drive number 0, the other control line activates the buffers that have signals from drive number 1. Thus the buffer acting as a 12-line to 6-line multiplexer. Thus the buffers are This multiplexing operation is only necessary if there more than one drive, and the drives do not have multiplexers built in (most late-model drives do).

Also notice the 120 ohm resistors on the inputs of these buffers. They have two purposes. One is to

match the normal low line impedance so that ringing caused by reflections will be minimized. The other is to make it difficult for external noise to provide enough current to cause a false signal on the line. The six outputs of these buffer pairs will be called by their signal name, while their inputs are named by the signal line plus the number of the drive (i.e., RDY, RDYO, and RDY1).

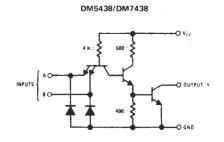

Next move your eye on the schematic up and slightly to the right. There is a row of five 7438 2-input NAND high- current open-collector gates. These are used as buffers in this interface. Their main advantage is that they are capable of supplying the high current required by the floppy drive(s). They also can double as NAND gates. As set by the jumpers, they are used to send the appropriate signals from the 1771 to the various disk control lines (see the 1771 data sheet and your drive's manual for a full explanation of the various lines). If both inputs to these gates are a logic high, the output is low. To the right, in the middle of the schematic, are seven more of these 7438 buffers. These too go to the drive(s).

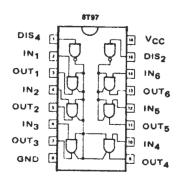

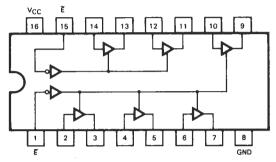

About two thirds of the way to the right near the top of the schematic, there are two rows of 8 These buffers buffer/inverters each. link the computer input and output data busses to the 1771 data bus. The inputs to the left row of buffers come from S-100 bus. The control lines for all these the buffers are connected together. When this control line is low, the data on the output data bus is inverted and gated onto the 1771 data bus. The gates on the right hand side do the reverse: when their control line is low, the data on the 1771 data bus is gated onto the computer's input data bus.

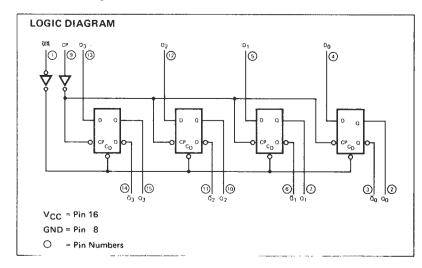

The last set of buffers is on the far right-hand side of the schematic, and is a row of nine non-inverting buffers. Their purpose is to suspend the usual CPU control of the data bus and gate the proper control signals onto the S-100 status lines to put the bootstrap in operation. When their common control line is low, whatever is on their inputs is gated to their outputs. Once the bootstrap is completed, U43, U34, and U37 relinquish control back to the bus.

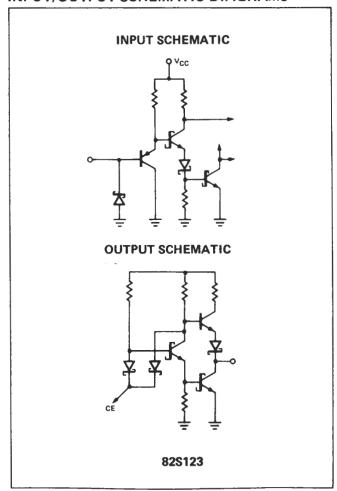

Bootstrap is initiated by NOR gate U28 (lower right) receiving Power On Clear (also generated by RESET) from the computer, which sets flip-flop U34 (upper right). The not-Q output, if passed by Sl position 5, is the bootstrap signal. This gates those nine buffers, and is used along with a signal from U37 (upper right) to activate U27 (middle) during the read cycle, thus reading from the 82S123 memory but writing through the bus to regular RAM.

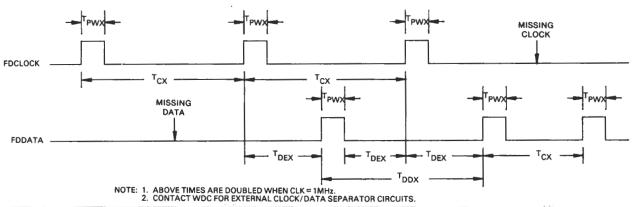

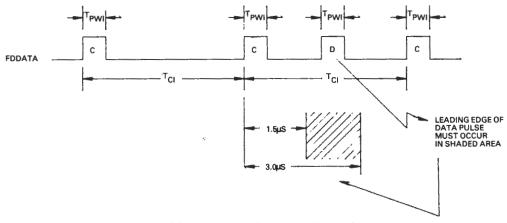

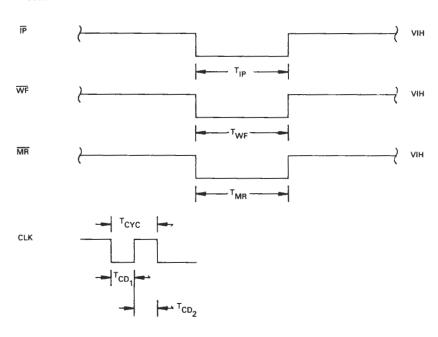

### TIMING CIRCUITS, SEPERATOR, AND PROCESSOR HOLD

At the lower right of the schematic, Ul, U2, Ul7, U33, U34, U35, and U36 form the clock and data seperator, which operates on the raw data which comes in on the line wich runs across the very bottom of the schematic. The actual clock oscillator circuit (also lower right) is composed of two sectons of Ul7 plus the 4MHz crystal Yl. Grounding pin 25 of the 1771 (XTDS\*) disables the internal seperator.

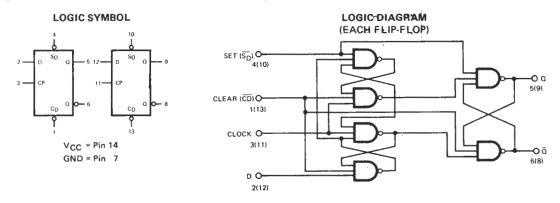

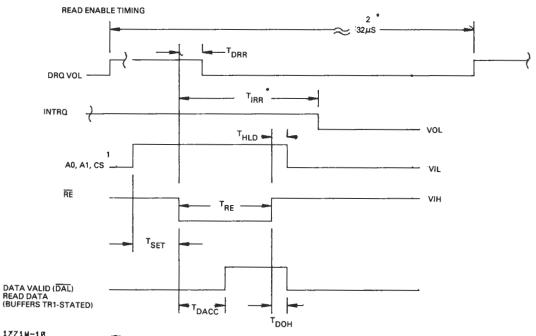

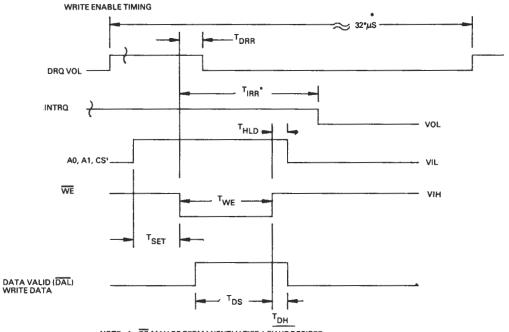

On the bottom middle, the INTRQ and DRQ signals from the 1771 are used to control the run or wait state of the CPU through gates U30 and U57 and bus signals PRDY or XRDY. These circuits allow the 1771 to temporarily suspend execution of the next CPU instruction until an internal process has been completed.

### HEAD-LOAD CIRCUIT

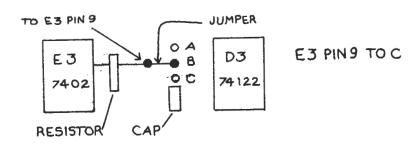

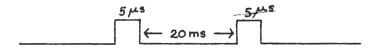

The 1771 checks for head-load by looking at the HLT line 10 milliseconds after the HLD line is activated. U41 and U57, in the upper-left corner of the schematic, sample the HLD line and generate the proper delay to allow for the physical head-load time of the drive before passing the signal on to the HLT input of the 1771.

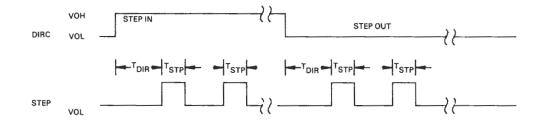

### STEP-IN AND STEP-OUT CIRCUIT

The 1771 signals your drive to step the head in or out by providing a short pulse from the step output and a DIRC output which is high for stepping in and low for stepping out. These signals must be reformatted for many drives, and they must be buffered. The circuitry at U59, U51 and U61, all in the upper left side, perform these tasks.

Most drives require a longer step pulse than is output at pin 15 of the 1771, so one-shot U51 is used to stretch the pulse out. For drives which require a step signal and the same polarity direction signal, like the Innovex 410, the other signals are simply buffered and then routed to the drives by the appropriate jumpers. For drives like the CDC BR803A, which require a step-in and step-out line, the jumpers are set to make these circuits decode those signals from the DIRC and step lines.

A few drives require step signals faster than those generated by the 1771. The line into pin 1 of buffer U59 can be driven directly by the computer, and can therefore be pulsed at a much faster rate. However,

in this case, the program must keep track of the number of pulses that this line puts out, plus observing any timing constraints.

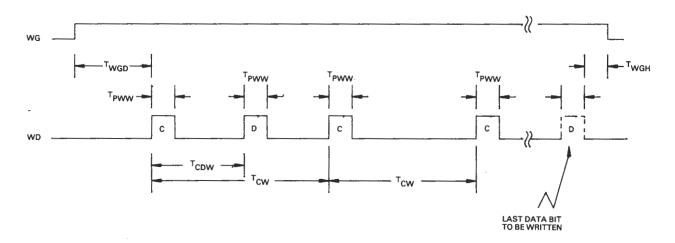

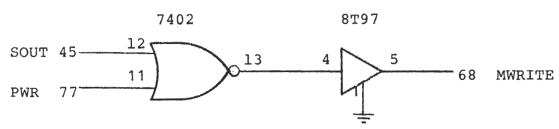

WRITE DATA, WRITE GATE, TRACK GREATER THAN 43

The write data, write gate, and track greater-than-43 signals control the write-to-disk functions. The circuits to control these signals are just above the middle left.

The write-data line contains the actual data mixed with a clock signal. From pin 31 of the 1771, it goes through buffer U57, and line driver U62, and then out through the jumpers to the disk. The TG43 line which tells the drive to reduce the head current while writing on the physically smaller tracks is set high when the track number is higher than 43. From the 1771 pin 29, it goes to U35, where it can be inverted for drives which require the opposite polarity, and then through driver U62 and the jumpers out to the disk.

The write-gate signal tells the drive that it is time to start a write operation. It comes out of the 1771 pin 30, is buffered by U57, and NANDed with the write protect signal at U62, where it goes to the jumper pads and the disk. The write gate signal can only go active (low) when switch position 6 of DIP-switch Sl is off, providing a logic 1 to pin 5 of U62. This switch allows you to prevent any write operation to the disk, regardless of any deliberate or accidental commands in the program. When this switch is not in the protect position, any time the write-gate is driven high from pin 30 of the 1771, the disk will be overwritten.

POWER SUPPLY (VOLTAGE REGULATOR) SECTION

The interface requires +5 Volts, +12 Volts, and -5 Volts. These are provided by on-board regulators driven from the unregulated DC voltages of the S-100 bus.

A 7805 (LM309) regulator supplies the +5 Volts. To make it run a little cooler, a 15 Ohm 2 watt resistor has been placed in parallel to bypass some of the current while still allowing the regulator to control the voltage.

The +12 Volt DC is regulated by a 12 Volt zener and 120 ohm resistor, since this supply must only provide a small amount of current. The -5 Volt supply is a similar zener-resistor pair.

1/4 W resistors

2 W resistor

LED

disc capacitor

electrolytic capacitor

mylar capacitors

DIP switch

integrated circuits

resistor networks

crystal

1771

40-pin socket

16-pin Bocket

50-pin header

| QTY                                                                                               | PART NO.                                                                                                                                                                                                                                      | REF. NUMBERS                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

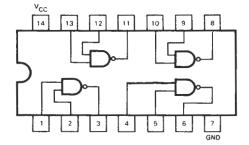

| 2<br>3<br>4<br>3<br>1<br>1<br>2<br>3<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1       | 74LS161 74LS00 74LS04 74LS367 74LS368 82S123 DM8131 74LS32 74LS08 74LS175 74LS74 74LS86 74LS123 7438 74LS10 8T97 FD1771 74LS138 7805UC                                                                                                        | U1,2 U3,45 U17,44,59 U18,19,24,30 U20,21,22 U23 U25 U27,29 U28,36,63 U33,37,40 U34 U35 U41,51 U42,61,62 U43 U52,53,57 U55 U56 U65           | 4-Bit Binary Counter Quad 2-Input NAND Gate Hex Inverter Hex Tri-State Buffer Hex Tri-State Inverter 32-Byte PROM 6-Bit Digital Comparitor Quad 2-Input OR Gate Quad 2-Input AND Gate Quad Latch Dual Type-D Flip-Flop Quad Exclusive-OR Gate Dual Retriggerable 1-shot Quad 2-Input NAND Buffer O/C Triple 3-Input NAND Gate Hex Tri-State Buffer Floppy Disk Controller 3-8 Line Decoder 5-Volt Regulator                                                                                                                                                                              |

| 14<br>1<br>4<br>1<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 120-1/2W<br>15K-1/4W<br>4.7K-1/4W<br>510-1/4W<br>33K-1/4W<br>10K-1/4W<br>470-1/2W<br>15-2W<br>1K-1/4W<br>2.2K-1/4W<br>330-1/4W<br>1KNW8<br>4.7KNW6<br>22MFD<br>33MFD<br>.1MFD<br>4.7MFD<br>390PF<br>1N751<br>1N4742<br>LED<br>CY3A<br>DIP-SW7 | R1-12,19,24 R13 R14,16,20,30 R15 R17,18 R21,22 R23 R27 R28,33 R29 (For Tests) Z1 Z2 C1,3 C2 C4,6,8-21 C5 C22 VR1 VR2 (For Tests) Y1 U26(S1) | 120 Ohm 1/2 Watt Resistor 15 Kohm 1/4 Watt Resistor 4.7 Kohm 1/4 Watt Resistor 510 Ohm 1/4 Watt Resistor 33 Kohm 1/4 Watt Resistor 10 Kohm 1/4 Watt Resistor 10 Kohm 1/2 Watt Resistor 15 Ohm 2 Watt Resistor 15 Ohm 2 Watt Resistor 1 Kohm 1/4 Watt Resistor 2.2 Kohm 1/4 Watt Resistor 330 Ohm 1/4 Watt Resistor 1 Kohm Resistor Network (8-pin) 4.7 Kohm Res. Network (6-pin) 22 Mfd 25-Volt Capacitor 33 Mfd 10% Capacitor .1 Mfd 10-Volt Capacitor 4.7 Mfd 10% Capacitor 5.1-Volt 1/2 Watt Zener 12-Volt 1 Watt Zener Light-Emitting Diode 4 MHz Crystal 7 or 8-Position Dip-Switch |

| 1<br>1<br>2                                                                                       | HS1<br>Set#6<br>Set#2                                                                                                                                                                                                                         | HS1<br>(For HS1)<br>(For Header)                                                                                                            | Heat Sink<br>#6 Screw, Nut, Washer<br>#2 Screw, Nut, Washer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1<br>1<br>1<br>1                                                                                  | 1011<br>FDCABLE<br>HDR-50<br>DIP-S16<br>DIP-S40                                                                                                                                                                                               | PCB<br>In Header<br>At J1<br>At U23<br>At U55                                                                                               | Printed Circuit Board<br>50-Cond. Cable & 1 Connector<br>50-pin Header Connector<br>16-Pin Dip Socket<br>40-Pin Dip Socket                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| QTY                                                                                     | PART NO.                                                                                                                                                                                                                                                        | REF. NUMBERS                                                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>3<br>4<br>3<br>1<br>1<br>2<br>3<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>1<br>1       | 74LS161 74LS00 74LS04 74LS367 74LS368 82S123 DM8131 74LS32 74LS08 74LS175 74LS74 74LS86 74LS123 7438 74LS10 8T97 FD1771 74LS138 7805UC                                                                                                                          | U1,2 U3,45 U17,44,59 U18,19,24,30 U20,21,22 U23 U25 U27,29 U28,36,63 U33,37,40 U34 U35 U41,51 U42,61,62 U43 U52,53,57 U55 U56 U65                     | 4-Bit Binary Counter Quad 2-Input NAND Gate Hex Inverter Hex Tri-State Buffer Hex Tri-State Inverter 32-Byte PROM 6-Bit Digital Comparitor Quad 2-Input OR Gate Quad 2-Input AND Gate Quad Latch Dual Type-D Flip-Flop Quad Exclusive-OR Gate Dual Retriggerable 1-shot Quad 2-Input NAND Buffer O/C Triple 3-Input NAND Gate Hex Tri-State Buffer Floppy Disk Controller 3-8 Line Decoder 5-Volt Regulator                                                                                                                                                                                                                      |

| 14<br>1<br>6<br>1<br>2<br>3<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 120-1/2W<br>15K-1/4W<br>4.7K-1/4W<br>510-1/4W<br>33K-1/4W<br>10K-1/4W<br>470-1/2W<br>15-2W<br>1K-1/4W<br>2.2K-1/4W<br>330-1/4W<br>1KNW8<br>4.7KNW6<br>22MFD<br>33MFD<br>.1MFD<br>4.7MFD<br>390PF<br>100PF<br>100PF<br>1N751<br>1N4742<br>LED<br>CY3A<br>DIP-SW7 | R1-12,19,24 R13 R14,16,20,30,35 R15 R17,18 R21,22,34 R23 R27 R28,33 R29 (For Tests) Z1 Z2 C1,3 C2 C4,6,8-21 C5 C22 C24 VR1 VR2 (For Tests) Y1 U26(S1) | 120 Ohm 1/2 Watt Resistor 15 Kohm 1/4 Watt Resistor 36 4.7 Kohm 1/4 Watt Resistor 510 Ohm 1/4 Watt Resistor 33 Kohm 1/4 Watt Resistor 10 Kohm 1/4 Watt Resistor 470 Ohm 1/2 Watt Resistor 15 Ohm 2 Watt Resistor 1 Kohm 1/4 Watt Resistor 1 Kohm 1/4 Watt Resistor 2.2 Kohm 1/4 Watt Resistor 330 Ohm 1/4 Watt Resistor 1 Kohm Resistor Network (8-pin) 4.7 Kohm Res. Network (6-pin) 22 Mfd 25-Volt Capacitor 33 Mfd 10% Capacitor 1 Mfd 10-Volt Capacitor 4.7 Mfd 10% Capacitor 390 Pfd Capacitor 100 Pfd Capacitor 5.1-Volt 1/2 Watt Zener 12-Volt 1 Watt Zener Light-Emitting Diode 4 MHz Crystal 7 or 8-Position Dip-Switch |

| 1<br>1<br>2                                                                             | HS1<br>Set#6<br>Set#2                                                                                                                                                                                                                                           | HS1<br>(For HS1)<br>(For Header)                                                                                                                      | Heat Sink<br>#6 Screw, Nut, Washer<br>#2 Screw, Nut, Washer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1<br>1<br>1<br>1                                                                        | 1011<br>FDCABLE<br>HDR-50<br>DIP-S16<br>DIP-S40                                                                                                                                                                                                                 | PCB<br>In Header<br>At J1<br>At U23<br>At U55                                                                                                         | Printed Circuit Board<br>50-Cond. Cable & 1 Connector<br>50-pin Header Connector<br>16-Pin Dip Socket<br>40-Pin Dip Socket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

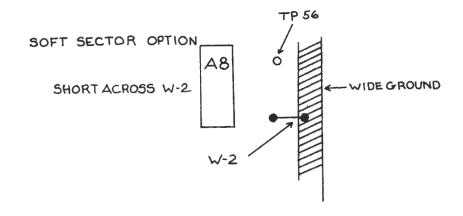

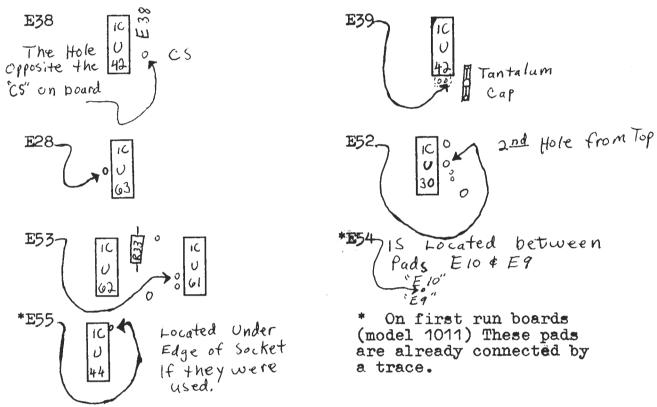

There are two major changes on the rev C boards:

- 1. Changes have been incorporated to allow operation on SOL-20 (Processor Technology) computers without the additional cuts and jumpers that are specified in step 4 on page 7-9 of this manual.

- 2. Changes have been incorporated to allow operation with Z-80 CPU boards by using the phantom line (pin 67). The jumpers required are listed below. The steps on page 7-8 are only valid for Z-80 operation with rev A, and are no longer valid for revision C.

Whether you're going to operate your interface with an 8080 or with a Z80 CPU, install the following items:

- ( ) A 100 pf disc ceramic capacitor at C24.

- () A 10 kohm 1/4 watt resistor (brown, black, orange) at R34.

- () A 4.7 kohm 1/4 watt resistor (yellow, violet, red) at R35.

- () The write protect switch (S1-6) now has three options: If you want the switch to protect

- 1. only even numbered drives, jumper E36 to E31.

- 2. only odd numbered drives, jumper E36 to E42.

- 3. all drives, jumper E36 to E37.

If you are going to operate your interface with a Z-80 CPU, or with an 8080 CPU and a memory with a phantom line, the memory located at address zero should have a phantom line (pin 67) which disables the memory when it is low. Then install the following items:

- () A jumper wire between E59 and E60.

- () A jumper wire between E63 and E58.

- () A 4.7 kohm 1/4 watt resistor (yellow, violet, red) at R36.

- () A jumper wire between E56 and E65.

If you are going to operate with an 8080 CPU without using the phantom line (standard), install the following items:

- () A jumper between E63 and E64.

- () A jumper between E56 and E57.

- () A jumper between E61 and E62.

### ASSEMBLY

The assembly of the disc interface consists of a series of small steps, each one of which should be checked before proceeding to the next one. You should have a computer mainframe of the IMSAI or ALTAIR\* type available.

You may elect, of course, to disregard the detailed instructions and just mount the components as shown in the assembly drawing, plug the board in, and hope for the best. If you do take this route, please at least check the voltages that go to the 1771 chip before this last part is installed (+5, -5, +12). Be sure to leave R27 out until you have all the IC's installed.

### NOTES:

- 1) When the instructions say "install board in mainframe in test configuration", make sure mainframe power has been off for at least 10 seconds, then install the board in any slot. No other interface board or memory board should be in the mainframe unless specified in the instructions. At the end of the test, turn off mainframe power and wait at least 10 seconds before removing the disk interface board.

- 2) "Locate and install" means find the indicated parts, mount each one as shown on the circuit board diagram, and solder them in place.

- 3) Some of the tests require use of the front panel that is normally included on an IMSAI or ALTAIR\* computer. If your computer does not have a front panel with several lights and switches, you will have to skip over these sections.

\*\*\*\*\*

### 1. Inspection

- () Check the printed circuit board carefully for flaws.

Look especially closely for any shorts between traces which

might later be covered under a socket or an IC.

- () Check contents of the kit against parts list. If any parts are missing, contact Tarbell Electronics for prompt replacement. If you have any extra parts, be sure and note this too, so they won't confuse you later on.

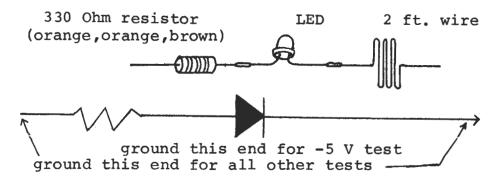

- 2. Construct LED (Light-Emitting-Diode) Tester

- () Find the 330 ohm resistor (orange, orange, brown) and the LED. As shown in the diagram, solder the LED anode (usually the anode is marked in red, or the cathode is a wider lead) to the resistor. Connect the LED cathode to a two-foot length of scrap flexible insulated wire (18-24 gauge is best). Strip about 1/4 inch from the end of the wire. This assembly will be referred to as the "LED probe".

<sup>\*</sup> ALTAIR is a trademark/tradename of MITS, Inc.

- 3. Install 40-pin socket

- () Find the 40-pin socket. Using the parts layout diagram, orient the socket so the notch indicating pin 1 faces the top of the card and pin 1 fits in the square pad.

- () Insert the socket, and carefully check that every pin is showing through on the solder side of the board.

- ( ) Hold the socket in firmly and solder all pins.

- 4. -5 Volt regulator

- ( ) Locate and install the following components:

- () R23--470 ohm 1/2 watt resistor (yellow, violet, brown)

- ( ) VR1--5.1 volt zener diode (marked 1N751); make sure polarity band is at left

- () C9--.1 MFD 10-volt disc ceramic capacitor.

Test--Install board in mainframe in the test configuration.

- () Temporarily connect the resistor end of the LED probe to a circuit ground. Touch the end of the wire from the probe to the left end of R23, which connects to the -16 volt bus. Notice the relative brightness of the LED.

- ( ) Move the wire to the right end of R23. The glow should be considerably less but not extinct.

- () If you have a voltmeter or oscilloscope, check that voltage at the right end of R23 is -5.1 within 10%.

- 5. +5 Volt regulator

- () Find the parts for the 5-volt regulator: () 7805 or LM309 3-pin IC; () regulator heat sink; () #6-32 mounting screw, and matching nut and washer;

- () Using the assembly diagram, position the regulator at U65. Insert the leads through the appropriate holes.

- () With the heat sink in place between the regulator and the board, bend the regulator pins over and fasten the regulator body against the heat sink with the screw and washer on the solder side of the board and the nut on the parts side. Solder the regulator in.

- () Install a 22 mfd. capacitor at Cl observing polarity shown on diagram.

- () Install the other 22 mfd. capacitor at C3, again observing polarity.

Test--Install the board in the computer mainframe in the test configuration.

- ( ) Connect the wire lead end of the LED probe to a good circuit ground. This end will remain connected for the rest of the asembly process. Touch the resistor end of the probe to the bottom lead of the +5 volt regulator (U65). Note the relative brightness.

- () Move the probe to the middle lead of the regulator. The light should go out altogether if not, this pin is not properly grounded.

- () Move the probe to the top lead of the regulator. The LED should glow with slightly less brightness than at the bottom lead.

- ( ) The top lead should measure +5 volts within 10% using a voltmeter or oscilloscope.

### 6. +12 Volt regulator

- ( ) Locate and install the following parts:

- () R24--120 ohm 1/2 watt carbon resistor (brown, red, brown)

- () VR2--12-volt 1 watt zener diode (marked 1N4742); be sure to place the polarity band of VR2 at right, as shown on the assembly diagram. On diodes marked with color bands, the end toward which the colors are grouped is the right end.

- () C10--.1 Mfd 10-volt disc ceramic capacitor.

Test--Install the board in the test configuration.

- () Place the tip of the LED probe on the left end of R24 and notice the brightness.

- () Touch the probe to the right end of R24. Check that the glow is less, but still quite visible.

- () If you have an oscilloscope or voltmeter, the voltage at the right end of R24 should be +12 volts within 10%.

NOTE--Do not proceed until you are confident the foregoing circuits are working properly. If not, they might damage the 1771 IC or other expensive chips.

### 7. Primary address circuit

- ( ) Locate and install the following parts:

- ( ) U24--74LS367 hex buffer IC.

- () U25--DM8131 6-bit comparator IC.

- () Install the 4.7K 6-pin in-line resistor network at Z2 with the dot in the square pad.

- () Install switch s1 (7-position or 8-position DIP switch) in the upper 14 holes at U26, with switch #1 oriented toward the top of the board. If it is a 7-position switch, there will be two empty holes left at the bottom. If it's a 8-position, you have an extra switch for your own purposes.

### Test--Install board in test configuration.

- Set all switch positions off.

- () Using the computer's front panel switches, examine location F8 (hex).

- () Using the LED probe, check that pin 9 of IC 25 is in the low state (out).

- () Check that the LED goes on if any of the address switch positions (S1 1 to 5) on the board are changed.

( ) Reset the switches, and check that the LED goes on if any other location smaller than F8 is examined. Secondary Address Gate Circuitry Locate and install the following components: () U28--74LS08 quad 2-input and gate IC U30--74L\$367 hex buffer IC ( ) U57--8T97 hex buffer IC R20--4.7K ohms 1/4 watt resistor (yellow, violet, red) R16--4.7K ohms 1/4 watt resistor (yellow, violet, red) ( ) R14--4.7K ohms 1/4 watt resistor (yellow, violet, red) ( ) R15--510 ohm 1/4 watt resistor (green, brown, brown) ( ) C8--.1MFD 10 volt disc ceramic capacitor ) R28--1K ohm 1/4 watt resistor (brown, black, red) ) R33--1K ohm 1/4 watt resistor (brown, black, red) Test--Install board in test configuration. Connect probe to U28 pin 8. Push reset switch on computer. Pin 8 should go low (LED out). Push the external clear switch on computer. Pin 8 should go low. Command Logic decoding gates Locate and install the following components: () U27--74LS32 quad 2-input OR gate IC. U43--74LS10 triple 3-input NAND gate IC. ( ) ( ) U44--74LS04 hex invertor IC. Test--Install the board in the test configuration. Set all switch positions to off. This sets the base address to F8 (hex). Use the LED probe to look at U27 pin 6 and U27 pin 8 for high (LED on) or low (LED off) states as follows-examine each location shown in the address table below, and check that U27 pin 6 and 8 shows the indicated state: FUNCTION ADDRESS U27 PIN 6 U27 PIN 8 Status/Command Port F8 Low High High Track Command F9 Low High Sector Command FA Low FBLow High Data Port FCHigh Low Wait/Control Port High High Unused FDFEHigh High High FF High 10. Read-write-control decoding gates. Locate and install the following components: () U3--74LS00 quad 2-input NAND gate IC. U22--74LS368 hex invertor/buffer IC. ( ) U29--74LS32 quad 2-input OR gate IC.

| TestInstall board in test configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| () Install a memory card addressed at location 0. Using the computer's front panel switches, load this data:  ADDRESS DATA  0000 DB  0001 F8  0002 C3  0003 00  0004 00                                                                                                                                                                                                                                                                                                                                                                                              |

| Note: If you have an ALTAIR 8800b, it may be easier to put the port number in the upper 8 address switches, and the byte to output in the lower 8 switches.                                                                                                                                                                                                                                                                                                                                                                                                          |

| () Connect probe to U29 pin 11. Examine location 0 and single step. When the input light on your front panel comes on, U29 pin 11 should go low.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| () Install (with power off) a memory card addressed at 0. Using the computer front panel switches, deposit D3 (hex) at                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| location 0. Examine location 0. Attach probe to U43 pin 6.  () Check that the probe indicates a high state. Single step computer using the front panel switch. When the front panel "out" light goes on, U43 pin 6 should go low.                                                                                                                                                                                                                                                                                                                                    |

| 11. Bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>() Locate and install the following components:</li> <li>() R292.2K ohm 1/4 watt resistor (red, red, red).</li> <li>() U3474LS74 dual type D flip-flop IC.</li> <li>() U1874LS367 hex buffer IC.</li> <li>() U1974LS367 hex buffer IC.</li> <li>() U2074LS368 hex inverter/buffer IC.</li> <li>() U2174LS368 hex inverter/buffer IC.</li> <li>() U1774LS04 hex inverter IC.</li> <li>() U3774LS175 quad latch IC.</li> </ul>                                                                                                                                |

| TestInstall board in test configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| () Set switch position 7 off. Turn power on and hit the reset switch. Front panel lights "MEMR", "M1" and "WO" should be on. (WO will not be on on the ALTAIR 8800b)                                                                                                                                                                                                                                                                                                                                                                                                 |

| () Set switch 7 to on. Front panel lights "WO" and "WAIT" should be on (except 8800b). All data lights are on.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12. Oscillator section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |