8080 Microcomputer Systems Systems Manual September 1975 September

### CONTENTS

| INTRODUCTION                                    |      | CHAPTER 4 -                               |      |

|-------------------------------------------------|------|-------------------------------------------|------|

| General                                         | i    | INSTRUCTION SET                           |      |

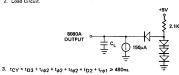

| Advantages of Designing with Microcomputers     | ü    | General                                   | 4-1  |

| Microcomputer Design Aids                       | 111  | Data Transfer Group                       | 4-4  |

| Application Example                             | iii  | Arithmetic Group                          | 4-6  |

| Application Table                               | iv   | Branch Group                              | 4-11 |

| Application rable                               | IV   | Stack, I/O and Machine Control Group      | 4-13 |

| CHAPTER 1 – THE FUNCTIONS OF A COMPUTER         |      | Summary Table                             | 4-15 |

| A Typical Computer System                       | 1-1  | CHAPTER 5 —                               |      |

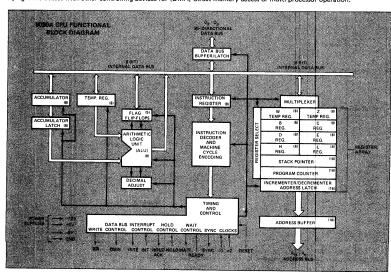

| The Architecture of a CPU                       | 1-1  | 8080 MICROCOMPUTER SYSTEM COMPONENTS      |      |

| Computer Operations                             | 1-3  | CPU Group                                 |      |

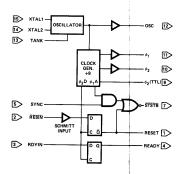

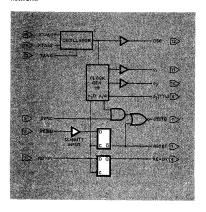

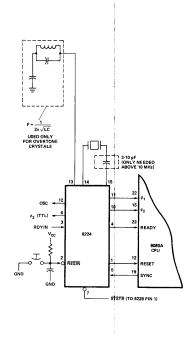

|                                                 | . •  | 8224 Clock Generator                      |      |

| CHAPTER 2 —<br>THE 8080 CENTRAL PROCESSING UNIT |      | Functional Description and                |      |

| General                                         | 2-1  | System Applications                       | 5-1  |

|                                                 |      | Data Sheet                                | 5-4  |

| Architecture of the 8080 CPU                    | 2-2  | 8228 System Controller                    |      |

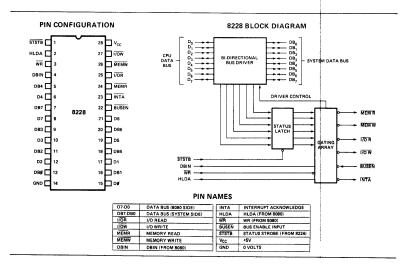

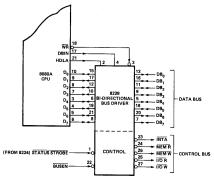

| The Processor Cycle                             | 2-3  | Functional Description and                |      |

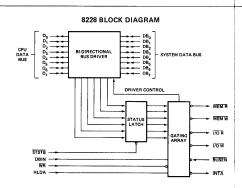

| Interrupt Sequences                             | 2-11 | System Applications                       | 5-7  |

| Hold Sequences                                  |      | Data Sheet                                | 5-11 |

| Halt Sequences                                  |      | 8080A Central Processor                   |      |

| Start-up of the 8080 CPU                        | 2-13 | Data Sheet                                | 5-13 |

| CHAPTER 3 -                                     |      | 8080A-1 Central Processor (1.3μs)         |      |

| INTERFACING THE 8080                            |      | Data Sheet                                | 5-20 |

| General                                         | 3-1  | 8080A-2 Central Processor (1.5µs)         |      |

| Basic System Operation                          | 3-1  | Data Sheet                                | 5-24 |

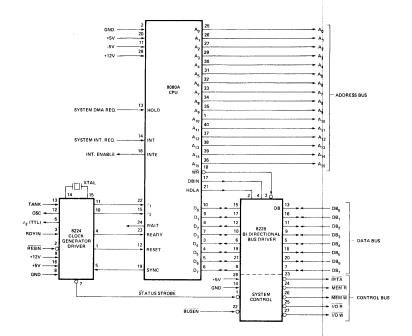

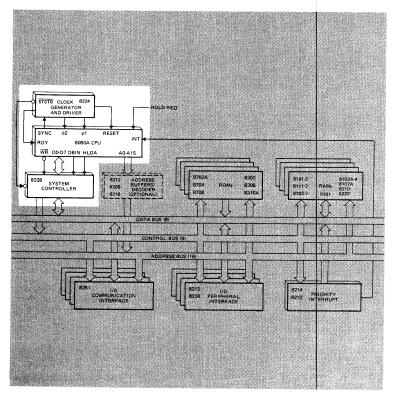

| CPU Module Design                               | 3-2  | M8080A Central Processor (-55° to +125°C) |      |

| Interfacing the 8080 to Memory and              |      | Data Sheet                                | 5-29 |

| I/O Devices                                     | 3.6  |                                           |      |

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied,

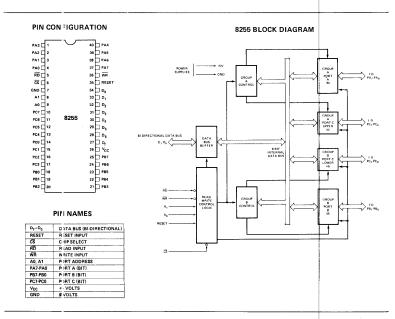

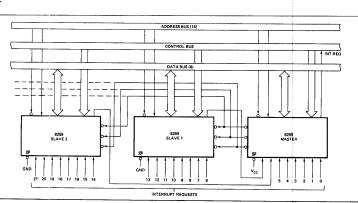

| ROMs                                 | 8255 Programmable Peripheral Interface       |

|--------------------------------------|----------------------------------------------|

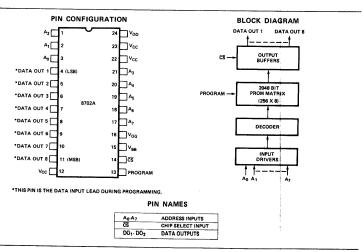

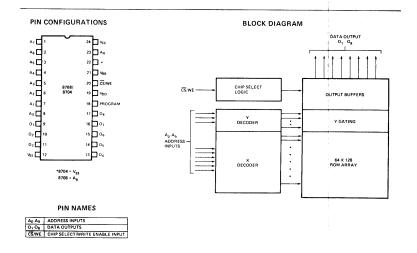

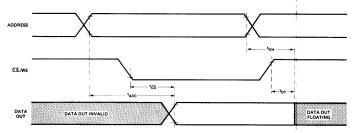

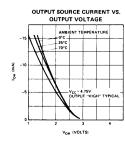

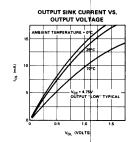

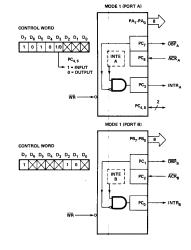

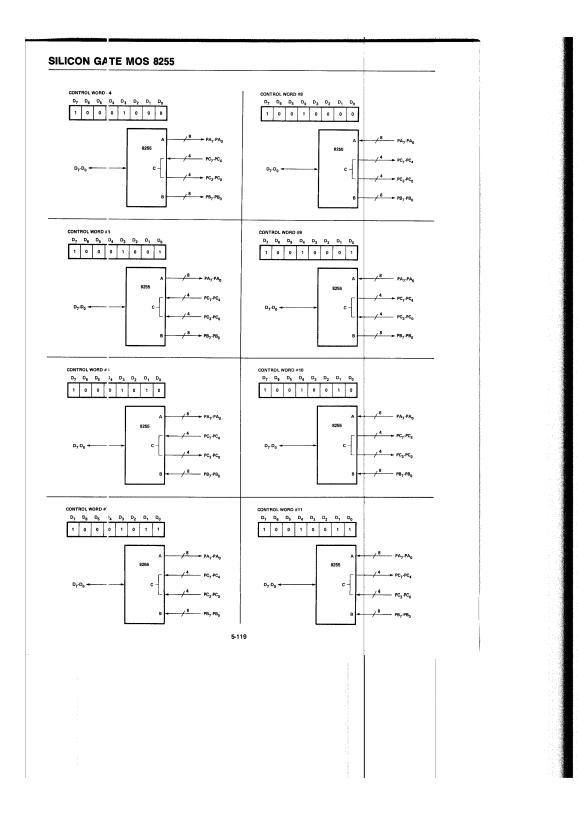

| 8702A Erasable PROM (256 x 8)        | Basic Functional Description 5-113           |

| Data Sheet                           | 37 Detailed Operational Description 5-116    |

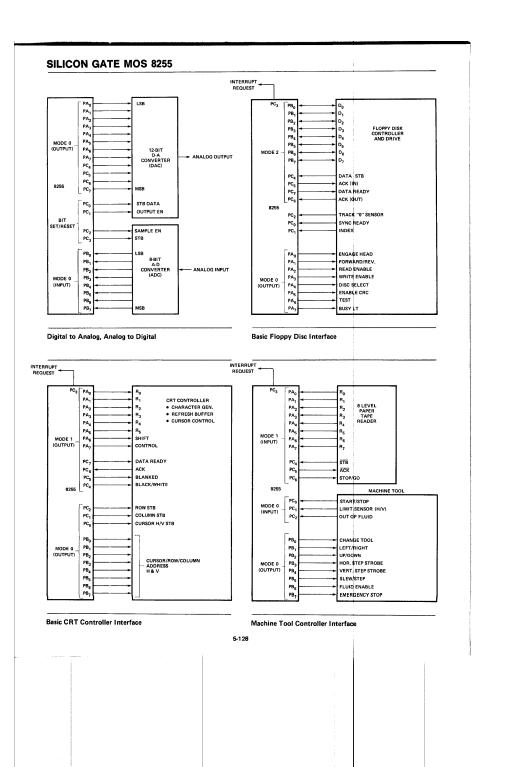

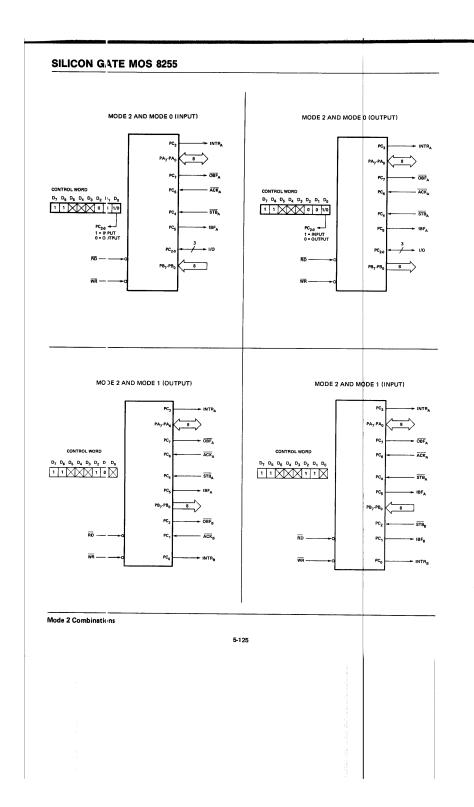

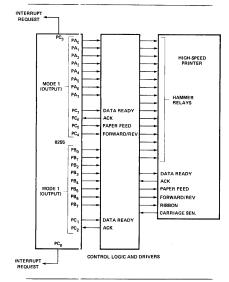

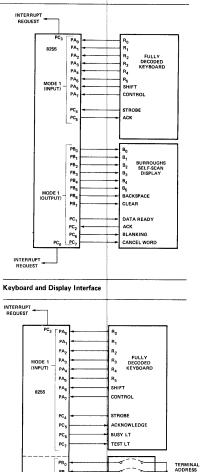

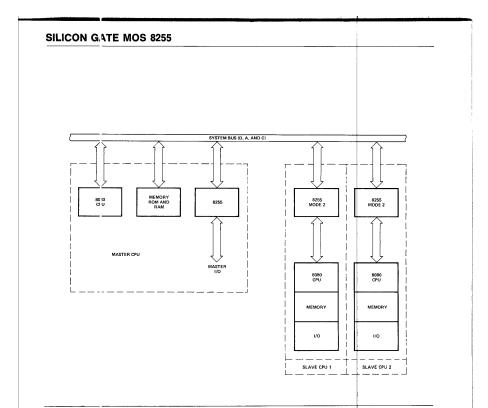

| 8708/8704 Erasable PROM (1K x 8)     | System Applications of the 8255 5-127        |

| Data Sheet                           | 45 Data Sheet                                |

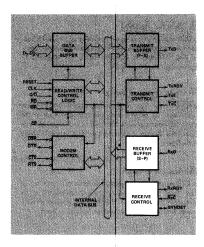

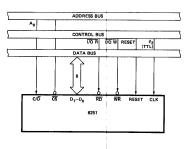

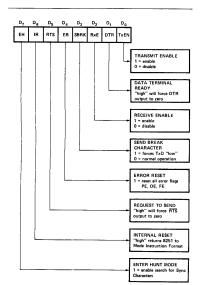

| 8302 Mask ROM (256 x 8)              | 8251 Programmable Communication Interface    |

| Data Sheet                           | 51 Basic Functional Description 5-135        |

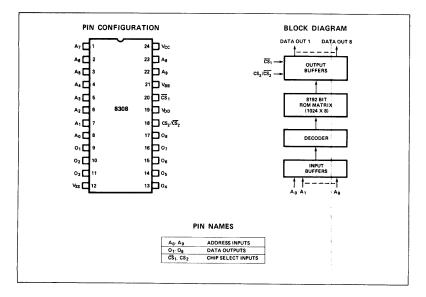

| 8308 Mask ROM (1K x 8)               | Detailed Operational Description 5-139       |

| Data Sheet                           | 59 System Applications of the 8251 5-143     |

| 8316A Mask ROM (2K x 8)              | Data Sheet                                   |

| Data Sheet                           | 61 Peripherals                               |

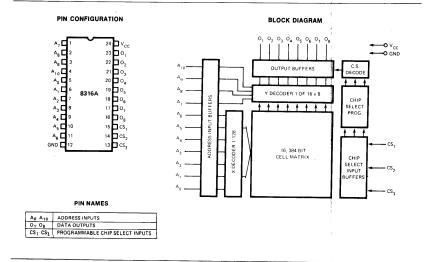

| RAMs                                 | 8205 One of 8 Decoder                        |

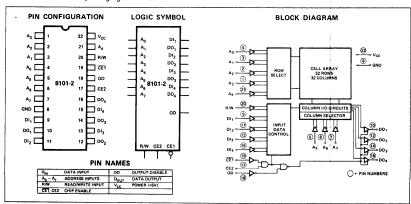

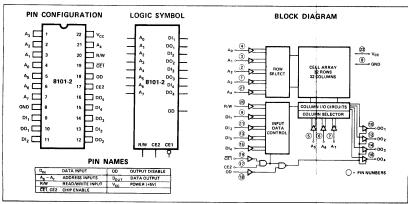

| 8101-2 Static RAM (256 x 4)          | Functional Description 5-147                 |

| Data Sheet                           | 67 System Applications of the 8205 5-149     |

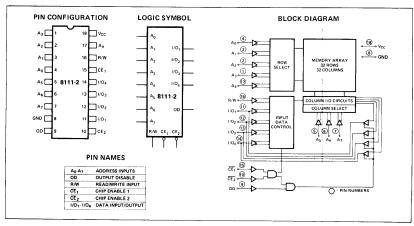

| 8111-2 Static RAM (256 x 4)          | Data Sheet                                   |

| Data Sheet                           | 71 8214 Priority Interrupt Control Unit      |

| 8102-2 Static RAM (1K x 1)           | Interrupts in Microcomputer Systems 5-153    |

| Data Sheet 5-                        | 75 Functional Description 5-155              |

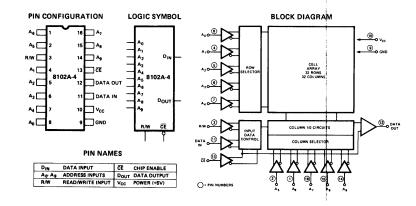

| 8102A-4 Static RAM (1K x 1)          | System Applications of the 8214 5-157        |

| Data Sheet                           | 79 Data Sheet                                |

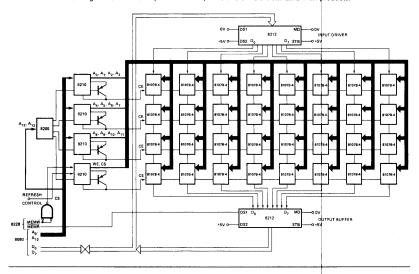

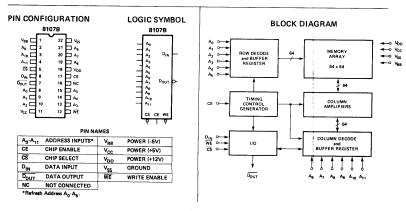

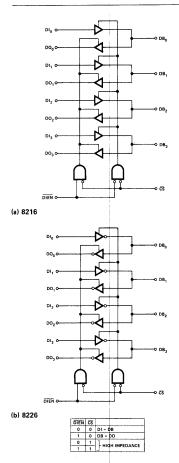

| 8107B-4 Dynamic RAM (4K x 1)         | 8216/8226 4-Bit Bi-Directional Bus Driver    |

| Data Sheet 5-                        | 83 Functional Description 5-163              |

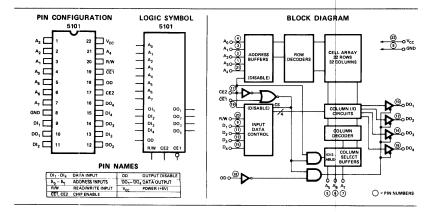

| 5101 Static CMOS RAM (256 x 4)       | System Applications of the 8216/8226 5-165   |

| Data Sheet                           | 91 Data Sheet                                |

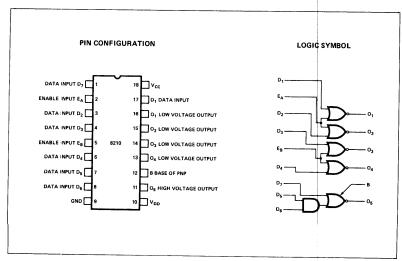

| 8210 Dynamic RAM Driver              | Coming Soon                                  |

| Data Sheet                           | 8253 Programmable Interval Timer 5-169       |

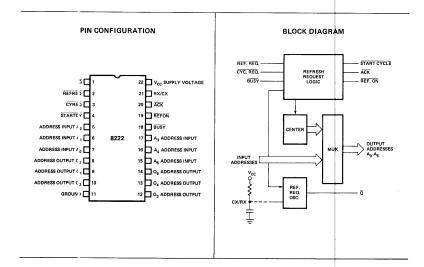

| 8222 Dynamic RAM Refresh Controller  | 0057.0                                       |

| New Product Announcement 5-5         | 8259 Programmable Interrupt Controller 5-173 |

| 1/0                                  | -                                            |

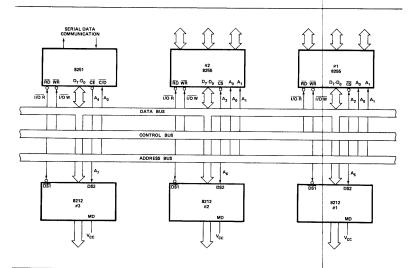

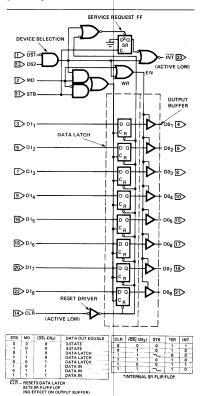

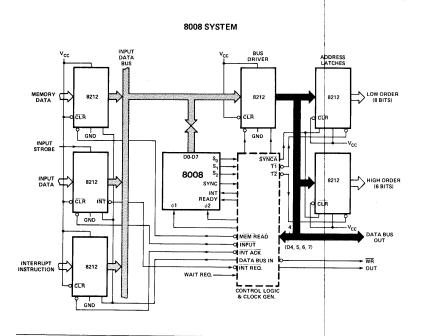

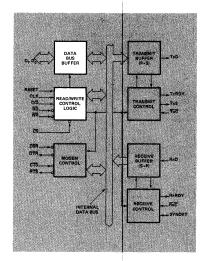

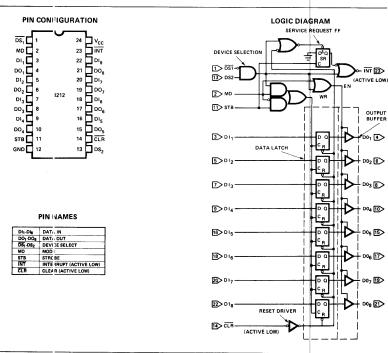

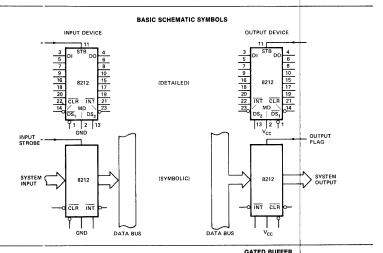

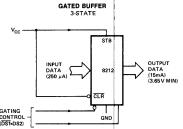

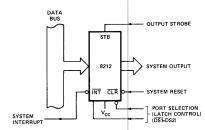

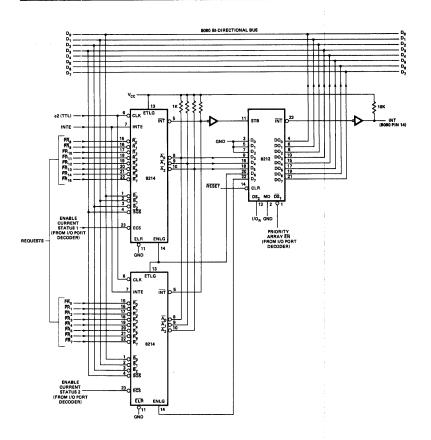

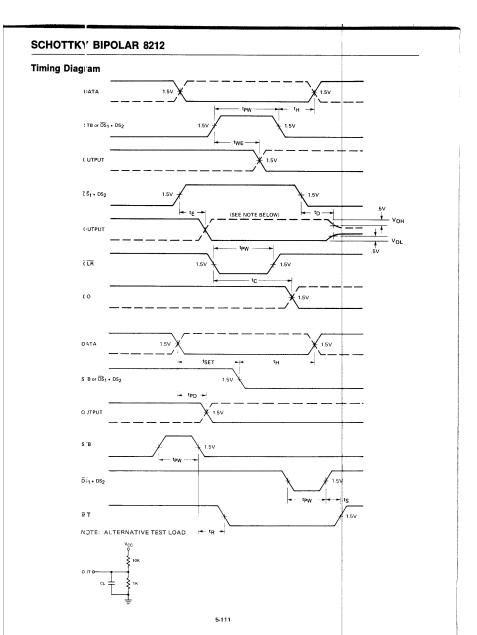

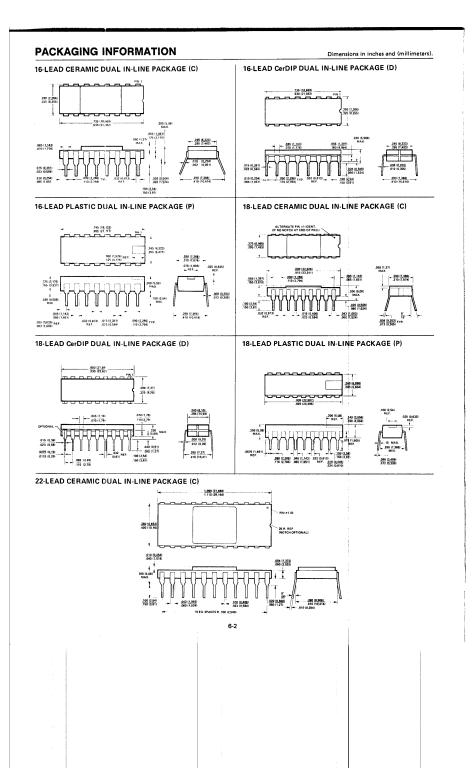

| 8212 8-Bit I/O Port                  | CHAPTER 6 – PACKAGING INFORMATION 6-1        |

| Functional Description 5-10          | 01 FACKAGING INFORMATION 6-1                 |

| System Applications of the 8212 5-10 | 03                                           |

| 0 - 0                                |                                              |

INTRODUCTION

Since their inception, digital computers have continuously become more efficient, expanding into new applications with each major technological improvement. The advent of minicomputers enabled the inclusion of digital computers as a permanent part of various process control systems. Unfortunately, the size and cost of minicomputers in "dedicated" applications has limited their use. Another approach has been the use of custom built systems made up of "random logic" (i.e., logic gates, flip-flops, counters, etc.). However, the huge expense and development time involved in the design and debugging of these systems has restricted their use to large volume applications where the development costs could be spread over a large number of machines.

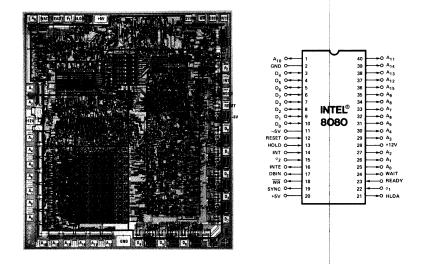

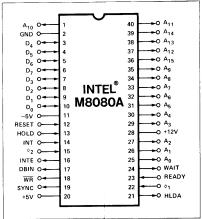

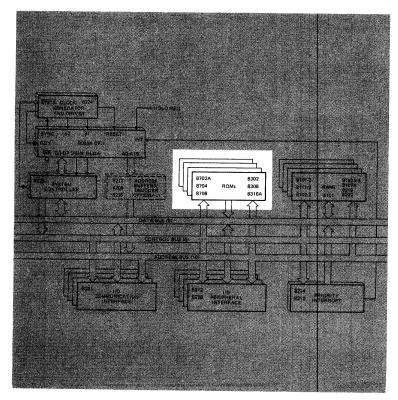

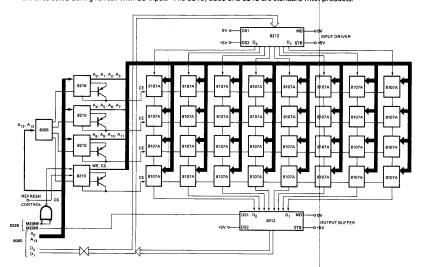

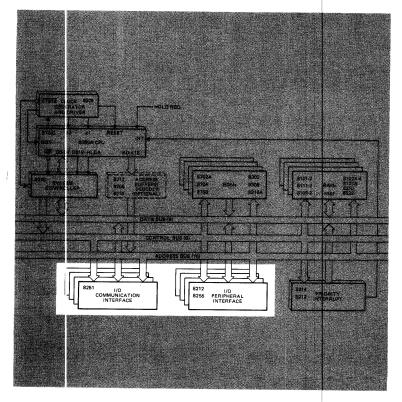

Today, Intel offers the systems designer a new alternative... the microcomputer. Utilizing the technologies and experience gained in becoming the world's largest supplier of LSI memory components, Intel has made the power of the digital computer available at the integrated circuit level. Using the n-channel silicon gate MoS process, Intel engineers have implemented the fast (2  $\mu s$ . cycle) and powerful (72 basic instructions) 8080 microprocessor on a single LSI chip. When this processor is combined with memory and I/O circuits, the computer is complete. Intel offers a variety of analom-access memory (RAM), read-only memory (ROM) as shift register circuits, that combine with the 8080 processor to form the MCS-80 microcomputer system, a system that can directly address and retrieve as many as 65,536 bytes stored in the memory devices.

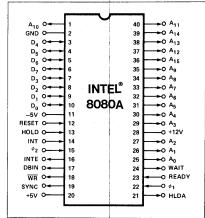

The 8080 processor is packaged in a 40-pin dual in-line package (DIP) that allows for remarkably easy interfacing. The 8080 has a 16-bit address bus, a 8-bit bidirectional data bus and fully decoded, TTL-compatible control outputs. In addition to supporting up to 64K bytes of mixed RAM and ROM memory, the 8080 can address up to 256 input ports and 256 output ports; thus allowing for virtually unlimited system expansion. The 8080 instruction set includes conditional branching, decimal as well as binary arithmetic,

logical, register-to-register, stack pontrol and memory reference instructions. In fact, the 8080 instruction set is powerful enough to rival the performance of many of the much higher priced minicomputers, yet the 8080 is upward software compatible with Intel's earlier 8008 microprocessor (i.e., programs written for the 8008 can be assembled and executed on the 8080.

In addition to an extensive instruction set oriented to problem solving, the 8080 has another significant feature—SPEED. In contrast to random logic designs which tend to work in parallel, the microcomputer works by sequentially executing its program. As a result of this sequential execution, the number of tasks a midrocomputer can undertake in a given period of time is directly proportional to the execution speed of the microcomputer. The speed of execution is the limiting factor of the realm of applications of the microcomputer. The 8080, with instruction times as short as 2 µsec., is an order of magnitude faster than earlier generations of microcomputers, and therefore has an expanded field of potential applications.

The architecture of the 8080 also shows a significant improvement over earlier microdomputer designs. The 8080 contains a 16-bit stack pointer that controls the addressing of an external stack located in memory. The pointer can be initialized via the proper instructions such that any portion of external memory can be used as a last in/first out stack; thus enabling almost unlimited subroutine nesting. The stack pointer allows the contents of the program counter, the accumulator, the condition flags or lany of the data registers to be stored in or retrieved from the external stack. In addition, multi-level interrupt processing is possible using the 8080's stack control instructions. The status of the processor can be "pushed" onto the stack when an interrupt accepted, then "popped" off the stack after the interrupt has been serviced. This ability to save the contents of the processor's registers is possible even if an interrupt service routine, itself, is interrupted.

i

|                         | CONVENTIONAL SYSTEM                           | PROGRAMMED LOGIC                                                    |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------|

| Product definition      |                                               | Simplified because of ease of incorporating features                |

| System and logic design | Done with logic diagrams                      | Can be programmed with design aids (compilers, assemblers, editors) |

| Debug                   | Done with conventional<br>Lab Instrumentation | Software and hardware aids reduce time                              |

| PC card layout          |                                               | Fewer cards to layout                                               |

| Documentation           |                                               | Less hardware to document                                           |

| Cooling and packaging   |                                               | Reduced system size and power consumption eases job                 |

| Power distribution      |                                               | Less power to distribute                                            |

| Engineering changes     | Done with yellow wire                         | Change program                                                      |

Table 0-1. The Advantages of Using Microprocessors

# ADVANTAGES OF DESIGNING WITH MICROCOMPUTERS

Microcomputers simplify almost every phase of product development. The first step, as in any product development. The first step, as in any product development program, is to identify the various functions that the end system is expected to perform. Instead of realizing these functions with networks of gates and flip-flops, the functions are implemented by encoding suitable sequences of instructions (programs) in the memory elements. Data and certain types of programs are stored in RAM, while the basic program can be stored in ROM. The microprocessor performs all of the system's functions by fetching the instructions in memory, executing them and communicating the results via the microcomputer's I/O ports. An 8080 microprocessor, executing the programmed logic stored in a single 2048-byte ROM element, can perform the same logical functions that might have previously required up to 1000 logic gates.

The benefits of designing a microcomputer into your system go far beyond the advantages of merely simplifying product development. You will also appreciate the profitmaking advantages of using a microcomputer in place of custom-designed random logic. The most apparent advantage is the significant savings in hardware costs. A microcomputer chip set replaces dozens of random logic elements, thus reducing the cost as well as the size of your system. In addition, production costs drop as the number of individual components to be handled decreases, and the number of complex printed circuit boards (which are difficult to layout, test and correct) is greatly reduced. Probably the most profitable advantage of a microcomputer is its flexibility for change. To modify your system, you merely re-program the memory elements; you don't have to redesign the entire system. You can imagine the savings in time and money when you want to upgrade your product. Reliability is another reason to choose the microcomputer over random logic. As the number of components decreases, the probability of a malfunctioning element likewise decreases. All

of the logical control functions formerly performed by numerous hardware components can now be implemented in a few ROM circuits which ale non-volatile; that is, the contents of ROM will never be lost, even in the event of a power failure. Table 0.1 summarizes many of the advantages of using microcomputers.

### MICROCOMPUTER DESIGN AIDS

If you're used to logic design and the idea of designing with programmed logic seems like too radical a change, regardless of advantages, there's no need to worry because Intel has already done most of the groundwork for you. The INTELLEC® 8 Development Systems provide flexible, inexpensive and simplified methods for OEM product development. The INTELLEC® 8 provides RAM program storage making program loading and modification easier, a display and control console for system monitoring and debugging, a standard TTY interface, a PRQM programming capability and a standard software package (System Monitor, Assembler and Test Editor). In addition to the standard software package available with the INTELLEC® 8, Intel offers a PL/M compiler, a cross-assembler and a simulator written in FORTRAN IV and designed to run on any large scale computer. These programs may be procured directly from Intel or from a number of nationwide computer time-sharing services. Intel's Microcomputer Systems Group is always available to provide assistance in every phase of your product

Intel also provides complete documentation on all their hardware and software products. In addition to this User's Manual, there are the:

- PL/M Language Reference Manual

- 8080 Assembly Language Programming Manual

INTELLEC® 8/MOD 80 Operator's Manual

- INTELLEC® 8/MOD 80 Operator's Manual

INTELLEC® 8/MOD 80 Hardware Reference

- Manual Manual

- 8080 User's Program Library

#### APPLICATIONS EXAMPLE

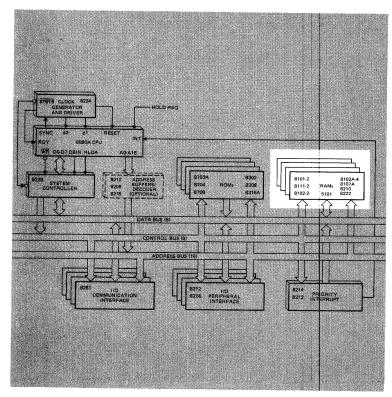

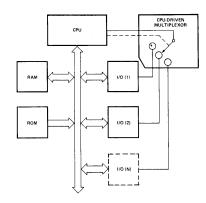

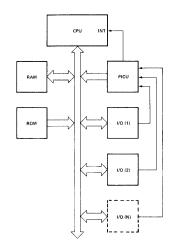

The 8080 can be used as the basis for a wide variety of calculation and control systems. The system configurations for particular applications will differ in the nature of the peripheral devices used and in the amount and the type of memory required. The applications and solutions described in this section are presented primarily to show how microcomputers can be used to solve design problems. The 8080 should not be considered limited either in scope or performance to those applications listed here.

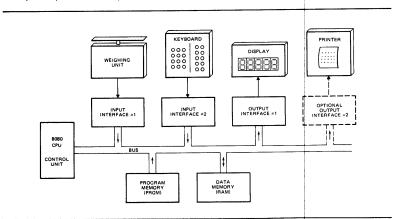

Consider an 8080 microcomputer used within an automatric computing scale for a supermarket. The basic machine has two input devices: the weighing unit and a keyboard, used for function selection and to enter the price per unit of weight. The only output device is a display showing the total price, although a ticket printer might be added as an optional output device.

The control unit must accept weight information from the weighing unit, function and data inputs from the key-board, and generate the display. The only arithmetic function to be performed is a simple multiplication of weight times rate.

The control unit could probably be realized with standard TTL logic. State diagrams for the various portions could be drawn and a multiplier unit designed. The whole design could then be tied together, and eventually reduced to a selection of packages and a printed circuit board layout. In effect, when designing with a logic family such as TTL, the designs are "customized" by the choice of packages and the wiring of the logic.

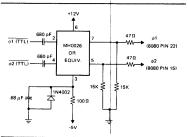

If, however, an 8080 microcomputer is used to realize

the control unit (as shown in Figure 0-1), the only "custom" logic will be that of the interface circuits. These circuits are usually quite simple, providing electrical buffering for the input and output signals.

Instead of drawing state diagrams leading to logic, the system designer now prepares a flow chart, indicating which input signals must be read, what processing and computations are needed, and what output signals must be produced. A program is written from the flow chart. The program is then assembled into bit patterns which are loaded into the program memory. Thus, this system is customized primarily by the contents of program memory.

For this automatic scale, the program would probably reside in read-only memory (ROM), since the microcomputer would always execute the same program, the one which implements the scale functions. The processor would constantly monitor the keyboard and weighing unit, and update the display whenever necessary. The unit would require very little data memory; it would only be needed for rate storage, intermediate results, and for storing a copy of the display.

When the control portion of a product is implemented with a microcomputer chip set, functions can be changed and features added merely by altering the program in memory. With a TTL based system, however, alterations may require extensive rewiring, alteration of PC boards, etc.

The number of applications for microcomputers is limited only by the depth of the designer's imagination. We have listed a few potential applications in Table 0-2, along with the types of peripheral devices usually associated with each product.

Figure 0-1. Microcomputer Application - Automatic Scale

with a clearly defined activity is called a **State**. And the interval between pulses of the timing oscillator is referred to as a **Clock Period**. As a general rule, one or more clock periods are necessary for the completion of a state, and there are several states in a cycle.

#### Instruction Fetch:

The first state(s) of any instruction cycle will be dedicated to fetching the next instruction. The CPU issues a read signal and the contents of the program counter are sent to memory, which responds by returning the next instruction word. The first byte of the instruction is placed in the instruction register. If the instruction consists of more than one byte, additional states are required to fetch each byte of the instruction. When the entire instruction is present in the CPU, the program counter is incremented (in preparation for the next instruction fetch) and the instruction is decoded. The operation specified in the instruction will be executed in the remaining states of the instruction cycle. The instruction may call for a memory read or write, an input or output and/or an internal CPU operation, such as a register-to-register transfer or an add-registers operation.

#### Memory Read:

An instruction fetch is merely a special memory read operation that brings the instruction to the CPU's instruction register. The instruction fetched may then call for data to be read from memory into the CPU. The CPU again issues a read signal and sends the proper memory address; memory responds by returning the requested word. The data received is placed in the accumulator or one of the other general purpose registers (not the instruction register).

#### Memory Write:

A memory write operation is similar to a read except for the direction of data flow. The CPU issues a write signal, sends the proper memory address, then sends the data word to be written into the addressed memory location.

### Wait (memory synchronization):

As previously stated, the activities of the processor are timed by a master clock oscillator. The clock period determines the timing of all processing activity.

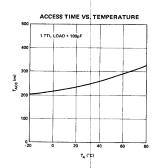

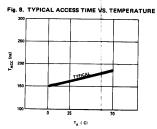

The speed of the processing cycle, however, is limited by the memory's Access Time. Once the processor has sent a read address to memory, it cannot proceed until the memory has had time to respond. Most memories are capable of responding much faster than the processing cycle requires. A few, however, cannot supply the addressed byte within the minimum time established by the processor's clock.

Therefore a processor should contain a synchronization provision, which permits the memory to request a Wait state. When the memory receives a read or write enable signal, it places a request signal on the processor's READY line, causing the CPU to idle temporarily. After the memory has had time to respond, it frees the processor's READY line, and the instruction cycle proceeds.

### Input/Output:

Input and Output operations are similar to memory read and write operations with the exception that a peripheral I/O device is addressed instead of a memory location. The CPU issues the appropriate input or output control signal, sends the proper device address and either receives the data being input or sends the data to be output.

Data can be input/output in either parallel or serial form. All data within a digital computer is represented in binary coded form. A binary data word consists of a group of bits; each bit is either a one or a zero. Parallel I/O consists of transferring all bits in the word at the same time, one bit per line. Serial I/O consists of transferring one bit at a time on a single line. Naturally serial I/O is much slower, but it requires considerably less hardware than does parallel I/O.

#### Interrupts:

Interrupt provisions are included on many central processors, as a means of improving the processor's efficiency. Consider the case of a computer that is processing a large volume of data, portions of which are to be output to a printer. The CPU can output a byte of data within a single machine cycle but it may take the printer the equivalent of many machine cycles to actually print the character specified by the data byte. The CPU could then remain idle waiting until the printer can accept the next data byte. If an interrupt capability is implemented on the computer, the CPU can output a data byte then return to data processing. When the printer is ready to accept the next data byte, it can request an interrupt. When the CPU acknowledges the interrupt, it suspends main program execution and automatically branches to a routine that will output the next data byte. After the byte is output, the CPU continues with main program execution. Note that this is, in principle, quite similar to a subroutine call except that the jump is initiated externally rather than by the program.

More complex interrupt structures are possible, in which several interrupting devices share the same processor but have different priority levels, interruptive processing is an important feature that enables maximum untilization of a processor's capacity for high system throughput.

### Hold:

Another important feature that improves the throughput of a processor is the Hold. The hold provision enables Direct Memory Access (DMA) operations.

In ordinary input and output operations, the processor itself supervises the entire data transfer. Information to be placed in memory is transferred from the input device to the processor, and then from the processor to the designated memory location. In similar fashion, information that goes

CHAPTER TONE

THE FUNCTUTER

OF A COMPUTER

This chapter introduces certain basic computer concepts. It provides background information and definitions which will be useful in later chapters of this manual. Those already familiar with computers may skip this material, at their option.

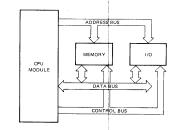

### A TYPICAL COMPUTER SYSTEM

A typical digital computer consists of:

- a) A central processor unit (CPU)

- b) A memory

- c) Input/output (I/O) ports

The memory serves as a place to store **Instructions**, the coded pieces of information that direct the activities of the CPU, and **Data**, the coded pieces of information that are processed by the CPU. A group of logically related instructions stored in memory is referred to as a **Program**. The CPU "reads" each instruction from memory in a logically determined sequence, and uses it to initiate processing actions. If the program sequence is coherent and logical, processing the program will produce intelligible and useful results.

The memory is also used to store the data to be manipulated, as well as the instructions that direct that manipulation. The program must be organized such that the CPU does not read a non-instruction word when it expects to see an instruction. The CPU can rapidly access any data stored in memory; but often the memory is not large enough to store the entire data bank required for a particular application. The problem can be resolved by providing the computer with one or more Input Ports. The CPU can address these ports and input the data contained there. The addition of input ports enables the computer to receive information from external equipment (such as a paper tape reader of loppy disk) at high rates of speed and in large volumes.

A computer also requires one or more **Output Ports** that permit the CPU to communicate the result of its processing to the outside world. The output may go to a display, for use by a human operator, to a peripheral device that produces "hard-copy," such as a line-printer, to a

peripheral storage device, such as a floppy disk unit, or the output may constitute process control signals that direct the operations of another system, such as an automated assembly line. Like input ports, output ports are addressable. The input and output ports together permit the processor to communicate with the outside world.

The CPU unifies the system. It controls the functions performed by the other components. The CPU must be able to fetch instructions from memory, decode their binary contents and execute them. It must also be able to reference memory and I/O ports as necessary in the execution of instructions. In addition, the CPU should be able to recognize and respond to certain external control signals, such as INTERRUPT and WAIT requests. The functional units within a CPU that enable it to perform these functions are described below.

#### THE ARCHITECTURE OF A CPU

A typical central processor unit (CPU) consists of the following interconnected functional units:

- Registers

- Arithmetic/Logic Unit (ALU)

- Control Circuitry

Registers are temporary storage units within the CPU. Some registers, such as the program counter and instruction register, have dedicated uses. Other registers, such as the accumulator, are for more general purpose use.

### Accumulator:

The accumulator usually stores one of the operands to be manipulated by the ALU. A typical instruction might direct the ALU to add the contents of some other register to the contents of the accumulator and store the result in the accumulator itself. In general, the accumulator is both a source (operand) and a destination (result) register.

Often a CPU will include a number of additional general purpose registers that can be used to store operands or intermediate data. The availability of general purpose

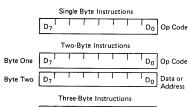

**Code** or **Operation Code**. An eight-bit word used as an instruction code can distinguish between 256 alternative actions, more than adequate for most processors.

The processor fetches an instruction in two distinct operations. First, the processor transmits the address in its Program Counter to the memory. Then the memory returns the addressed byte to the processor. The CPU stores this instruction byte in a register known as the Instruction Register, and uses it to direct activities during the remainder of the instruction execution.

The mechanism by which the processor translates an instruction code into specific processing actions requires more elaboration than we can here afford. The concept, however, should be intuitively clear to any logic designer. The eight bits stored in the instruction register can be decoded and used to selectively activate one of a number of output lines, in this case up to 256 lines. Each line represents a set of activities associated with execution of a particular instruction code. The enabled line can be combined with selected timing pulses, to develop electrical signals that can then be used to initiate specific actions. This translation of code into action is performed by the Instruction Decoder and by the associated control circuitry.

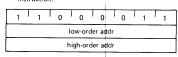

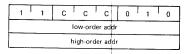

An eight-bit instruction code is often sufficient to specify a particular processing action. There are times, however, when execution of the instruction requires more information than eight bits can convey.

One example of this is when the instruction references a memory location. The basic instruction code identifies the operation to be performed, but cannot specify the object address as well. In a case like this, a two- or three-byte instruction must be used. Successive instruction bytes are stored in sequentially adjacent memory locations, and the processor performs two or three fetches in succession to obtain the full instruction. The first byte retrieved from memory is placed in the processor's instruction register, and subsequent bytes are placed in temporary storage; the processor then proceeds with the execution phase. Such an instruction is referred to as Variable Length.

### Address Register(s):

A CPU may use a register or register-pair to hold the address of a memory location that is to be accessed for data. If the address register is Programmable, (i.e., if there are instructions that allow the programmer to alter the contents of the register) the program can "build" an address in the address register prior to executing a Memory Reference instruction (i.e., an instruction that reads data from memory, writes data to memory or operates on data stored in memory).

### Arithmetic/Logic Unit (ALU):

All processors contain an arithmetic/logic unit, which is often referred to simply as the ALU. The ALU, as its name implies, is that portion of the CPU hardware which

performs the arithmetic and logical operations on the binary data.

The ALU must contain an combining the contents of two registers in accordance with the logic of binary arithmetic. This provision permits the processor to perform arithmetic manipulations on the data it obtains from memory and from its other inputs.

Using only the basic adder a capable programmer can write routines which will subtrast, multiply and divide, giving the machine complete arithmetic capabilities. In practice, however, most ALUs provide other built-in functions, including hardware subtraction, bdolean logic operations, and shift capabilities.

The ALU contains Flag Bits which specify certain conditions that arise in the course of arithmetic and logical manipulations. Flags typically include Carry, Zero, Sign, and Parity. It is possible to program jumps which are conditionally dependent on the status of one or more flags. Thus, for example, the program may be designed to jump to a special routine if the carry bit is set following an addition instruction.

#### Control Circuitry:

The control circuitry is the primary functional unit within a CPU. Using clock inputs, the control circuitry maintains the proper sequence of events required for any processing task. After an instruction is fetched and decoded, the control circuitry issues the appropriate signals (to units both internal and external to the CPU) for initiating the proper processing action. Often the control circuitry will be capable of responding to external signals, such as an interrupt or wait request. An Interrupt request will cause the control circuitry to temporarily interrupt main program execution, jump to a special routihe to service the interrupting device, then automatically return to the main program. A Wait request is often issued by a memory or I/O element that operates slower than the CPU. The control circuitry will idle the CPU until the memory or I/O port is ready with the data.

### COMPUTER OPERATIONS

There are certain operations that are basic to almost any computer. A sound understanding of these basic operations is a necessary prerequisite to examining the specific operations of a particular computer.

### Timing

The activities of the central processor are cyclical. The processor fetches an instruction performs the operations required, fetches the next instruction, and so on. This orderly sequence of events requires precise timing, and the CPU therefore requires a free running oscillator clock which furnishes the reference for all processor actions. The combined fetch and execution of a single instruction is referred to as an Instruction Cycle. The portion of a cycle identified

be synchronized with the pulses of the driving clock. Thus, the duration of all states are integral multiples of the clock period.

To summarize then, each clock period marks a state; three to five states constitute a machine cycle; and one to five machine cycles comprise an instruction cycle. A full instruction cycle requires anywhere from four to eight-teen states for its completion, depending on the kind of instruction involved.

#### Machine Cycle Identification:

With the exception of the DAD instruction, there is just one consideration that determines how many machine cycles are required in any given instruction cycle: the number of times that the processor must reference a memory address or an addressable peripheral device, in order to fetch and execute the instruction. Like many processors, the 8080 is so constructed that it can transmit only one address per machine cycle. Thus, if the fetch and execution of an instruction requires two memory references, then the instruction cycle associated with that instruction consists of two machine cycles. If five such references are called for, then the instruction cycle contains five machine cycles.

Every instruction cycle has at least one reference to memory, during which the instruction is fetched. An instruction cycle must always have a fetch, even if the execution of the instruction requires no further references to memory. The first machine cycle in every instruction cycle is therefore a FETCH. Beyond that, there are no fast rules. It depends on the kind of instruction that is fetched.

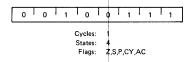

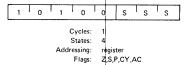

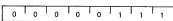

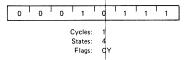

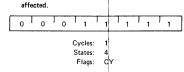

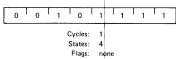

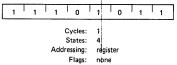

Consider some examples. The add-register (ADD r) instruction is an instruction that requires only a single machine cycle (FETCH) for its completion. In this one-byte instruction, the contents of one of the CPU's six general purpose registers is added to the existing contents of the accumulator. Since all the information necessary to execute the command is contained in the eight bits of the instruction code, only one memory reference is necessary. Three states are used to extract the instruction from memory, and one additional state is used to accomplish the desired addition. The entire instruction cycle thus requires only one machine cycle that consists of four states, or four periods of the external clock.

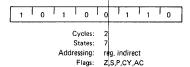

Suppose now, however, that we wish to add the contents of a specific memory location to the existing contents of the accumulator (ADD M). Although this is quite similar in principle to the example just cited, several additional steps will be used. An extra machine cycle will be used, in order to address the desired memory location.

The actual sequence is as follows. First the processor extracts from memory the one-byte instruction word addressed by its program counter. This takes three states. The eight-bit instruction word obtained during the FETCH machine cycle is deposited in the CPU's instruction register and used to direct activities during the remainder of the instruction cycle. Next, the processor sends out, as an address,

the contents of its H and L registers. The eight-bit data word returned during this MEMORY READ machine cycle is placed in a temporary register inside the 8080 CPU. By now three more clock periods (states) have elapsed. In the seventh and final state, the contents of the temporary register are added to those of the accumulator. Two machine cycles, consisting of seven states in all, complete the "ADD M" instruction cycle.

At the opposite extreme is the save H and L registers (SHLD) instruction, which requires five machine cycles. During an "SHLD" instruction cycle, the contents of the processor's H and L registers are deposited in two sequentially adjacent memory locations; the destination is indicated by two address bytes which are stored in the two memory locations immediately following the operation code byte. The following sequence of events occurs:

- (1) A FETCH machine cycle, consisting of four states. During the first three states of this machine cycle, the processor fetches the instruction indicated by its program counter. The program counter is then incremented. The fourth state is used for internal instruction decoding.

- (2) A MEMORY READ machine cycle, consisting of three states. During this machine cycle, the byte indicated by the program counter is read from memory and placed in the processor's Z register. The program counter is incremented again.

- (3) Another MEMORY READ machine cycle, consisting of three states, in which the byte indicated by the processor's program counter is read from memory and placed in the W register. The program counter is incremented, in anticipation of the next instruction fetch.

- (4) A MEMORY WRITE machine cycle, of three states, in which the contents of the L register are transferred to the memory location pointed to by the present contents of the W and Z registers. The state following the transfer is used to increment the W.Z register pair so that it indicates the next memory location to receive data.

- (5) A MEMORY WRITE machine cycle, of three states, in which the contents of the H register are transferred to the new memory location pointed to by the W, Z register pair.

In summary, the "SHLD" instruction cycle contains five machine cycles and takes 16 states to execute.

Most instructions fall somewhere between the extremes typified by the "ADD r" and the "SHLD" instructions. The input (INP) and the output (OUT) instructions, for example, require three machine cycles: a FETCH, to obtain the instruction; a MEMORY READ, to obtain the address of the object peripheral; and an INPUT or an OUT-PUT machine cycle, to complete the transfer.

from memory to output devices goes by way of the processor.  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

Some peripheral devices, however, are capable of transferring information to and from memory much faster than the processor itself can accomplish the transfer. If any appreciable quantity of data must be transferred to or from such a device, then system throughput will be increased by

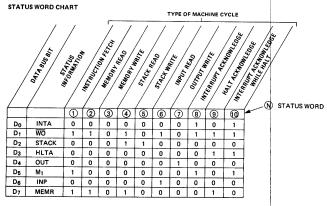

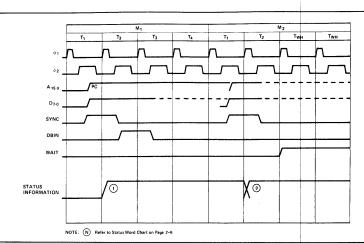

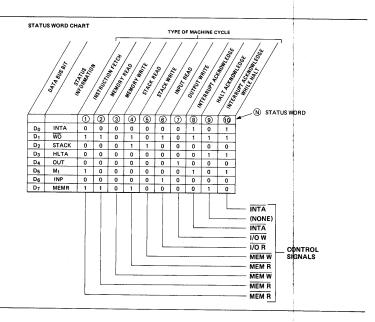

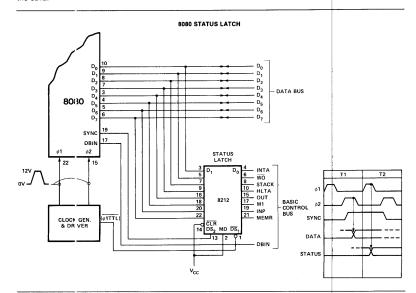

having the device accomplish the transfer directly. The processor must temporarily suspend its operation during such a transfer, to prevent conflicts that would arise if processor and peripheral device attempted to access memory simultaneously. It is for this reason that a **hold** provision is included on some processors. Instructions for the 8080 require from one to five machine cycles for complete execution. The 8080 sends out 8 bit of status information on the data bus at the beginning of sech machine cycle (during SYNC time). The following table defines the status information.

STATUS INFORMATION DEFINITION

|                | STATUS         | INFORMATION DEFINITION                                                                                                                                                                    |

|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Data Bus       |                                                                                                                                                                                           |

| Symbols        | Bit            | Definition                                                                                                                                                                                |

| INTA*          | D <sub>0</sub> | Acknowledge signal for INTERRUPT request. Signal should be used to gate a restart instruction onto the data bus when DBIN is active.                                                      |

| wo             | D <sub>1</sub> | Indicates that the operation in the current machine cycle will be a WRITE memory or OUTPUT function ( $\overline{WO}$ = 0). Otherwise, a READ memory or INPUT operation will be executed. |

| STACK          | D <sub>2</sub> | Indicates that the address bus holds the pushdown stack address from the Stack Pointer.                                                                                                   |

| HLTA           | $D_3$          | Acknowledge signal for HALT instruction.                                                                                                                                                  |

| оит            | D <sub>4</sub> | Indicates that the address bus contains the address of an output device and the data bus will contain the output data when $\overline{WR}$ is active.                                     |

| M <sub>1</sub> | D <sub>5</sub> | Provides a signal to indicate that the CPU is in the fetch cycle for the first byte of an instruction.                                                                                    |

| INP*           | D <sub>6</sub> | Indicates that the address bus contains the address of an input device and the input data should be placed on the data bus when DBIN is active.                                           |

| MEMR*          | $D_7$          | Designates that the data bus will be used for memory read data.                                                                                                                           |

<sup>\*</sup>These three status bits can be used to control the flow of data onto the 8080 data bus.

Table 2-1. 8080 Status Bit Definitions

CHAPTER 2 THE 8080 CENTRAL THE 8080 CENTRAL PROCESSOR UNIT

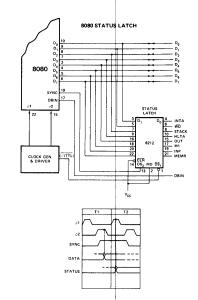

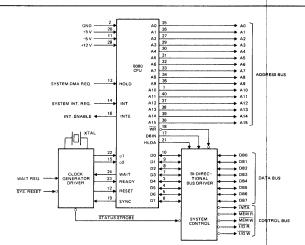

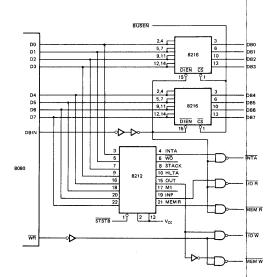

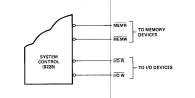

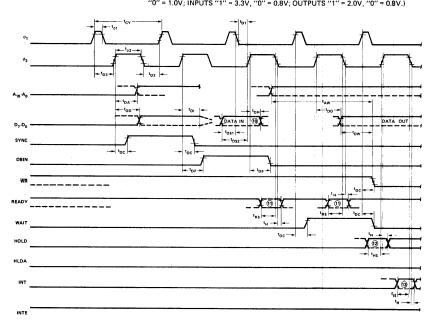

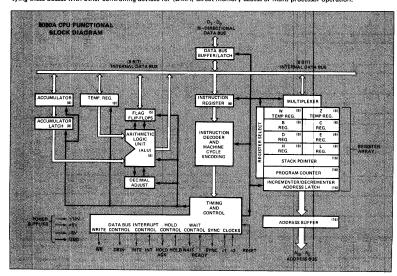

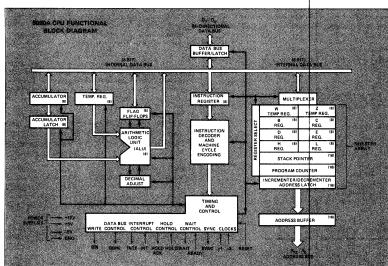

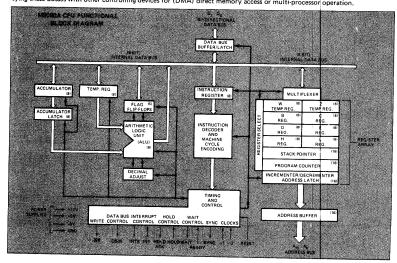

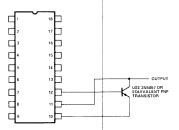

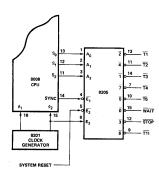

The 8080 is a complete 8-bit parallel, central processor unit (CPU) for use in general purpose digital computer systems. It is fabricated on a single LSI chip (see Figure 3-1). using Intel's n-channel silicon gate MOS process. The 8080 transfers data and internal state information via an 8-bit, bidirectional 3-state Data Bus (Dq-Dq). Memory and peripheral device addresses are transmitted over a separate 16-

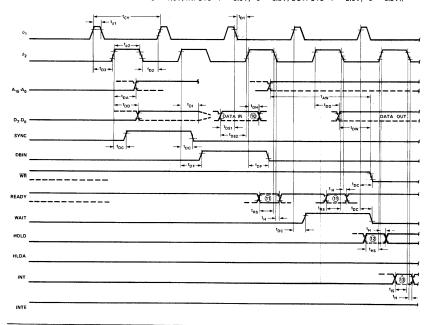

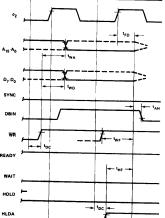

bit 3-state Address Bus (A<sub>0</sub>-A<sub>1</sub>b). Six timing and control outputs (SYNC, DBIN, WAIT,  $\overline{WR}$ , HLDA and INTE) emanate from the 8080, while four HOLD, INT and RESET), four power inputs (READY, HOLD, INT and two clock inputs ( $\phi$ 1 and  $\phi$ 2) are accepted by the 8080.

Figure 2-1. 8080 Photomicrograph With Pin Designations

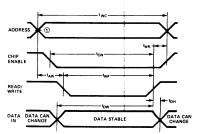

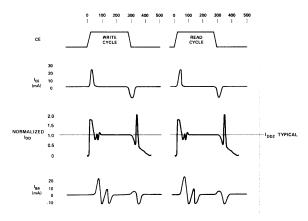

The events that take place during the T<sub>3</sub> state are determined by the kind of machine cycle in progress. In a FETCH machine cycle, the processor interprets the data on its data bus as an instruction. During a MEMORY READ or a STACK READ, data on this bus is interpreted as a data word. The processor outputs data on this bus during a MEMORY WRITE machine cycle. During I/O operations, the processor may either transmit or receive data, depending on whether an OUTPUT or an INPUT operation is involved.

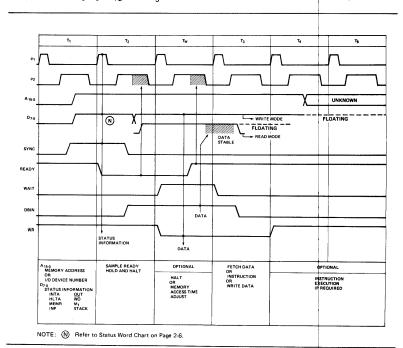

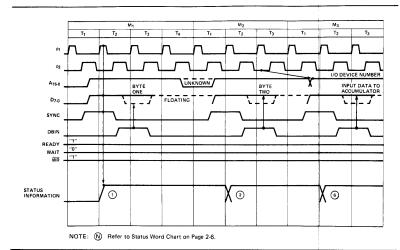

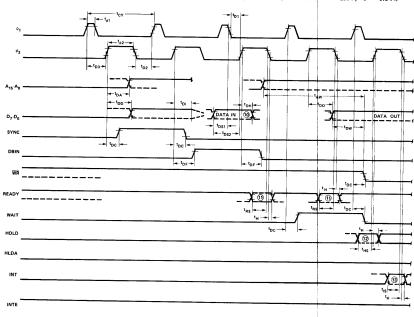

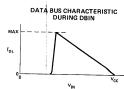

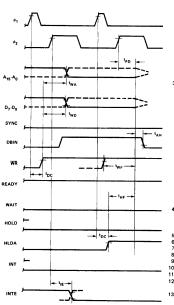

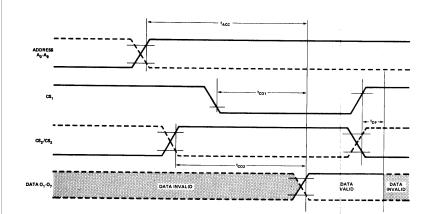

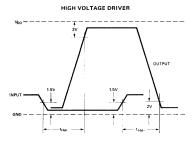

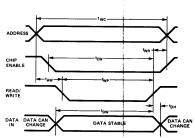

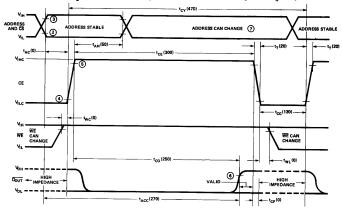

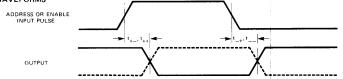

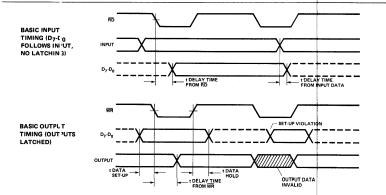

Figure 2-6 illustrates the timing that is characteristic of a data input operation. As shown, the low-to-high transition of  $\phi_2$  during T2 clears status information from the processor's data lines, preparing these lines for the receipt of incoming data. The data presented to the processor must have stabilized prior to both the " $\phi_1$ —data set-up" interval (tDS1), that precedes the falling edge of the  $\phi_1$  pulse defining state T3, and the " $\phi_2$ —data set-up" interval (tDS2), that precedes the rising edge of  $\phi_2$  in state T3. This same

data must remain stable during the "data hold" interval  $\{tp_H\}$  that occurs following the rising edge of the  $\phi_2$  pulse. Data placed on these lines by memory or by other external devices will be sampled during  $T_3$ ;

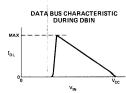

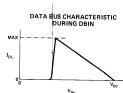

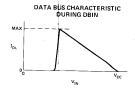

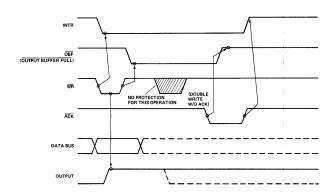

During the input of data to the processor, the 8080 generates a DBIN signal which should be used externally to enable the transfer. Machine cycles in which DBIN is available include: FETCH, MEMORY READ, STACK READ, and INTERRUPT. DBIN is initiated by the rising edge of  $\phi_2$  during state T2 and terminated by the corresponding edge of  $\phi_2$  during T3. Any Ty phases intervening between T2 and T3 will therefore extend DBIN by one or more clock periods.

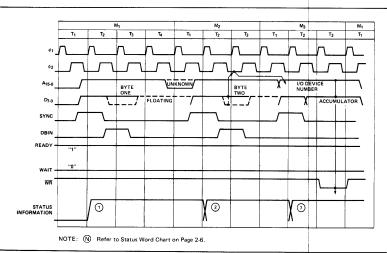

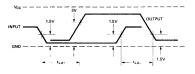

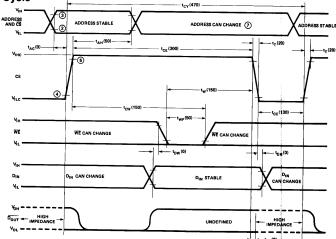

Figure 2.7 shows the timing of a machine cycle in which the processor outputs data. Output data may be destined either for memory or for peripherals. The rising edge of  $\phi_2$  within state T2 clears stafus information from the CPU's data lines, and loads in the data which is to be output to external devices. This substitution takes place within the

Figure 2-5. Basic 8080 Instruction Cycle

### Arithmetic and Logic Unit (ALU):

The ALU contains the following registers:

- An 8-bit accumulator

- · An 8-bit temporary accumulator (ACT)

- A 5-bit flag register: zero, carry, sign, parity and auxiliary carry

- An 8-bit temporary register (TMP)

Arithmetic, logical and rotate operations are performed in the ALU. The ALU is fed by the temporary register (TMP) and the temporary accumulator (ACT) and carry flip-flop. The result of the operation can be transferred to the internal bus or to the accumulator; the ALU also feeds the flag register.

The temporary register (TMP) receives information from the internal bus and can send all or portions of it to the ALU, the flag register and the internal bus.

The accumulator (ACC) can be loaded from the ALU and the internal bus and can transfer data to the temporary accumulator (ACT) and the internal bus. The contents of the accumulator (ACC) and the auxiliary carry flip-flop can be tested for decimal correction during the execution of the DAA instruction (see Chapter 4).

### Instruction Register and Control:

During an instruction fetch, the first byte of an instruction (containing the OP code) is transferred from the internal bus to the 8-bit instruction register.

The contents of the instruction register are, in turn, available to the instruction decoder. The output of the decoder, combined with various timing signals, provides the control signals for the register array, ALU and data buffer blocks. In addition, the outputs from the instruction decoder and external control signals feed the timing and state control section which generates the state and cycle timing signals.

### Data Bus Buffer:

This 8-bit bidirectional 3-state buffer is used to isolate the CPU's internal bus from the external data bus (D<sub>0</sub> through D<sub>7</sub>). In the output mode, the internal bus content is loaded into an 8-bit latch that, in turn, drives the data bus output buffers. The output buffers are switched off during input or non-transfer operations.

During the input mode, data from the external data bus is transferred to the internal bus. The internal bus is pre-charged at the beginning of each internal state, except for the transfer state (T3—described later in this chapter).

#### THE PROCESSOR CYCLE

An instruction cycle is defined as the time required to fetch and execute an instruction. During the fetch, a selected instruction (one, two or three bytes) is extracted from memory and deposited in the CPU's instruction register. During the execution phase, the instruction is decoded and translated into specific processing activities.

Every instruction cycle consists of one, two, three, four or five machine cycles. A machine cycle is required each time the CPU accesses memiory or an I/O port. The fetch portion of an instruction cycle requires one machine cycle for each byte to be fetched. The duration of the execution portion of the instruction cycle depends on the kind of instruction that has been fetched. Some instructions do not require any machine cycles other than those necessary to fetch the instruction; other instructions, however, require additional machine cycles to write or read data to/from memory or I/O devices. The DAD instruction is an exception in that it requires two additional machine cycles to complete an internal register-pair add (see Chapter 4).

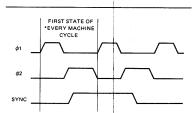

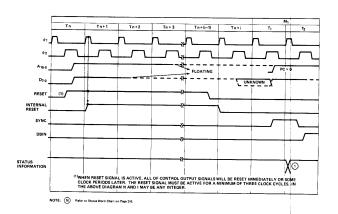

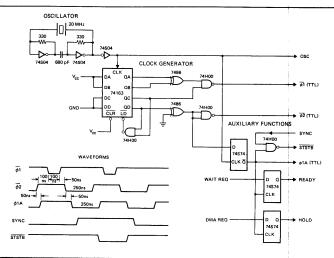

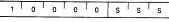

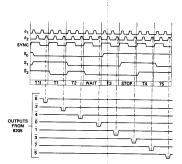

Each machine cycle consists of three, four or five states. A state is the smallest unit of processing activity and is defined as the interval between two successive positive-going transitions of the \$\phi\_1\$ driven clock pulse. The 8080 is driven by a two-phase clock oscillator. All processing activities are referred to the period of this clock. The two non-overlapping clock pulses, labeled \$\phi\_1\$ and \$\phi\_2\$, are furnished by external circuitry. It is the \$\phi\_1\$ clock pulse which divides each machine cycle into states. Timing logic within the 8080 uses the clock inputs to produce a SYNC pulse, which identifies the beginning of every machine cycle. The SYNC pulse is triggered by the low-to-high transition of \$\phi\_2\$, as shown in Figure 2-3.

\*SYNC DOES NOT OCCUR IN THE SECOND AND THIRD MACHINE CYCLES OF A DAD INSTRUCTION SINCE THESE MACHINE CYCLES ARE USED FOR AN INTERNAL REGISTER-PAIR ADD.

### Figure 2-3. $\phi_1, \phi_2$ And SYNC Timing

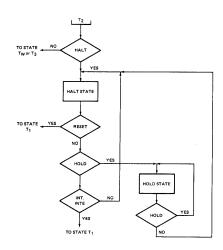

There are three exceptions to the defined duration of a state. They are the WAIT state; the hold (HLDA) state and the halt (HLTA) state, described later in this chapter. Because the WAIT, the HLDA, and the HLTA states depend upon external events, they are by their nature of indeterminate length. Even these exceptional states, however, must

Figure 2-11. HALT Timing

Figure 2-12. HALT Sequence Flow Chart.

While no one instruction cycle will consist of more then five machine cycles, the following ten different types of machine cycles may occur within an instruction cycle:

- (1) FETCH (M1)

- (2) MEMORY READ

- (3) MEMORY WRITE

- (4) STACK READ

- (5) STACK WRITE

- (6) INPUT

- (7) OUTPUT

- (8) INTERRUPT

- (9) HALT

- (10) HALT INTERRUPT

The machine cycles that actually do occur in a particular instruction cycle depend upon the kind of instruction, with the overriding stipulation that the first machine cycle in any instruction cycle is always a FETCH.

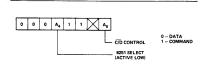

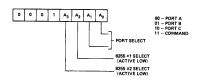

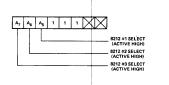

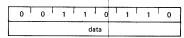

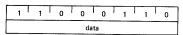

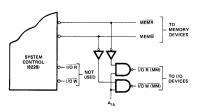

The processor identifies the machine cycle in progress by transmitting an eight-bit status word during the first state of every machine cycle. Updated status information is presented on the 8080's data lines (D<sub>0</sub>-D<sub>7</sub>), during the SYNC interval. This data should be saved in latches, and used to develop control signals for external circuitry. Table 2-1 shows how the positive-true status information is distributed on the processor's data bus.

Status signals are provided principally for the control of external circuitry. Simplicity of interface, rather than machine cycle identification, dictates the logical definition of individual status bits. You will therefore observe that certain processor machine cycles are uniquely identified by a single status bit, but that others are not. The M<sub>1</sub> status bit (D<sub>6</sub>), for example, unambiguously identifies a FETCH machine cycle. A STACK READ, on the other hand, is indicated by the coincidence of STACK and MEMR signals. Machine cycle identification data is also valuable in the test and de-bugging phases of system development. Table 2-1 lists the status bit outputs for each type of machine cycle.

### State Transition Sequence:

Every machine cycle within an instruction cycle consists of three to five active states (referred to as T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, T<sub>4</sub>, T<sub>5</sub> or T<sub>W</sub>). The actual number of states depends upon the instruction being executed, and on the particular machine cycle within the greater instruction cycle. The state transition diagram in Figure 2-4 shows how the 8080 proceeds from state to state in the course of a machine cycle. The diagram also shows how the READY, HOLD, and INTERRUPT lines are sampled during the machine cycle, and how the conditions on these lines may modify the

basic transition sequence. In the present discussion, we are concerned only with the basic sequence and with the READY function. The HOLD and INTERRUPT functions will be discussed later.

The 8080 CPU does not directly indicate its internal state by transmitting a "state control" output during each state; instead, the 8080 supplies direct control output (INTE, HLDA, DBIN,  $\overline{\text{WR}}$  and WAIT) for use by external circuitry.

Recall that the 8080 passes through at least three states in every machine cycle, with each state defined by successive low-to-high transitions of the  $\phi_1$  clock. Figure 2-5 shows the timing relationships in a typical FETCH machine cycle. Events that occur in each state are referenced to transitions of the  $\phi_1$  and  $\phi_2$  clock pulses.

The SYNC signal identifies the first state (T<sub>1</sub>) in every machine cycle. As shown in Figure 2-5, the SYNC signal is related to the leading edge of the  $\phi_2$  clock. There adelay (tpc) between the low-tp-high transition of  $\phi_2$  and the positive-going edge of the SYNC pulse. There also is a corresponding delay (also tpc) between the next  $\phi_2$  pulse and the falling edge of the SYNC signal. Status information is displayed on Dq-Dq during the same  $\phi_2$  to  $\phi_2$  interval. Switching of the status signals is likewise controlled by  $\phi_2$ .

The rising edge of  $\phi_2$  during T<sub>1</sub> also loads the processor's address lines (A<sub>0</sub>-A15). These lines become stable within a brief delay (t<sub>DA</sub>) of the  $\phi_2$  clocking pulse, and they remain stable until the first  $\phi_2$  pulse after state T<sub>3</sub>. This gives the processor ample turned from memory.

Once the processor has sent an address to memory, there is an opportunity for the memory to request a WAIT. This it does by pulling the processor's READY line low, prior to the "Ready set-up" interval  $\{t_{RS}\}$  which occurs during the  $\phi_2$  pulse within state  $T_2$  or  $T_W$ . As long as the READY line remains low, the processor will idle, giving the memory time to respond to the addressed data request. Refer to Figure 2-5.

The processor responds to a wait request by entering an alternative state (T<sub>W</sub>) at the end of T<sub>2</sub>, rather than proceeding directly to the T<sub>3</sub> state. Entry into the T<sub>W</sub> state is indicated by a WAIT signal from the processor, acknowledging the memory's request. A low-to-high transition on the WAIT line is triggered by the rising edge of the  $\phi_1$  clock and occurs within a brief delay (t<sub>D</sub>C) of the actual entry into the T<sub>W</sub> state.

A wait period may be of indefinite duration. The processor remains in the waiting condition until its READY line again goes high. A READY indication **must** precede the falling edge of the  $\phi_2$  clock by a specified interval (t<sub>RS</sub>), in order to guarantee an exit from the T<sub>W</sub> state. The cycle may then proceed, beginning with the rising edge of the next  $\phi_1$  clock. A WAIT interval will therefore consist of an integral number of T<sub>W</sub> states and will always be a multiple of the clock period.

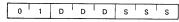

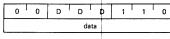

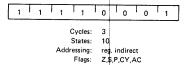

| MNEMONIC               | OP 0        | ODE      |                  |             | M1          | ii T                       |           |                     | M2                          |                |  |

|------------------------|-------------|----------|------------------|-------------|-------------|----------------------------|-----------|---------------------|-----------------------------|----------------|--|

|                        | D7 D6 D5 D4 | D3D2D1D0 | T1               | T2[2]       | Т3          | T4                         | Т5        | T1                  | T2[2]                       | Т3             |  |

| MOV r1, r2             | 0 1 D D     | DSSS     | PC OUT<br>STATUS | PC = PC +1  | INST→TMP/IR | (SSS)→TMP                  | (TMP)→DDD |                     |                             |                |  |

| MOV r, M               | 0 1 D D     | D 1 1 0  | 1                | 1           | 1 1         | X(3)                       |           | HL OUT<br>STATUS[6] | DATA                        | ►DDD           |  |

| MOV M, r               | 0 1 1 1     | 0 8 8 8  |                  |             |             | (SSS)→TMP                  |           | HL OUT<br>STATUS[7] | (TMP)                       | DATA BUS       |  |

| SPHL                   | 1111        | 1 0 0 1  |                  |             |             | (HL)                       | SP        |                     |                             |                |  |

| MVI r, data            | 0000        | D 1 1 0  |                  |             |             | ×                          |           | PC OUT<br>STATUS[6] | B2                          | <b>→</b> DDDD  |  |

| MVI M, data            | 0 0 1 1     | 0 1 1 0  |                  |             |             | ×                          |           | 1                   | B2-                         | ►TMP           |  |

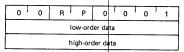

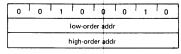

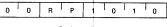

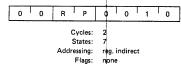

| LXI rp, date           | 0 0 R P     | 0 0 0 1  |                  |             |             | ×                          |           |                     | PC = PC + 1 B2              | ►r1            |  |

| LDA addr               | 0 0 1 1     | 1010     |                  |             |             | x                          |           |                     | PC = PC + 1 B2              | - Z            |  |

| STA addr               | 0 0 1 1     | 0 0 1 0  |                  |             |             | ×                          |           |                     | PC = PC + 1 B2              | ►Z             |  |

| LHLD addr              | 0 0 1 0     | 1010     |                  |             |             | ×                          |           |                     | PC = PC + 1 B2 -            | ►Z             |  |

| SHLD addr              | 0 0 1 0     | 0 0 1 0  |                  |             |             | ×                          |           | PC OUT<br>STATUS[6] |                             | ►Z             |  |

| LDAX rp[4]             | 0 0 R P     | 1010     |                  |             |             | ×                          |           | rp OUT<br>STATUSIG  | DATA-                       | -Α             |  |

| STAX rp <sup>[4]</sup> | 0 0 R P     | 0010     |                  |             |             | ×                          |           | rp OUT<br>STATUS[7] | (A) —                       | ► DATA BUS     |  |

| XCHG                   | 1110        | 1011     |                  |             |             | (HL)+-+(DE)                |           |                     |                             |                |  |

| ADD r                  | 1000        | 0 5 5 5  |                  |             |             | (SSS)→TMP<br>(A)→ACT       |           | (9)                 | (ACT)+(TMP)→A               |                |  |

| ADD M                  | 1000        | 0 1 1 0  |                  |             |             | (A)→ACT                    |           | HL OUT<br>STATUS[6] | DATA                        | →TMP           |  |

| ADI data               | 1,1 0 0     | 0 1 1 0  |                  |             |             | (A)→ACT                    |           | PC OUT<br>STATUSIO  | PC = PC + 1 B2 -            | ►TMP           |  |

| ADC r                  | 1000        | 1 5 5 5  |                  |             |             | (SSS)→TMP<br>(A)→ACT       |           | (9)                 | (ACT)+(TMP)+CY-A            |                |  |

| ADC M                  | 1000        | 1 1 1 0  |                  |             |             | (A)→ACT                    |           | HL OUT<br>STATUS[6] | DATA-                       | <b>→</b> TMP   |  |

| ACI data               | 1 1 0 0     | 1 1 1 0  |                  |             |             | (A)→ACT                    |           | PC OUT<br>STATUS[6  | PC = PC + 1 B2-             | ►TMP           |  |

| SUB r                  | 1001        | 0 8 8 8  |                  |             |             | (SSS)→TMP<br>(A)→ACT       |           | [9]                 | (ACT)-(TMP)→A               |                |  |

| SUB M                  | 1001        | 0 1 1 0  |                  |             |             | (A)→ACT                    |           | HL OUT<br>STATUS[6] | DATA-                       | → TMP          |  |

| SUI deta               | 1101        | 0 1 1 0  |                  |             |             | (A)→ACT                    |           | PC OUT<br>STATUSIG  | PC = PC + 1 B2-             | ►TMP           |  |

| SBB r                  | 1 0 0 1     | 1 5 5 5  |                  |             |             | (SSS)→TMP<br>(A)→ACT       |           | (9)                 | (ACT)-(TMP)-CY→A            |                |  |

| SBB M                  | 1001        | 1110     |                  |             |             | (A)→ACT                    |           | HL OUT<br>STATUS[6] | DATA-                       | <b>→</b> TMP   |  |

| \$BI deta              | 1 1 0 1     | 1 1 1 0  |                  |             |             | (A)→ACT                    |           | PC OUT<br>STATUS(6  | PC = PC + 1 B2-             | ► TMP          |  |

| INR r                  | 0 0 D D     | D 1 0 0  |                  |             |             | (DDD)→TMP<br>(TMP) + 1→ALU | ALU→DDD   |                     |                             |                |  |

| INR M                  | 0 0 1 1     | 0 1 0 0  |                  |             |             | ×                          |           | HL OUT<br>STATUS[6] | DATA<br>(TMP)+1             | ► TMP<br>► ALU |  |

| DCR r                  | 0 0 D D     | D 1 0 1  |                  |             |             | (DDD)→TMP<br>(TMP)+1→ALU   | ALU→DDD   |                     |                             |                |  |

| DCR M                  | 0 0 1 1     | 0 1 0 1  |                  |             |             | x                          | 5.4       | HL OUT<br>STATUS[6] | DATA<br>(TMP)-1             | ► TMP<br>► ALU |  |

| INX rp                 | 0 0 R P     | 0 0 1 1  |                  |             |             | (RP) + 1                   | RP        |                     |                             |                |  |

| DCX rp                 | OORP        | 1011     |                  |             |             | (RP) - 1                   | RP        |                     |                             |                |  |

| DAD rp(8)              | 0 0 R P     | 1001     |                  |             |             | x                          |           | (ri)→ACT            | (L)→TMP,<br>(ACT)+(TMP)→ALU | ALU→L, CY      |  |

| DAA                    | 0 0 1 0     | 0 1 1 1  |                  |             |             | DAA-A, FLAGS[10]           |           |                     |                             |                |  |

| ANA r                  | 1010        | 0 8 8 8  |                  |             |             | (SSS)→TMP<br>(A)→ACT       |           | [9]                 | (ACT)+(TMP)-+A              |                |  |

| ANA M                  | 1010        | 0110     | PC OUT<br>STATUS | PC = PC + 1 | INST→TMP/IR | (A)-+ACT                   | 16.14     | HL OUT<br>STATUS    | DATA-                       | <b>→</b> TMP   |  |

Figure 2-6. Input Instruction Cycle

Figure 2-7. Output Instruction Cycle

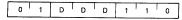

| MNEMONIC                    | OP 0        | ODE      |                  |             | M1                 | [1]                           |                 |                  |            | M2           |               |              |

|-----------------------------|-------------|----------|------------------|-------------|--------------------|-------------------------------|-----------------|------------------|------------|--------------|---------------|--------------|

|                             | D7 D6 D5 D4 | D3D2D1D0 | Τ1               | T2[2]       | Т3                 | T4                            | T5              | T1               | П          | T2[2]        |               | Т3           |

| ANI data                    | 1 1 1 0     | 0 1 1 0  | PC OUT<br>STATUS | PC = PC + 1 | INST-TMP/IR        | (A)-ACT                       |                 | PC OUT<br>STATUS | 61         | PC = PC + 1  | 82            | _TMP         |

| XRA r                       | 1010        | 1 S S S  |                  | 1           | 1                  | (A)→ACT<br>(SSS)→TMP          |                 | (9)              | П          | (ACT)+(TPM)- | +A            |              |

| XRA M                       | 1010        | 1 1 1 0  |                  |             |                    | (A)→ACT                       |                 | HL OUT           | 6)         |              | DATA-         | <b>→</b> TMP |

| XRI deta                    | 1 1 1 0     | 1 1 1 0  |                  |             |                    | (A)→ACT                       |                 | PC OUT<br>STATUS | <b>6</b> 1 | PC = PC + 1  | B2 —          | ► TMP        |

| ORAr                        | 1011        | 0 8 8 8  |                  |             |                    | (A)→ACT<br>(SSS)→TMP          |                 | [9]              | П          | (ACT)+(TMP)- | +A            |              |

| M ARO                       | 1 0 1 1     | 0 1 1 0  |                  |             |                    | (A)→ACT                       |                 | HL OUT<br>STATUS | ВІ         |              | DATA -        | ►TMP         |

| ORI deta                    | 1111        | 0110     |                  |             |                    | (A)→ACT                       |                 | PC OUT           | <b>B</b> 1 | PC = PC + 1  | 82            | ► TMP        |

| CMP r                       | 1011        | 1 8 8 8  |                  |             |                    | (A)→ACT<br>(SSSI→TMP          |                 | (9)              |            | (ACT)-(TMP), | FLAGS         | 1            |

| CMP M                       | 1011        | 1 1 1 0  |                  |             |                    | (A)→ACT                       |                 | HL OUT<br>STATUS |            |              | DATA -        | ►TMP         |

| CPI data                    | 1111        | 1 1 1 0  |                  |             |                    | (A)→ACT                       |                 | PC OUT<br>STATUS | В          | PC - PC + 1  | B2 -          | <b>→</b> TMP |

| RLĊ                         | 0000        | 0 1 1 1  |                  |             |                    | (A)→ALU<br>ROTATE             |                 | (9)              | Ш          | ALU→A, CY    |               |              |

| RRC                         | 0000        | 1111     |                  |             |                    | (A)→ALU<br>ROTATE             |                 | (9)              | Ц          | ALU→A, CY    |               |              |

| RAL                         | 0001        | 0 1 1 1  |                  |             |                    | (A), CY→ALU<br>ROTATE         |                 | (9)              |            | ALU→A, CY    |               |              |

| RAR                         | 0 0 0 1     | 1 1 1 1  |                  |             |                    | (A), CY→ALU<br>ROTATE         |                 | (9)              | Ш          | ALU-A, CY    | and the later |              |

| CMA                         | 0010        | 1 1 1 1  |                  |             |                    | (Ā)→A                         |                 |                  |            |              |               |              |

| СМС                         | 0 0 1 1     | 1 1 1 1  |                  |             |                    | CY→CY                         |                 |                  |            |              |               |              |

| STC                         | 0 0 1 1     | 0 1 1 1  |                  |             |                    | 1→CY                          |                 |                  |            |              |               |              |

| JMP addr                    | 1 1 0 0     | 0011     |                  |             |                    | ×                             |                 | PC OUT<br>STATUS | -          | PC = PC + 1  | 82-           | <b>-</b> Z   |

| J cond addr [17]            | 1100        | C 0 1 0  |                  |             |                    | JUDGE COND                    | ITION           | PC OUT<br>STATUS | 6)         | PC = PC + 1  | B2 -          | <b>→</b> Z   |

| CALL addr                   | 1 1 0 0     | 1 1 0 1  |                  |             |                    | SP = SP -                     |                 | PC OUT<br>STATUS | 6)         | PC - PC + 1  | B2 -          | ►Z           |

| C cond addr <sup>[17]</sup> | 1100        | C 1 0 0  |                  |             |                    | JUDGE COND<br>IF TRUE, SP = 1 | ITION<br>SP - 1 | PC OUT<br>STATUS |            | PC = PC + 1  | B2-           | ►Z           |

| RET                         | 1 1 0 0     | 1 0 0 1  |                  |             | ,                  | ×                             | 2.1             | SP OUT<br>STATUS | 15)        | SP = SP + 1  | DATA-         | ►Z           |

| R cond addr[17]             | 1100        | C 0 0 0  |                  |             | INST-TMP/IR        | JUDGE COND                    |                 | SP OUT<br>STATUS | 15]        | SP = SP + 1  | DATA-         | ►Z           |

| RST n                       | 1 1 N N     | N 1 1 1  |                  |             | ¢→W<br>INST→TMP/IR | SP = SP -                     |                 | SP OUT<br>STATUS | 16)        | SP = SP - 1  | (PCH) -       | DATA BUS     |

| PCHL                        | 1 1 1 0     | 1001     |                  |             | INST→TMP/IR        | (HL)                          | PC              |                  |            |              |               |              |

| PUSH rp                     | 1 1 R P     | 0101     |                  |             |                    | SP = SP -                     |                 | SP OUT<br>STATUS | 16]        | SP = SP - 1  | (rh)-         | DATA BUS     |

| PUSH PSW                    | 1111        | 0 1 0 1  |                  |             |                    | SP = SP -                     | 1               | SP OUT<br>STATUS | 16)        | SP = SP - 1  | (A)-          | ►DATA BUS    |

| POP rp                      | 1 1 R P     | 0 0 0 1  |                  |             |                    | ×                             |                 | SP OUT<br>STATUS |            | SP = SP + 1  | DATA-         | <b>⇒</b> r1  |

| POP PSW                     | 1111        | 0001     |                  |             |                    | ×                             |                 | SP OUT<br>STATUS | 15}        | SP = SP + 1  | DATA-         | FLAGS        |

| XTHL                        | 1110        | 0 0 1 1  |                  |             |                    | ×                             |                 | SP OUT<br>STATUS | 15)        | SP = SP + 1  | DATA -        | -z           |

| IN port                     | 1 1 0 1     | 1011     |                  |             |                    | ×                             |                 | PC OUT<br>STATUS | (6)        | PC = PC + 1  | B2-           | ►Z, W        |

| OUT port                    | 1101        | 0011     | $\Box$           |             |                    | ×                             |                 | PC OUT<br>STATUS | (6)        | PC = PC + 1  | B2 -          | →Z, W        |

| EI                          | 1111        | 1011     | <u> </u>         |             |                    | SET INTE F/F                  |                 |                  |            |              |               |              |

| DI                          | 1111        | 0011     |                  |             |                    | RESET INTE F/F                |                 |                  |            |              | (20)          |              |

| HLT                         | 0111        | 0 1 1 0  |                  |             |                    | ×                             |                 | PC OUT<br>STATUS |            | HALT MODE    | الما          |              |

| NOP                         | 0000        | 0000     | PC OUT<br>STATUS | PC = PC + 1 | INST-+TMP/IR       | ×                             |                 |                  |            |              |               |              |

### INTERRUPT SEQUENCES

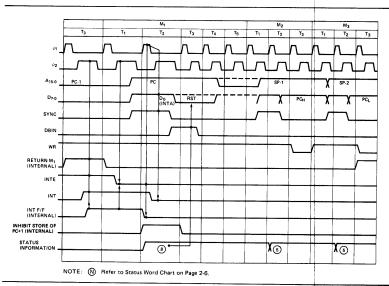

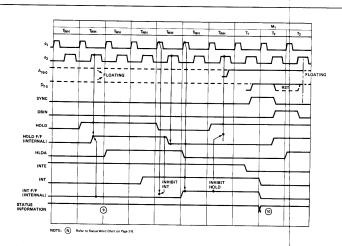

The 8080 has the built-in capacity to handle external interrupt requests. A peripheral device can initiate an interrupt simply by driving the processor's interrupt (INT) line high.

The interrupt (INT) input is asynchronous, and a request may therefore originate at any time during any instruction cycle. Internal logic re-clocks the external request, so that a proper correspondence with the driving clock is established. As Figure 2-8 shows, an interrupt request (INT) arriving during the time that the interrupt enable line (INTE) is high, acts in coincidence with the  $\phi_2$  clock to set the internal interrupt latch. This event takes place during the last state of the instruction cycle in which the request occurs, thus ensuring that any instruction in progress is completed before the interrupt can be processed.

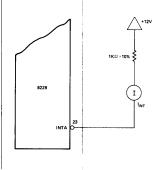

The INTERRUPT machine cycle which follows the arrival of an enabled interrupt request resembles an ordinary FETCH machine cycle in most respects. The M<sub>1</sub> status bit is transmitted as usual during the SYNC interval. It is accompanied, however, by an INTA status bit (D<sub>0</sub>) which acknowledges the external request. The contents of the program counter are latched onto the CPU's address lines during T<sub>1</sub>, but the counter itself is not incremented during the INTERRUPT machine cycle, as it otherwise would be.

In this way, the pre-interrupt status of the program counter is preserved, so that data in the counter may be restored by the interrupted program after the interrupt request has been processed.

The interrupt cycle is otherwise indistinguishable from an ordinary FETCH machine cycle. The processor itself takes no further special action. It is the responsibility of the peripheral logic to see that an eight-bit interrupt instruction is "jammed" onto the processor's data bus during state T3. In a typical system, this means that the data-in bus from memory must be temporarily disconnected from the processor's main data bus, so that the interrupting device can command the main bus without interference.

The 8080's instruction set provides a special one-byte call which facilitates the processing of interrupts (the ordinary program Call takes three bytes). This is the RESTART instruction (RST). A variable three-bit field embedded in the eight-bit field of the RST enables the interrupting device to direct a Call to one of eight fixed memory locations. The decimal addresses of these dedicated locations are: 0, 8, 16, 24, 32, 40, 48, and 56. Any of these addresses may be used to store the first instruction(s) of a routine designed to service the requirements of an interrupting device. Since the (RST) is a call, completion of the instruction also stores the old program counter contents on the STACK.

Figure 2-8. Interrupt Timing

#### MOTES

- 1. The first memory cycle (M1) is always an instruction fetch; the first (or only) byte, containing the op code, is fetched during this cycle.

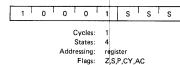

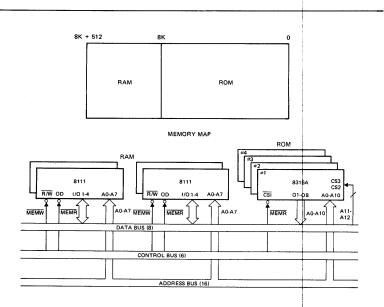

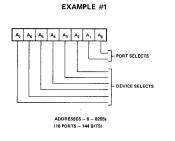

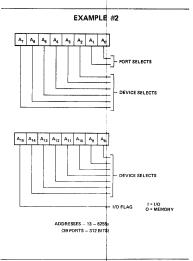

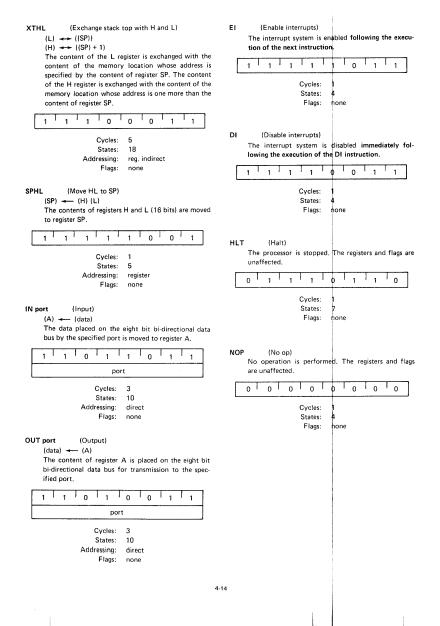

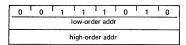

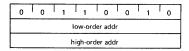

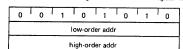

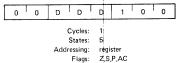

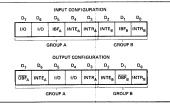

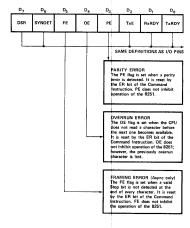

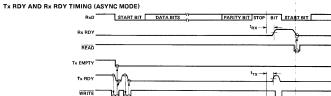

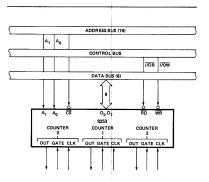

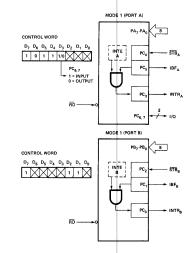

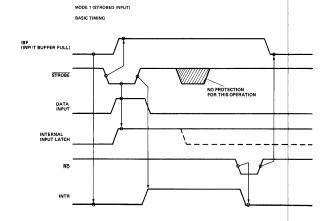

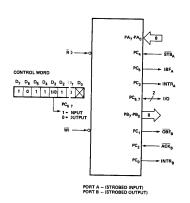

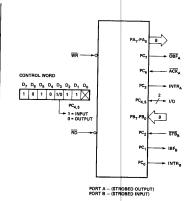

- 2. If the READY input from memory is not high during T2 of each memory cycle, the processor will enter a wait state (TW) until READY is sampled as high.