# EGEG RETICON

EG&G RETICON • 345 POTRERO AVENUE • SUNNYVALE, CALIFORNIA 94086 • TEL. (408) 738-4266

OPERATION AND MAINTENANCE

MANUAL

MC520/RS520

CAMERA/CONTROLLER SYSTEM

|  | 1 |

|--|---|

|  |   |

|  |   |

#### SAFETY CONSIDERATIONS

#### CAUTION

#### **BEFORE SWITCHING ON THIS INSTRUMENT:**

- 1. MAKE SURE THE INSTRUMENT IS SET TO THE VOLTAGE OF THE POWER SOURCE

- 2. ENSURE THAT ALL DEVICES CONNECTED TO THIS INSTRUMENT ARE CONNECTED TO THE PROTECTIVE (EARTH) GROUND.

- 3. THE PROTECTIVE EARTH TERMINALS OF THE INSTRUMENT MUST BE CONNECTED TO THE PROTECTIVE CONDUCTOR OF THE (MAINS) POWER CORD. THE MAINS PLUG SHALL ONLY BE INSERTED IN A SOCKET OUTLET PROVIDED WITH A PROTECTIVE EARTH CONTACT. THE PROTECTIVE ACTION MUST NOT BE NEGATED BY THE USE OF AN EXTENSION CORD (POWER CABLE) WITHOUT A PROTECTIVE CONDUCTOR (GROUNDING).

- 4. MAKE SURE THAT ONLY FUSES WITH THE REQUIRED RATED CURRENT AND OF THE SPECIFIED TYPE (NORMAL BLOW, TIME DELAY, ETC.) ARE USED FOR REPLACEMENT. THE USE OF REPAIRED FUSES AND THE SHORT-CIRCUITING OF FUSE HOLDER MUST BE AVOIDED.

### WARNING

THE SERVICE INFORMATION FOUND IN THIS MANUAL IS OFTEN USED WITH POWER SUPPLIED AND PROTECTIVE COVERS REMOVED FROM THE INSTRUMENT. ENERGY AVAILABLE AT MANY POINTS MAY, IF CONTACTED, RESULT IN PERSONAL INJURY.

|   | ı |

|---|---|

|   | • |

|   |   |

|   | 1 |

|   | ı |

|   | - |

|   |   |

|   | 1 |

|   |   |

|   |   |

|   | ı |

|   | ı |

|   | • |

|   |   |

|   | 1 |

|   | 1 |

|   |   |

|   | 1 |

|   | ı |

|   |   |

|   |   |

|   |   |

|   | 1 |

|   |   |

|   | • |

|   | ı |

|   | ı |

|   |   |

|   | 1 |

|   | ı |

|   | • |

|   |   |

| • |   |

|   |   |

|   |   |

|   | 1 |

|   | ı |

|   | • |

|   | _ |

|   | 1 |

|   |   |

|   |   |

|   | 1 |

|   |   |

|   | • |

|   | _ |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   | - |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   | - |

|   | , |

|   |   |

|   | I |

|   |   |

|   |   |

#### WARRANTY

Reticon warrants that the camera described herein will be free from defects in material and workmanship under normal use and service for a period of one year from date of shipment. The liability of Reticon under this warranty is limited solely to replacing or repairing or issuing credit (at the discretion of Reticon) for such parts that become defective during the warranty period. In order to permit Reticon to properly administer this warranty, Buyer shall: (1) Notify Reticon promptly in writing of any claims; (2) Provide Reticon with an opportunity to inspect and test the camera claimed to be defective. Such inspection may be on customer's premises or Reticon may request return of the camera at the customer's expense. Such expenses will subsequently be reimbursed to customer if the camera is found to be defective. Adjustment is contingent upon Reticon's examination of the product, disclosing that apparent defects have not been caused by misuse, abuse, improper installation or application, repair, alteration, accident or negligence in use, storage, transportation or handling. In no event shall Reticon be liable to Buyer for loss of profits, loss of use, or damages of any kind based upon a claim for breach of warranty.

THIS WARRANTY IS EXPRESSED IN LIEU OF ALL OTHER WARRANTIES EXPRESSED OR IMPLIED, INCLUDING THE IMPLIED WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE, AND OF ALL OTHER OBLIGATIONS OR LIABILITIES ON RETICON'S PART, AND IT NEITHER ASSUMES NOR AUTHORIZES ANY OTHER PERSON TO ASSUME FOR RETICON ANY OTHER LIABILITIES IN CONNECTION WITH THE SALE OF THE SAID CAMERA.

Copyright RETICON Corporation 1976. Contents may not be reproduced in whole or in part without the written consent of RETICON Corporation. RETICON reserves the right to make engineering refinements that may not be reflected in this manual.

Information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by RETICON Corporation for its use; nor for any infrigement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RETICON Corporation.

# TABLE OF CONTENTS

| SECTION |              |                                | PAG         |

|---------|--------------|--------------------------------|-------------|

| I       | SYSTEM STAR  | TUP                            |             |

|         | 1.1          | UNPACKING                      | 1-1         |

|         | 1.2          | POWERING UP                    |             |

|         | 1.3          | SYSTEM CHECKOUT                |             |

| II      | INTRODUCTION | ON                             |             |

|         | 2.1          | MC520/RS520 SYSTEM             | 2-1         |

|         | 2.2          | MC520 CAMERA - GENERAL         |             |

|         | 2.2.1        | MC520 Mechanical Configuration |             |

|         | 2.2.2        | MC520 Electronic Configuration |             |

|         | 2.3          | RS520 CONTROLLER - GENERAL     |             |

|         | 2.3.1        | RS520 Mechanical Configuration |             |

|         | 2.3.2        | RS520 Electronic Configuration |             |

| III     | MC520 CAME   | CRA SPECIFICATIONS             |             |

|         | _            |                                |             |

|         | 3.1          | MECHANICAL                     |             |

|         | 3.2          | OPTICAL                        |             |

|         | 3.3          | ELECTRICAL                     |             |

|         | 3.3.1        | BNC Connectors                 |             |

|         | 3.3.1.1      | Video                          |             |

|         | 3.3.1.2      | Frame Sync                     |             |

|         | 3.3.1.3      | Line Sync                      |             |

|         | 3.3.2        | Bendix Connector, J4           |             |

|         | 3.3.2.1      | Analog Signals                 |             |

|         | 3.3.2.1.1    | Video (+) and (-) Outputs      |             |

|         | 3.3.2.2      | Digital Signals                |             |

|         | 3.3.2.2.1    | MCLK (+) and (-) Inputs        |             |

|         | 3.3.2.2.2    | M1C (+) and (-) Inputs         |             |

|         | 3.3.2.2.3    | CCLK (+) and (-) Outputs       |             |

|         | 3.3.2.2.4    | EOF (+) and (-) Outputs        |             |

|         | 3.3.2.3      | Power                          | 3-4         |

|         | 3.3.2.3.1    | +5 Volts and Digital Ground    | 3-4         |

|         | 3.3.2.3.2    | +15 Volts                      |             |

|         | 3.3.2.3.3    | -15 Volts and Analog Ground    | <b>3-</b> 5 |

|         | 3.4          | ENVIRONMENTAL                  |             |

|         | 3.4.1        | Temperature                    | 3-5         |

|         | 3.4.2        | Humidity                       | 3-5         |

|         | 3.5          | ADJUSTMENTS                    | 3-5         |

|         | 3.5.1        | Internal                       |             |

|         |              |                                |             |

| SECTION |            |                                                | PAGE       |

|---------|------------|------------------------------------------------|------------|

| IV      | RS520 CONT | ROLLER SPECIFICATIONS                          |            |

|         | 4.1        | MECHANICAL                                     | 4-1        |

|         | 4.2        | ELECTRICAL                                     | 4-1        |

|         | 4.2.1      | BNC Connectors                                 |            |

|         | 4.2.1.1    | Z Output                                       |            |

|         | 4.2.1.2    | Y Output                                       |            |

|         | 4.2.1.3    | X Output                                       |            |

|         | 4.2.1.4    | 75Ω Output                                     | 4-2 *      |

|         | 4.2.1.5    | Threshold                                      | 4-3        |

|         | 4.2.1.6    | Sync                                           | 4-3        |

|         | 4.2.2      | Bendix Connectors                              | 4-3        |

|         | 4.2.2.1    | Data A Connector                               | 4-3        |

|         | 4.2.2.1.1  | Digital Ground                                 |            |

|         | 4.2.2.1.2  | ECLK (+) and (-) Inputs                        | 4-4        |

|         | 4.2.2.1.3  | Data (+) and (-) Outputs                       |            |

|         | 4.2.2.1.4  | Light Level (+) and (-) Outputs                |            |

|         | 4.2.2.1.5  | GCLK (+) and (-) Outputs                       |            |

|         | 4.2.2.1.6  | FEN (+) and (-) Outputs                        |            |

|         | 4.2.2.1.7  | ESTART (+) and (-) Inputs                      |            |

|         | 4.2.2.2    | Data B Connector                               |            |

|         | 4.2.2.2.1  | LEN (+) and (-) Outputs                        |            |

|         | 4.2.2.2.2  | Analog and Signal Ground                       |            |

|         | 4.2.2.2.3  | 50 (+) and (-) Video Output                    |            |

|         | 4.2.2.2.4  | Digital Ground                                 |            |

|         | 4.2.2.2.5  | RE-REF (+) and (-) Output                      |            |

|         | 4.2.2.2.6  | HCLK (+) and (-) Output                        |            |

|         | 4.2.2.2.7  | $M\emptyset \bullet EOF (+)$ and $(-)$ Outputs |            |

|         | 4.2.2.3    |                                                | 4-8        |

|         | 4.2.2.3.1  | Video (+) and Video (-) Inputs                 |            |

|         | 4.2.2.3.2  |                                                | 4-9        |

|         | 4.2.2.3.3  |                                                | 4-9        |

|         | 4.2.2.3.4  | CCLK (+) and (-) Input                         |            |

|         | 4.2.2.3.5  | EOF (+) and (-) Input                          |            |

|         | 4.2.2.3.6  | +5 Volts and Digital Ground                    |            |

|         | 4.2.2.3.7  | +15 Volts                                      |            |

|         | 4.2.2.3.8  | -15 Volts and Analog Ground                    |            |

|         | 4.3        | ENVIRONMENTAL                                  |            |

|         | 4.3.1      | Temperature                                    |            |

|         | 4.3.2      | Humidity                                       |            |

|         | 4.4        | ADJUSTMENTS                                    |            |

|         | 4.5        | P/C BOARDS                                     | 4-11       |

| V       |            | ION OF OPTICAL, ILLUMINATION, AND              |            |

|         | MOUNTING I | REQUIREMENTS                                   |            |

|         | 5.1        | OPTICAL RELATIONSHIPS                          | 5-1<br>5-1 |

|         | ~ 1 1      | Field of Migra (F)                             |            |

| SECTION |             |                                                    | PAG  |

|---------|-------------|----------------------------------------------------|------|

|         | 5.1.3       | Static Resolution (RS)                             | 5-1  |

|         | 5.1.4       | Dynamic Resolution (RD)                            |      |

|         | 5.1.5       | Working Distance (D)                               |      |

|         | 5.1.6       | - , ,                                              |      |

|         | 5.1.7       | Depth of Field                                     |      |

|         |             | Optical Determination Example                      |      |

|         | 5.2         | ILLUMINATION REQUIREMENTS                          |      |

|         | 5.2.1       | Array Sensitivity Characteristics                  |      |

|         | 5.2.2       | Array Blooming Characteristics                     |      |

|         | 5.2.3       | Camera Mounting                                    | 5-5  |

| VI      | INSTALLATIO | N AND ADJUSTMENT                                   |      |

|         | 6.1         | GENERAL                                            | 6-1  |

|         | 6.2         | MC520 CAMERA ELECTRONIC ADJUSTMENT                 |      |

|         | 6.2.1       | Initial Coarse Adjustment                          |      |

|         | 6.2.2       | Final Adjustment                                   |      |

|         | 6.2.2.1     | MY and Gain Balance Adjustment                     |      |

|         | 6.2.2.2     | LR/LT Adjustment                                   | -    |

|         | 6.2.2.3     | VQ Adjustment                                      |      |

|         | 6.2.2.4     | Gain Adjustment                                    |      |

|         | 6.2.2.5     | V <sub>BUF</sub> Adjustment                        |      |

|         | 6.2.2.6     |                                                    |      |

|         | 6.2.2.7     | $V_{\mathrm{BB}}$ Adjustment                       |      |

|         | 6.2.2.8     | V <sub>IRIS</sub> Balance                          |      |

|         | 6.2.2.9     | Cleaning Array Window                              |      |

|         | 6.3         | RS520 CONTROLLER ELECTRONIC ADJUSTMENT .           |      |

|         | 6.3.1       | Power Supply Adjustment                            |      |

|         | 6.3.2       | Controller Clock and Start Mode Selection          |      |

|         | 6.3.2.1     | GCLK Mode Selection                                |      |

|         | 6.3.2.2     | Master Slaving Multiple Cameras                    |      |

|         | 6.3.3       | Retrace Count Selection                            |      |

|         | 6.3.4       | Clock Frequency and Pulse Width Adjustment.        |      |

|         |             |                                                    | 0-7  |

|         | 6.3.5       | Analog Line Receiver Common Mode and               | 6.0  |

|         |             | Gain Adjustment                                    |      |

|         | 6.3.5.1     | Gain Adjustment                                    |      |

|         | 6.3.5.2     | Common Mode Balance (Factory Adjustment) .         | 6-9  |

|         | 6.3.6       | Odd and Even Sample Pulse Width Adjustment         | 6-1  |

|         | 6.3.7       | Sample-and-Hold Gain and Offset Balance Adjustment | 6-10 |

|         | 6.3.8       | Dark Level and Blanking Level/Balance              |      |

|         | 0.0.0       | Adjustment                                         | 6-1  |

|         | 6.3.9       | Transmit Gain and Balance Adjustment               | 6-13 |

|         | 6.3.10      | Data and Light Level Threshold Adjustment          |      |

|         | 6.3.11      | X and Y Sweep Amplitude Adjustment                 | 6-12 |

|         | 0.3.11      | A and I bweep Amplitude Adjustment                 | 0-12 |

| SECTION |             |                                          | PAGE |

|---------|-------------|------------------------------------------|------|

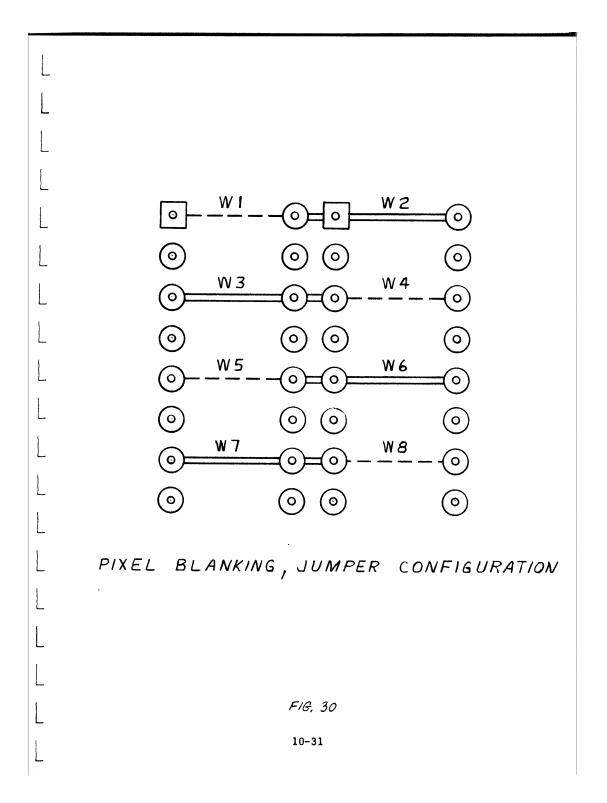

|         | 6.3.12      | Pixel Blanking Jumper Option             | 6-13 |

|         | 6.3.13      | Signal Selection Jumper Options          |      |

|         | 6.3.14      | Pixel Counter Jumper Options             |      |

|         | 6.3.15      | Light Level Jumper Options               |      |

|         | 6.4         | USER I/O CABLE PREPARATION               |      |

|         | 6.4.1       | D.C. Restoration of Video Output Signals |      |

|         | 6.5         | OPTICAL ADJUSTMENT                       |      |

|         | 6.5.1       | Exposure Adjustment                      |      |

|         | 6.5.1.1     | Line Scan Time                           |      |

|         | 6.5.1.2     | Lens F-Stop Adjustment                   |      |

|         | 6.5.1.3     | Light Level Adjustments                  |      |

|         | 6.5.2       | Video Dark and Blank Level Adjustment    |      |

|         | 6.5.3       | Object Centering                         |      |

|         | 6.5.4       | Focus Adjustment                         |      |

|         | 6.5.5       | Threshold Adjustment                     |      |

|         | 6.5.6       | Magnification Adjustment                 |      |

| VII     | PRINCIPLES  | OF OPERATION MC520 CAMERA                |      |

|         | 7.1         | INTRODUCTION                             | 7-1  |

|         | 7.2         | RA-100 x 100 ARRAY                       | 7-1  |

|         | 7.3         | ARRAY BOARD-A1                           |      |

|         | 7.4         | CONTROL BOARD-A2                         | 7-4  |

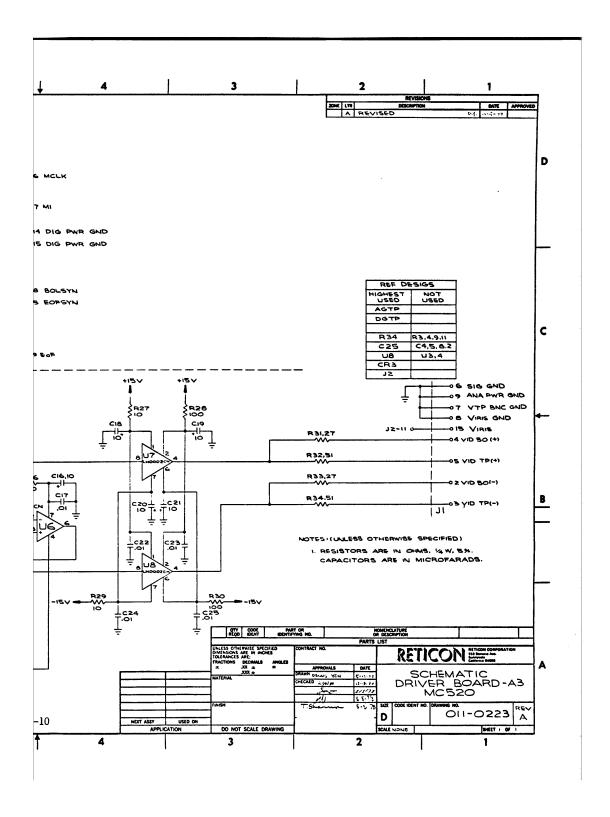

|         | 7.5         | DRIVER BOARD-A3                          | 7-5  |

| VIII    | PRINCIPLES  | OF OPERATION RS520 CONTROLLER            |      |

|         | 8.1         | INTRODUCTION                             | 8-1  |

|         | 8.2         | MC520 CAMERA                             | 8-1  |

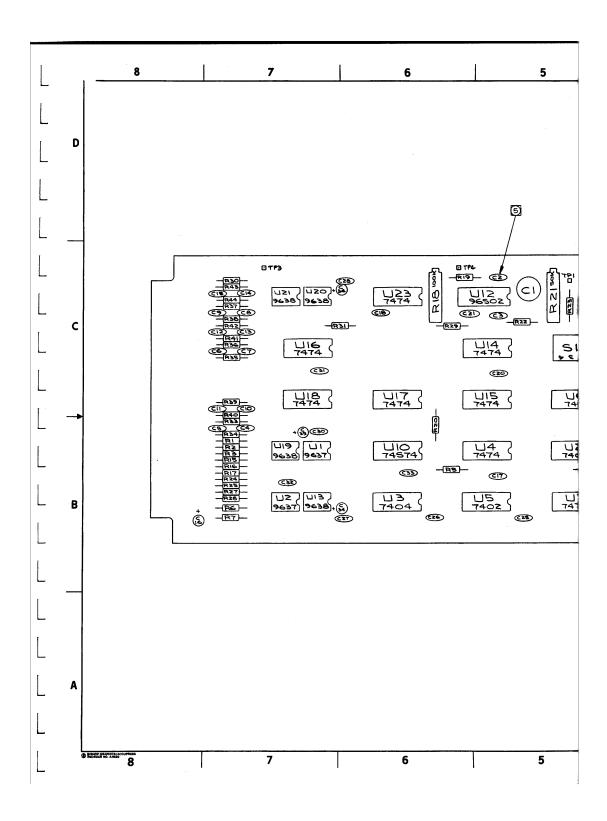

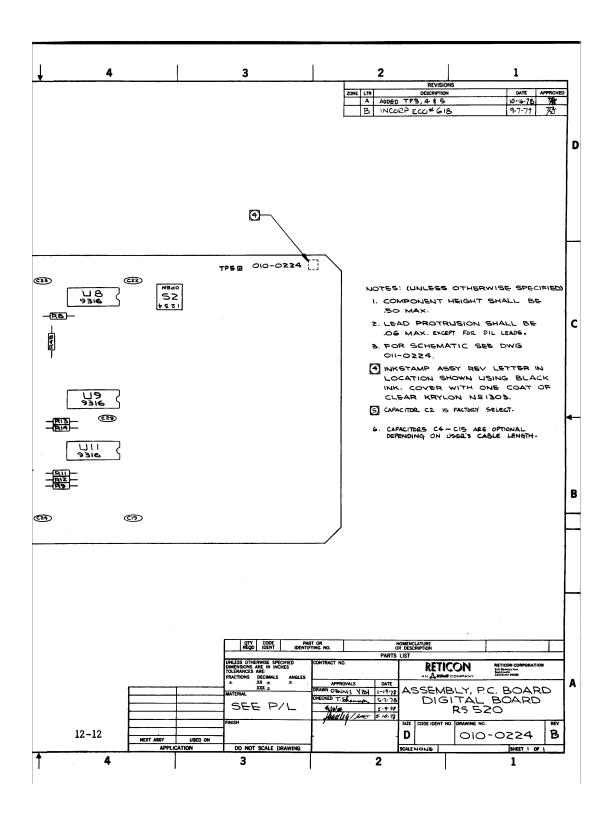

|         | 8 <b>.3</b> | DIGITAL BOARD-A4                         | 8-1  |

|         | 8.3.1       | "M" Register                             | 8-1  |

|         | 8.3.2       | Start Logic                              | 8-2  |

|         | 8.3.3       | Retrace Counter                          | 8-3  |

|         | 8.3.4       | Pixel Counter                            | 8-4  |

|         | 8.3.5       | Master Clock Generator                   | 8-4  |

|         | 8.3.6       | Camera Clock Duplicator                  | 8-4  |

|         | 8.3.7       | Logic Deskew Register                    | 8-5  |

|         | 8.3.8       | Cable Deskew Register                    | 8-5  |

|         | 8.3.9       | Enable and Re-Reference Registers        | 8-6  |

|         | 8.3.10      | GCLK and HCLK Generators                 | 8-7  |

|         | 8.4         | ANALOG BOARD-A6                          | 8-8  |

|         | 8.4.1       | Video Line Receiver                      | 8-8  |

|         | 8.4.2       | Sample-and-Hold                          |      |

|         | 8.4.3       | Blanking Switch                          | 8-11 |

|         | 8.4.4       | Line Drivers and Threshold Detectors     | 8-13 |

| L |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

|---|---------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|   | SECTION |                                                             |                                                                                                                                                                                                                                                                      | PAGE                                                        |

|   |         | 8.4.4.1<br>8.4.4.2<br>8.4.5                                 | Line Drivers                                                                                                                                                                                                                                                         | 8-13<br>8-14<br>8-15                                        |

|   | IX      | FAILURE DIAG                                                | NOSTIC PROCEDURES                                                                                                                                                                                                                                                    |                                                             |

|   |         | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9 | INTRODUCTION  TEST INSTRUMENTS  EXTERNAL CONNECTIONS  RS520 POWER SUPPLY  RS520 MASTER CLOCK GENERATOR  RS520 "M" REGISTER  RS520 LOGIC DESKEW REGISTER  RS520 CABLE DESKEW REGISTER  RS520 ENABLE AND RE-REFERENCE REGISTERS.  RS520 GCLK, HCLK, AND MØ • EOF LOGIC | 9-1<br>9-1<br>9-1<br>9-2<br>9-3<br>9-4<br>9-4<br>9-5<br>9-5 |

|   |         | 9.11<br>9.12<br>9.13<br>9.14                                | RS520 ANALOG LINE RECEIVER                                                                                                                                                                                                                                           | 9-7<br>9-8<br>9-8<br>9-9                                    |

|   |         | 9.15<br>9.16<br>9.17<br>9.18                                | RS520 X AND Y SWEEP                                                                                                                                                                                                                                                  | 9-10<br>9-10<br>9-11<br>9-12                                |

| L |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

|   |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

| L |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

| L |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

|   |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

|   |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

| L |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

|   |         |                                                             |                                                                                                                                                                                                                                                                      |                                                             |

| L |         |                                                             | v                                                                                                                                                                                                                                                                    |                                                             |

# SECTION X

# LIST OF ILLUSTRATIONS

| Figure No. | <u>Description</u>                                                | PAGE  |

|------------|-------------------------------------------------------------------|-------|

| 1          | Picture of MC520 Camera                                           | 10-2  |

| 2          | See Drawing 005-0081                                              | 10-3  |

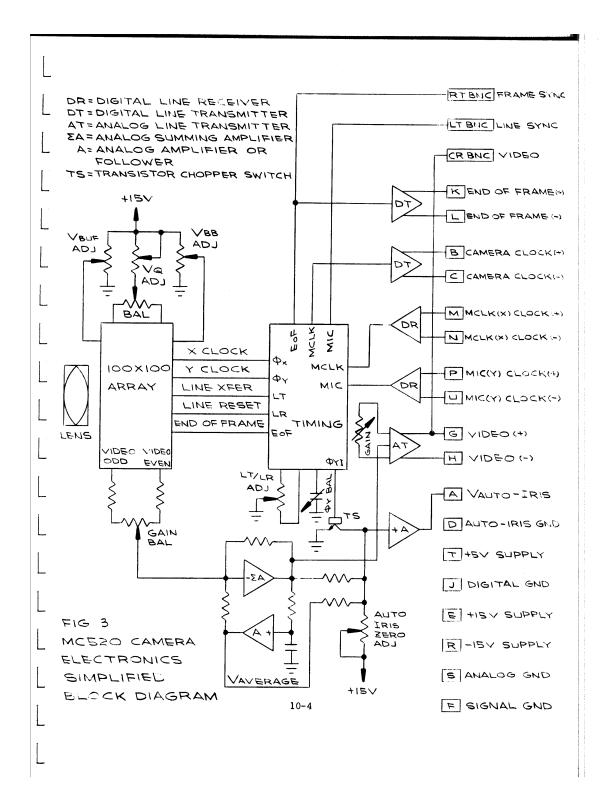

| 3          | MC520 Camera Electronics, Simplified Block Diagram · · ·          |       |

| 4          | Picture of RS520 Controller · · · · · · · · · · · · · · · · · · · |       |

| 5          | See Drawing 005-0082 · · · · · · · · · · · · · · · · · · ·        | 10-6  |

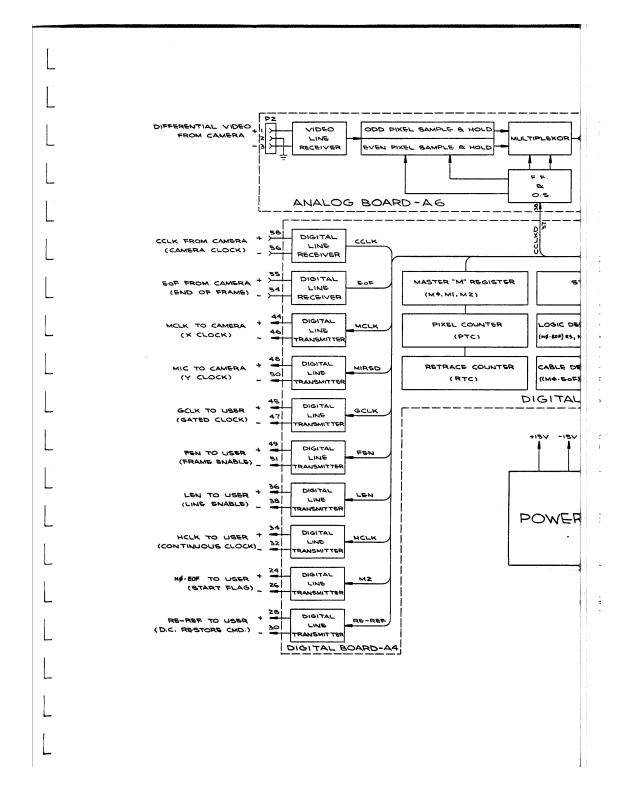

| 6          | RS520 Matrix Camera Controller Electronics,                       |       |

|            | Simplified Block Diagram                                          | 10-7  |

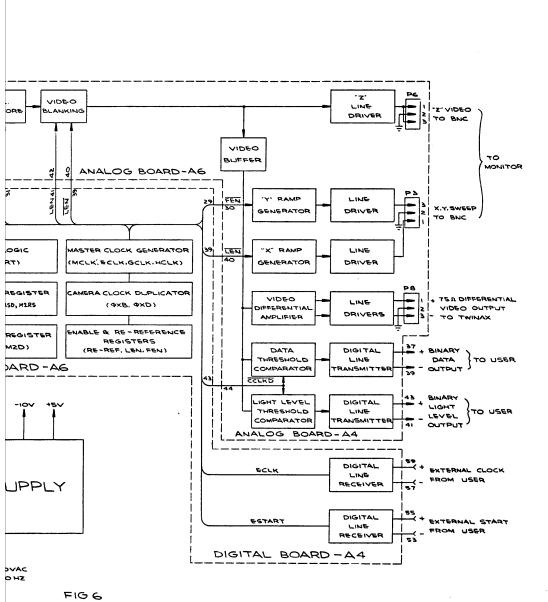

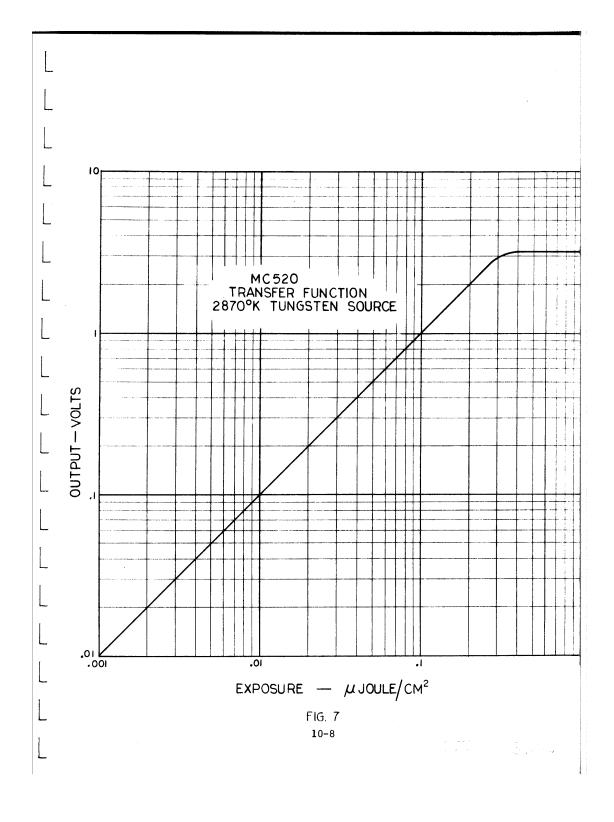

| 7          | MC520 Transfer Function                                           | 10-8  |

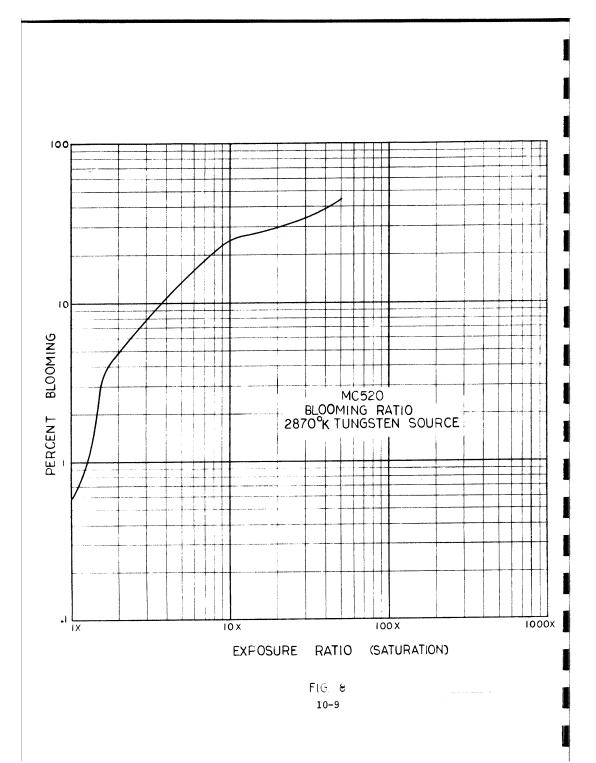

| 8          | MC520 Blooming Ratio                                              | 10-9  |

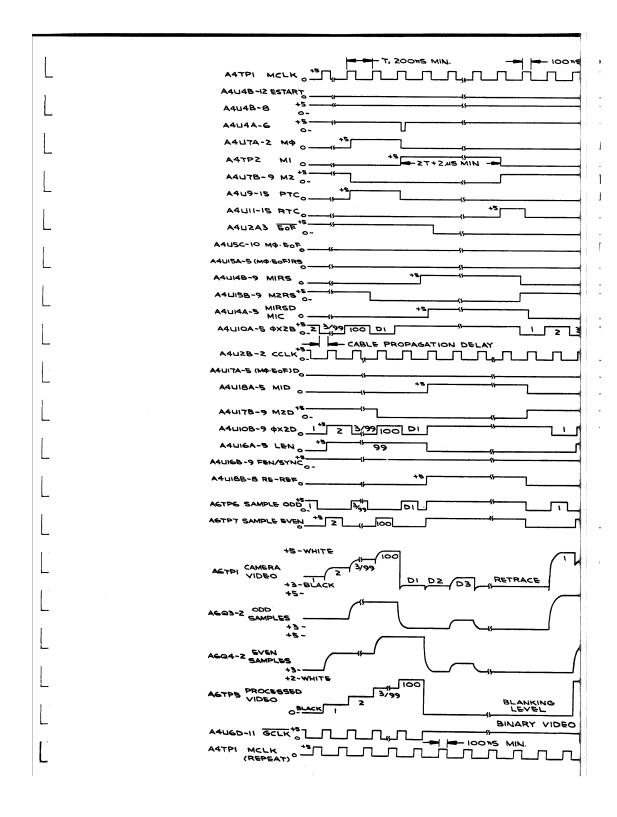

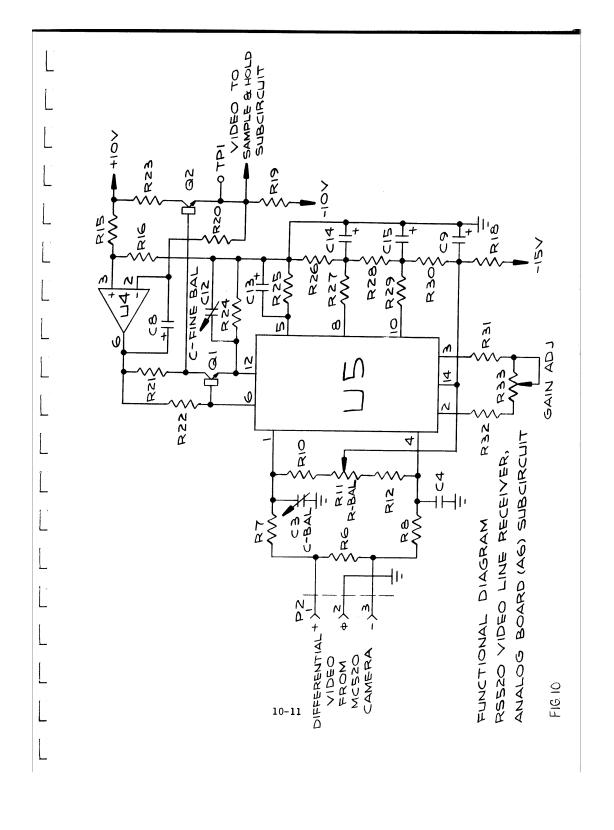

| 9          | Timing Diagram, RS520 Controller                                  | 10-10 |

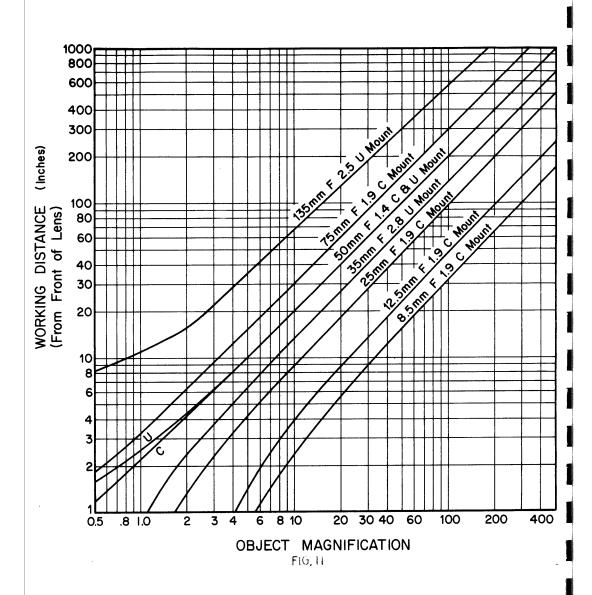

| 10         | Functional Diagram, RS520 Video Line Receiver                     | 10-11 |

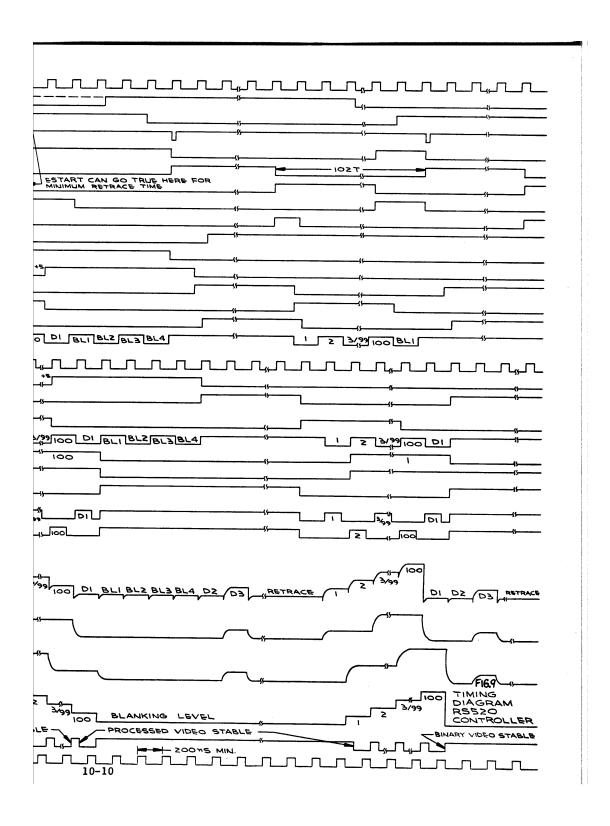

| 11         | Graph, Object Magnification Vs Working Distance                   | 10-12 |

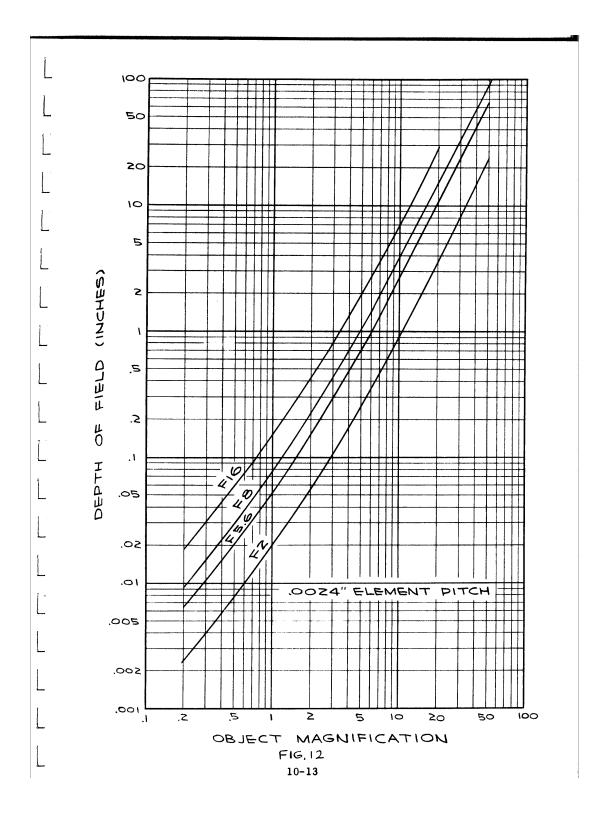

| 12         | Graph, Object Magnification Vs Depth of Field                     | 10-13 |

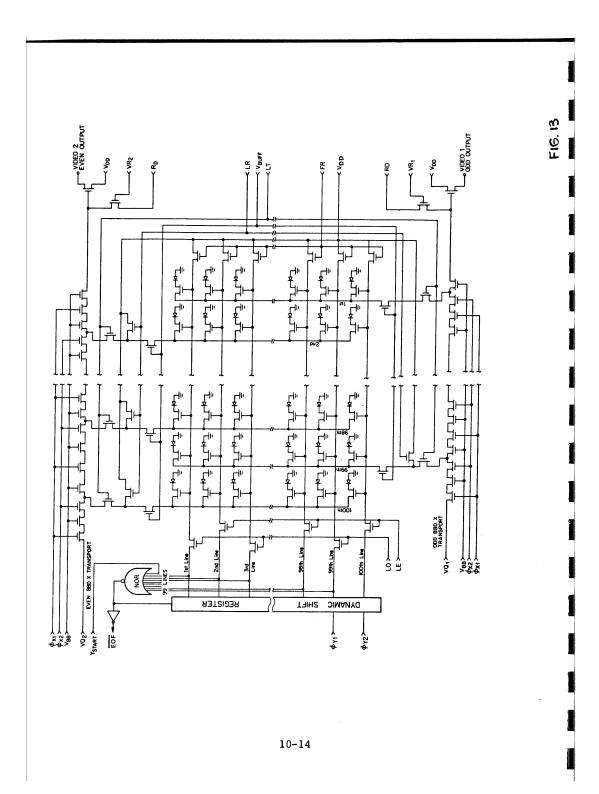

| 13         | Schematic Diagram, RA 100 x 100                                   | 10-14 |

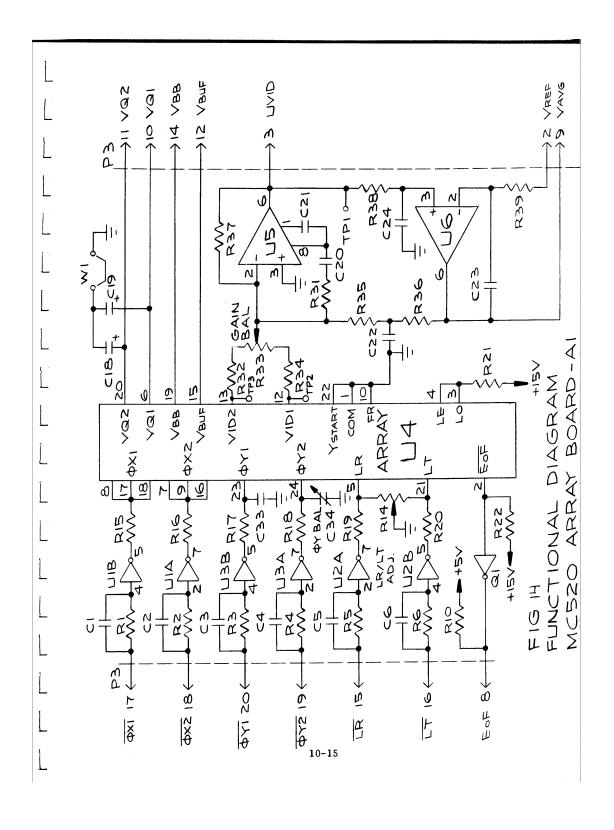

| 14         | Functional Diagram, MC520 Array Board-Al                          | 10-15 |

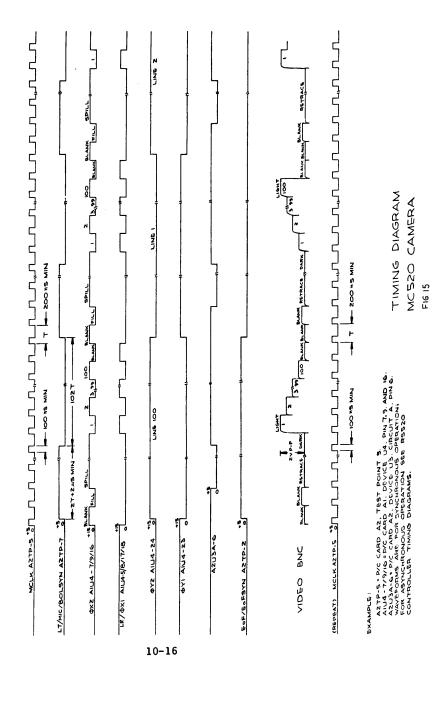

| 15         | Timing Diagram, MC520 Array Board-Al                              | 10-16 |

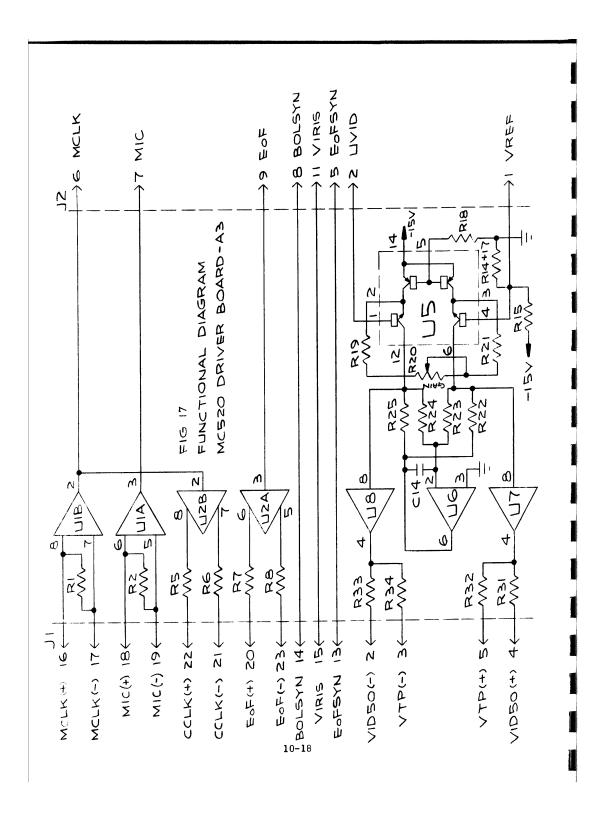

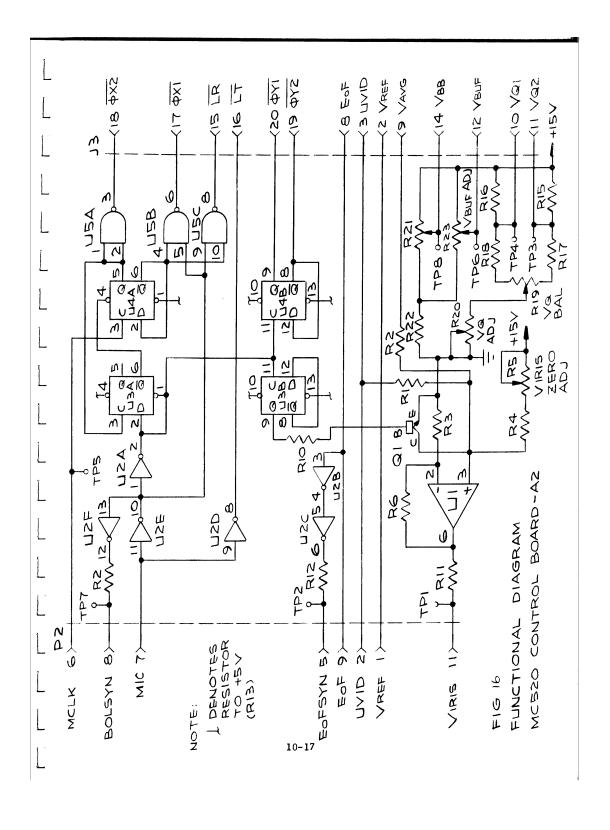

| 16         | Functional Diagram, MC520 Control Board-A2                        | 10-17 |

| 17         | Functional Diagram, MC520 Driver Board-A3                         | 10-18 |

| 18         | Not Used                                                          | 10-19 |

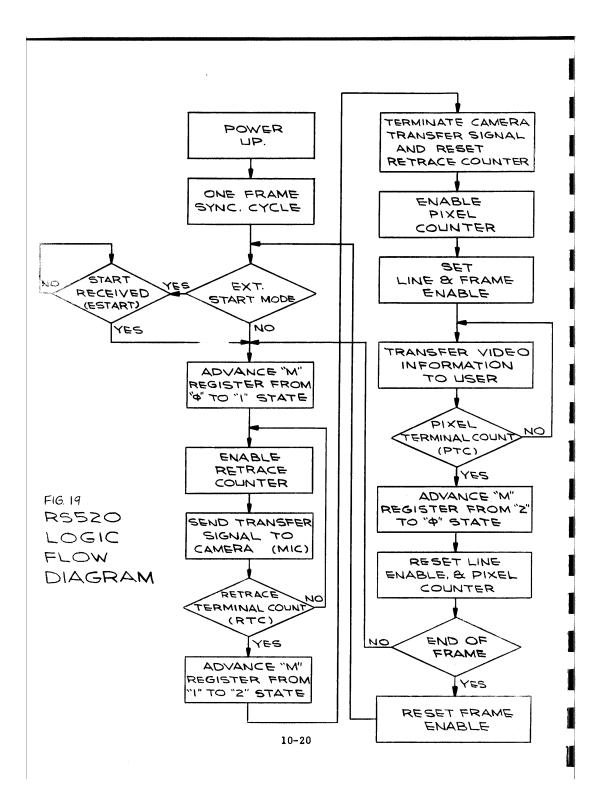

| 19         | RS520 Logic Flow Diagram                                          | 10-20 |

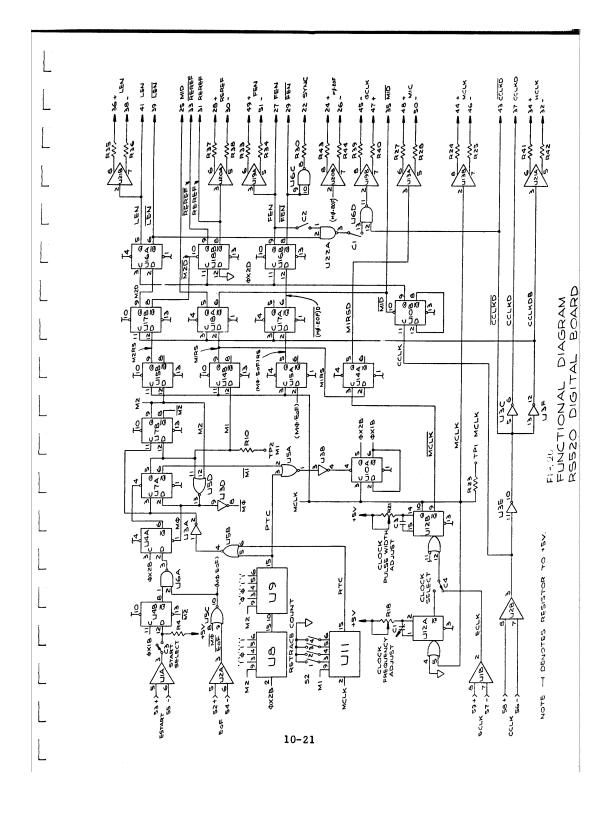

| 20         | Functional Diagram                                                | 10-21 |

| 21         | LM1496 - Amplifier/Switch                                         | 10-22 |

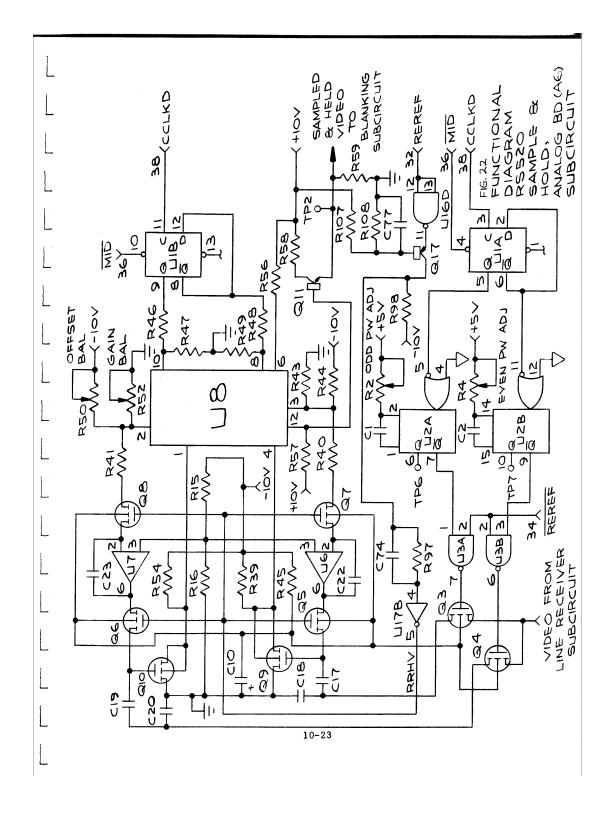

| 22         | Functional Diagram, RS520 Sample and Hold                         | 10-23 |

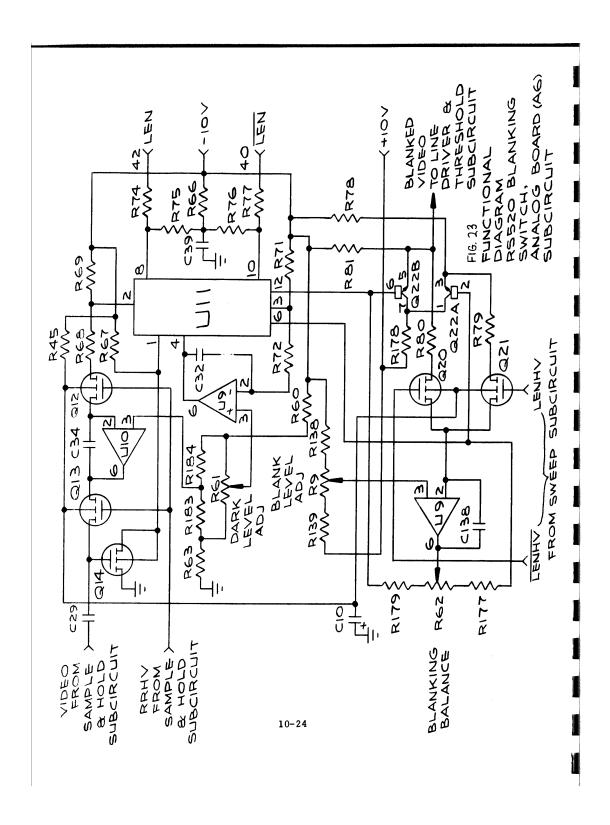

| 23         | Functional Diagram, RS520 Blanking Switch                         | 10-24 |

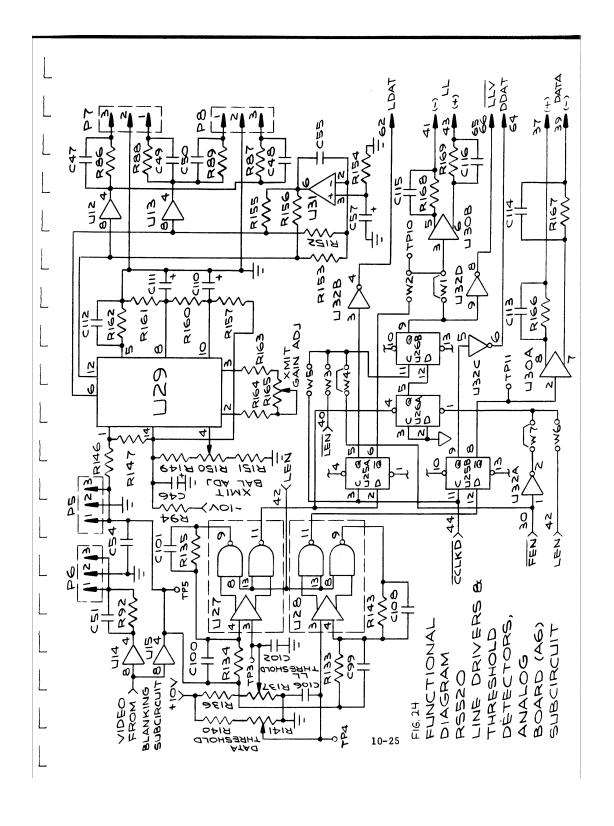

| 24         | Functional Diagram, RS520 Line Drivers and Threshold              |       |

|            | Detectors                                                         | 10-25 |

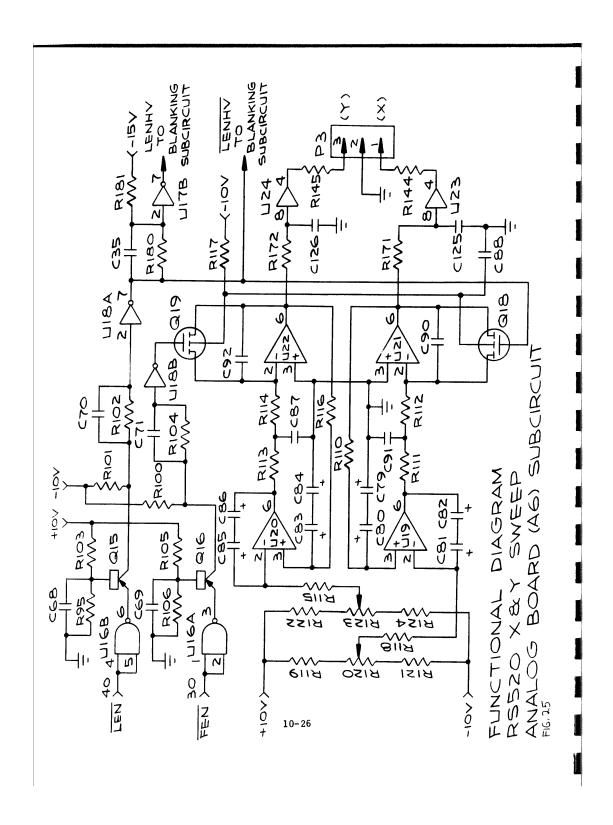

| 25         | Functional Diagram, RS520 X & Y Sweep · · · · · · · ·             | 10-26 |

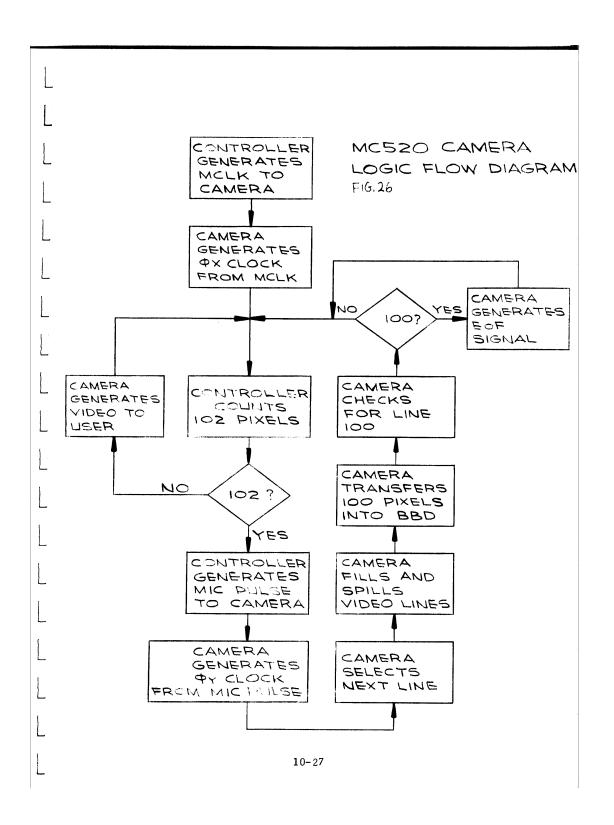

| 26         | MC520 Camera, Logic Flow Diagram                                  | 10-27 |

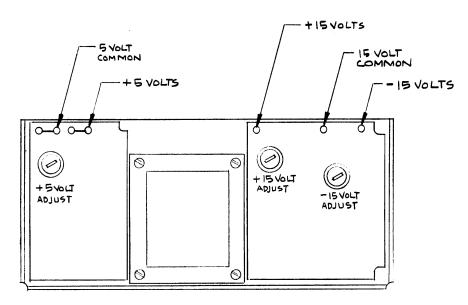

| 27         | RS520 Power Supply, Adjustment and Output Terminal                |       |

|            | Location                                                          | 10-28 |

| 28         | User Wiring for Data A and Data B Connectors                      | 10-29 |

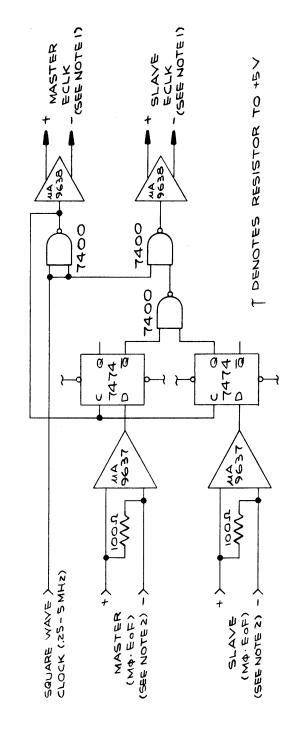

| 29         | Logic for Master Slave Operation of Multiple Cameras              | 10-30 |

| 30         | Pixel Blanking, Jumper Configuration                              | 10-31 |

| 1. |                | SECTION XI              |  |

|----|----------------|-------------------------|--|

| L  |                | LIST OF TABLES          |  |

|    | Table No.      | <u>Description</u> PAGE |  |

| Ľ  | I<br>II<br>III | S1 Switch Settings      |  |

| L  |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

|    |                |                         |  |

# SECTION XII

# LIST OF DRAWINGS

| Drawing No. | Description                                 | <u>Page</u> |

|-------------|---------------------------------------------|-------------|

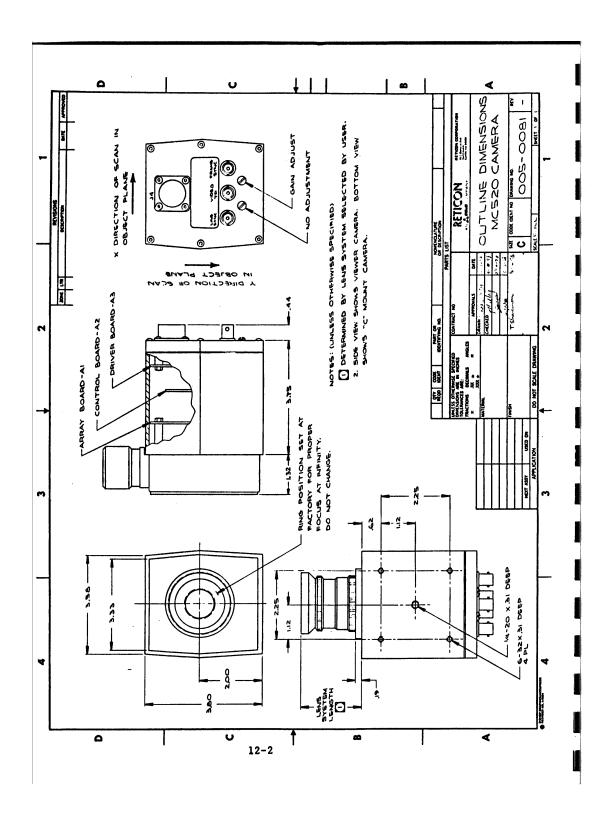

| 005-0081    | Outline Dimensions, MC520 Camera (Fig. 2)   | 12-2        |

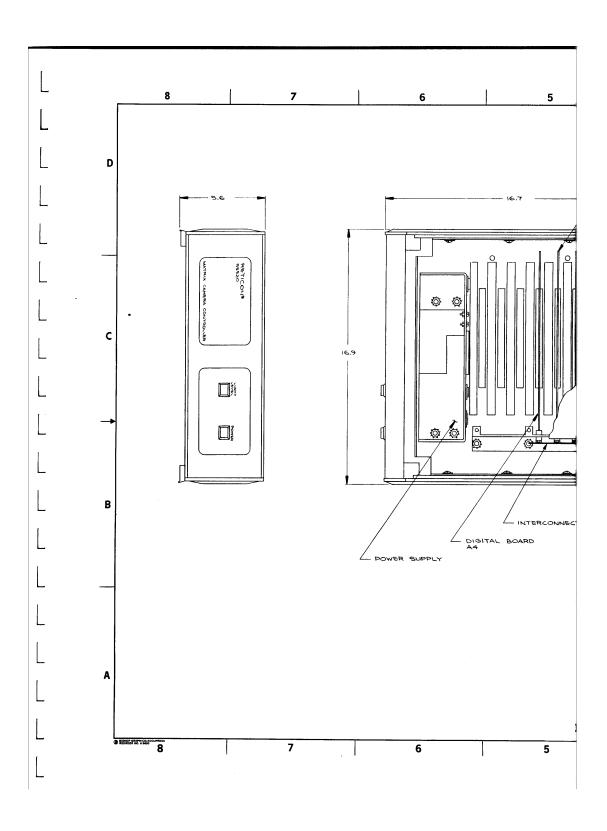

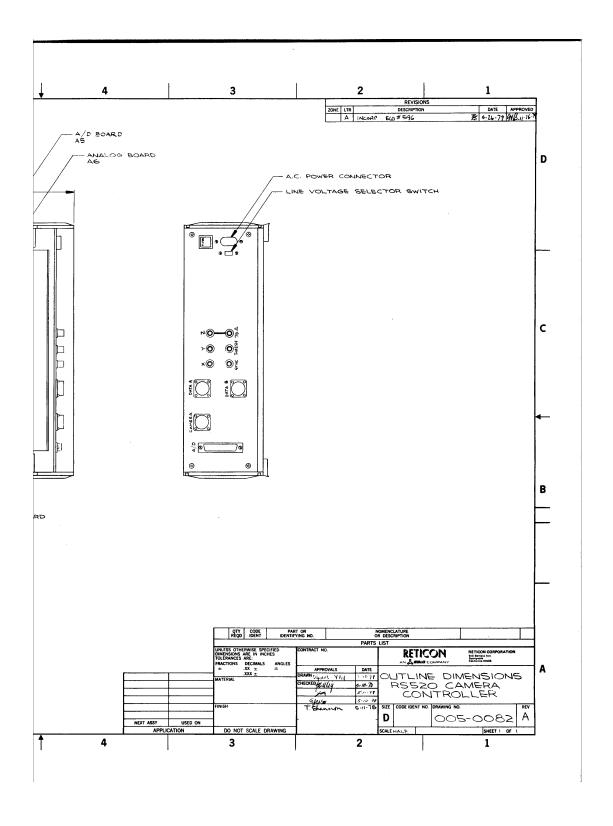

| 005-0082    | Outline Dimensions, RS520 Camera Controller | 12-3        |

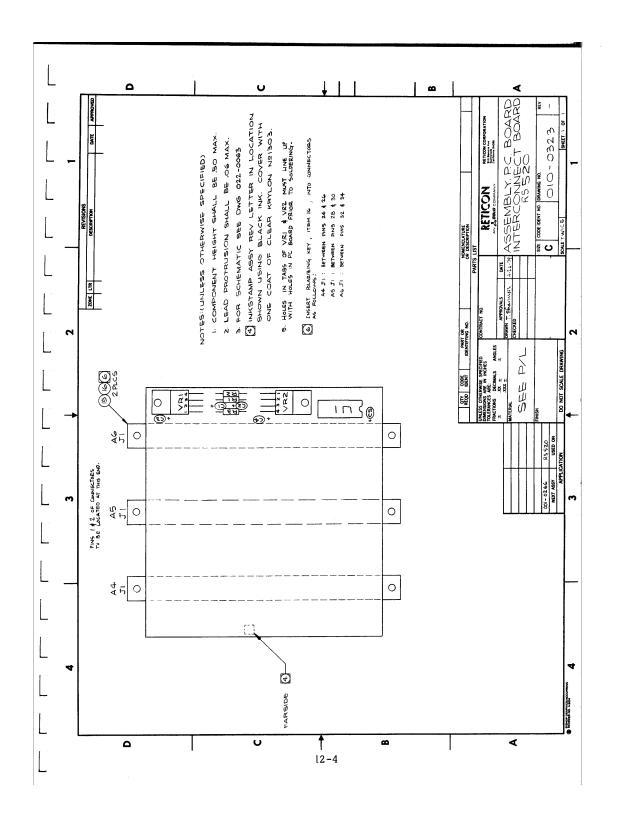

| 010-0323    | Assembly, P.C. Board, Interconnect Board    | 12-4        |

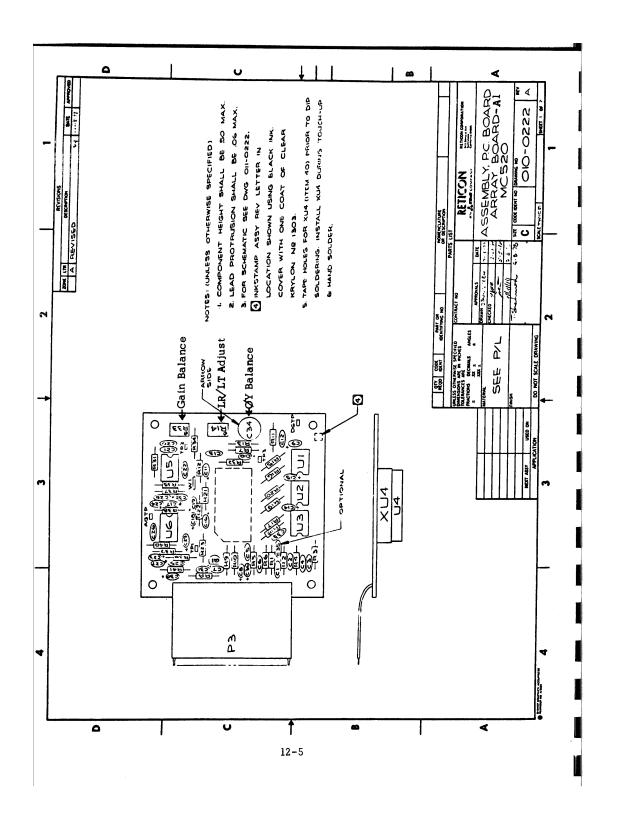

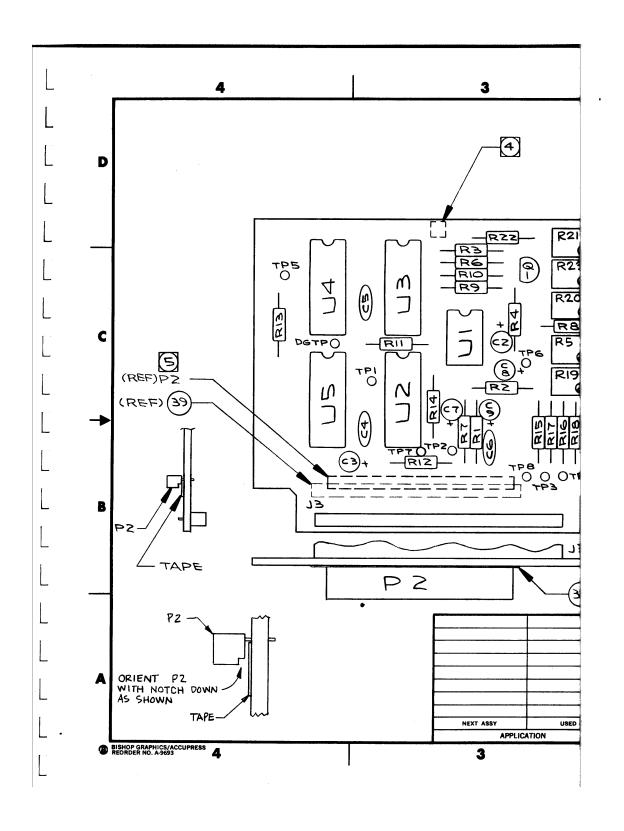

| 010-0222    | Assembly, P.C. Board, Array Board-Al        | 12-5        |

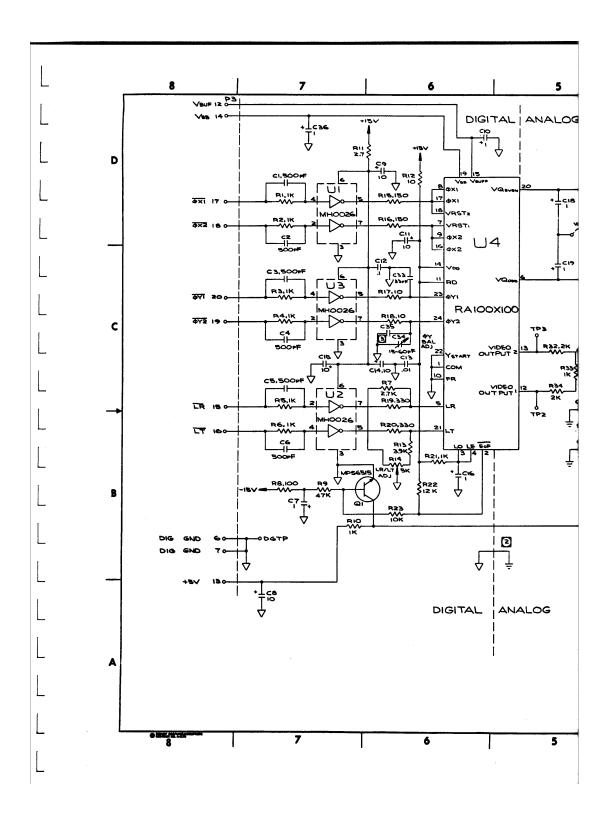

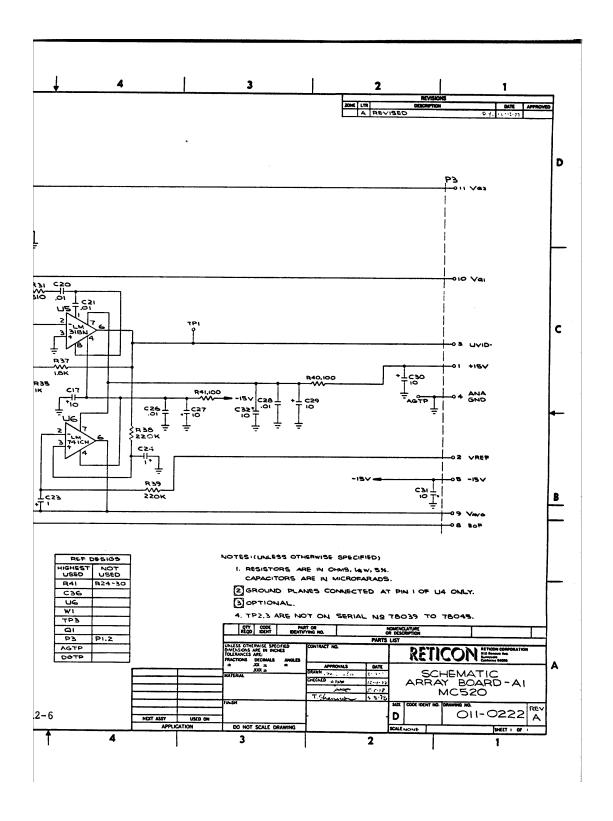

| 011-0222    | Schematic, Array Board-Al                   | 12-6        |

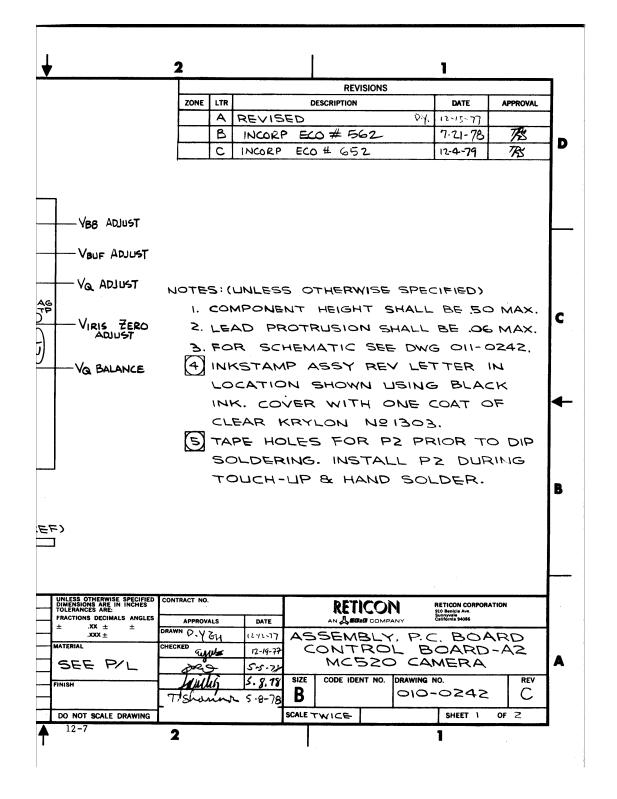

| 010-0242    | Assembly, P.C. Board. Control Board-A6      | 12-7        |

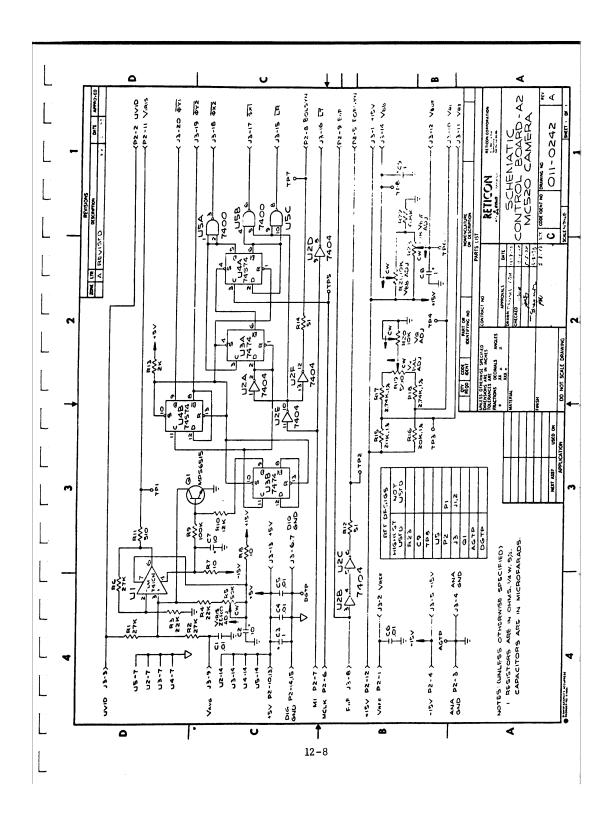

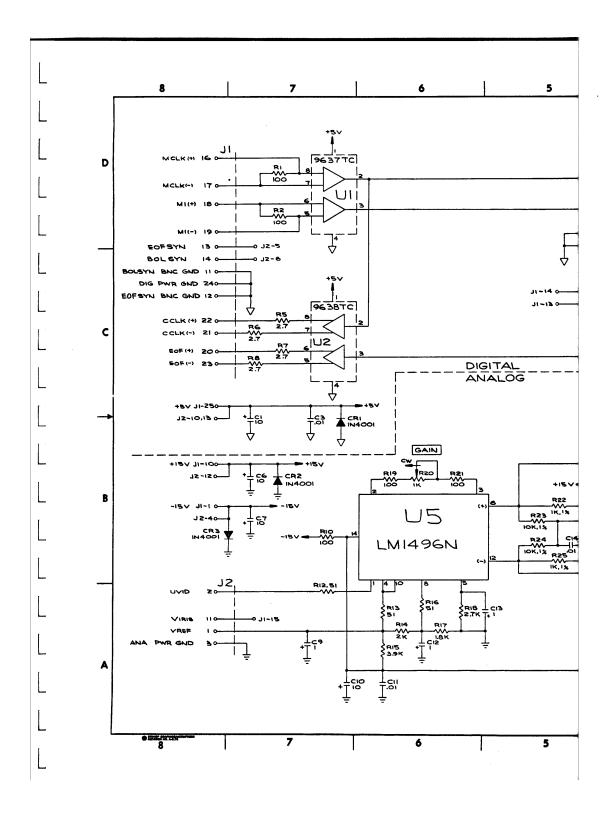

| 011-0242    | Schematic, Control Board-A2                 | 12-8        |

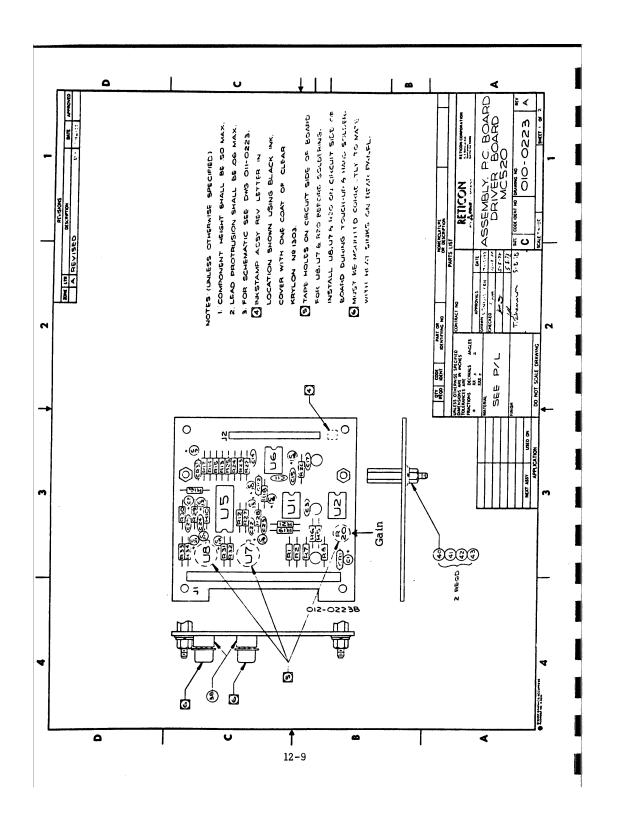

| 010-0223    | Assembly, P.C. Board, Driver Board-A3       | 12-9        |

| 011-0223    | Schematic, Driver Board-A3                  | 12-10       |

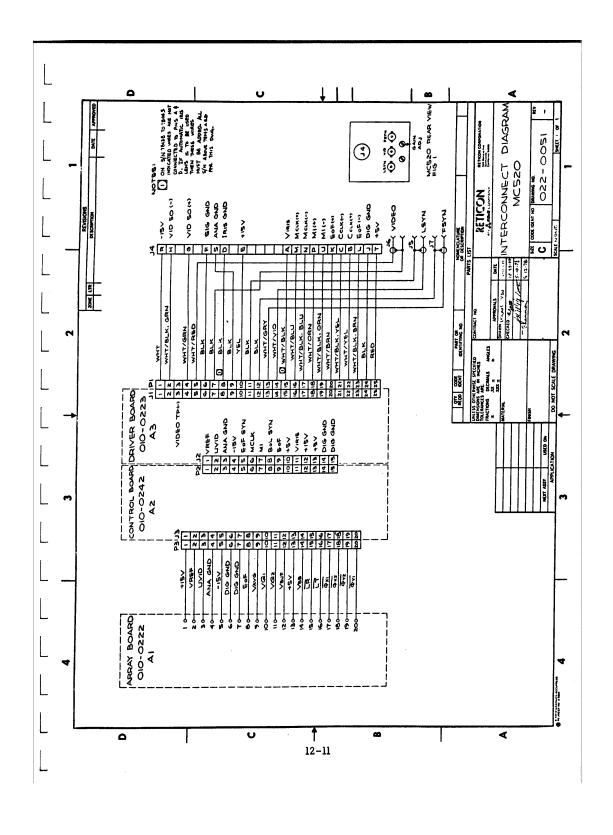

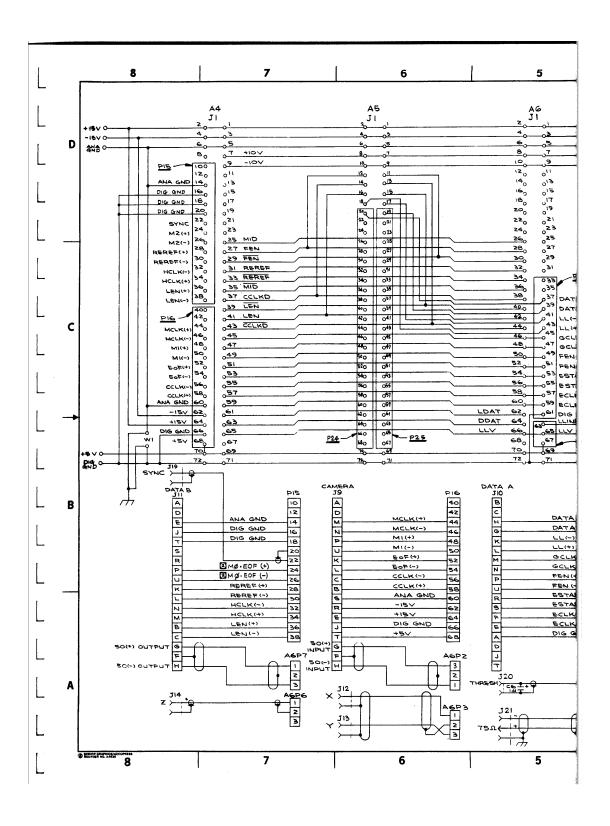

| 022-0051    | Interconnect Diagram, MC520                 | 12-11       |

| 010-0224    | Assembly, P.C. Board, Digital Board-A4      | 12-12       |

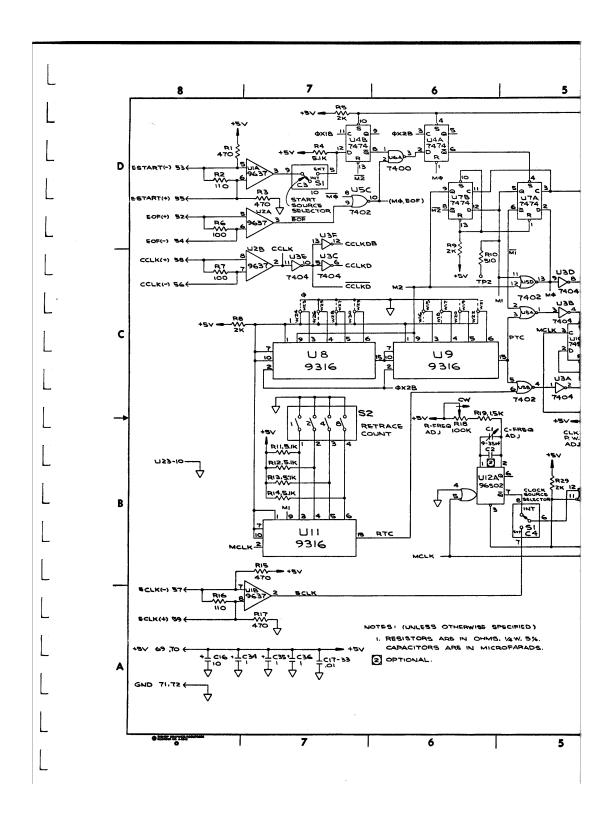

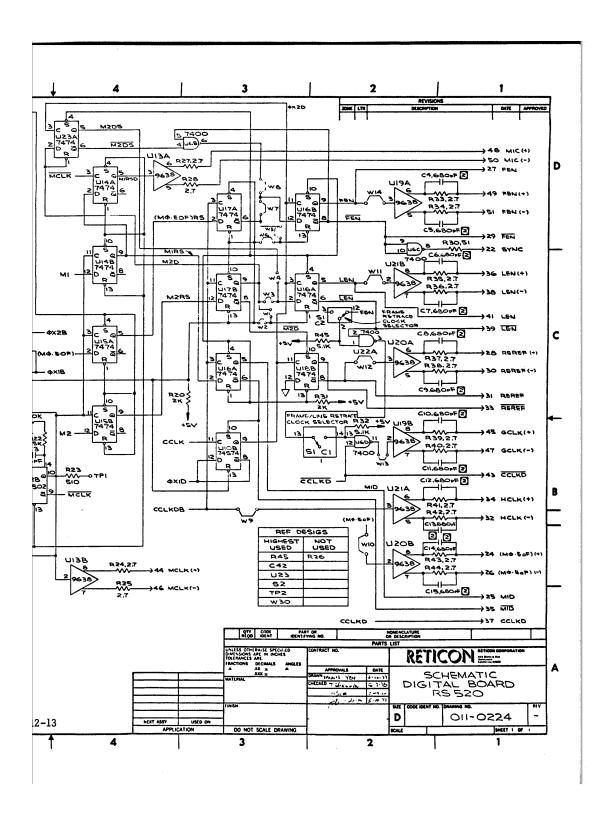

| 011-0224    | Schematic, Digital Board-A4                 | 12-13       |

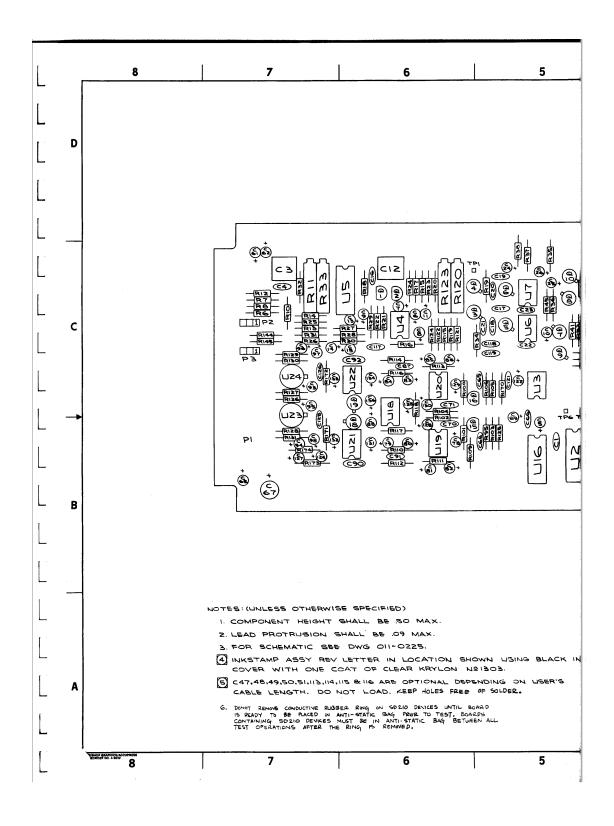

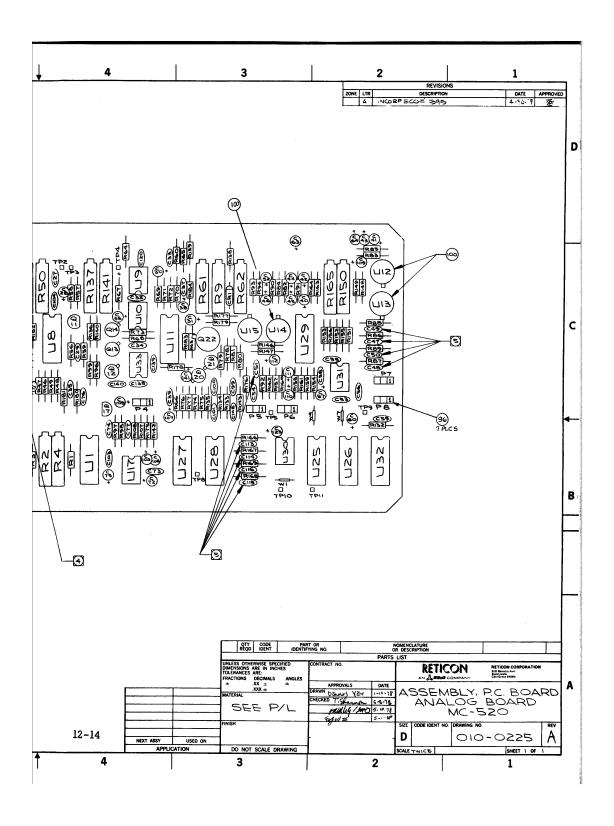

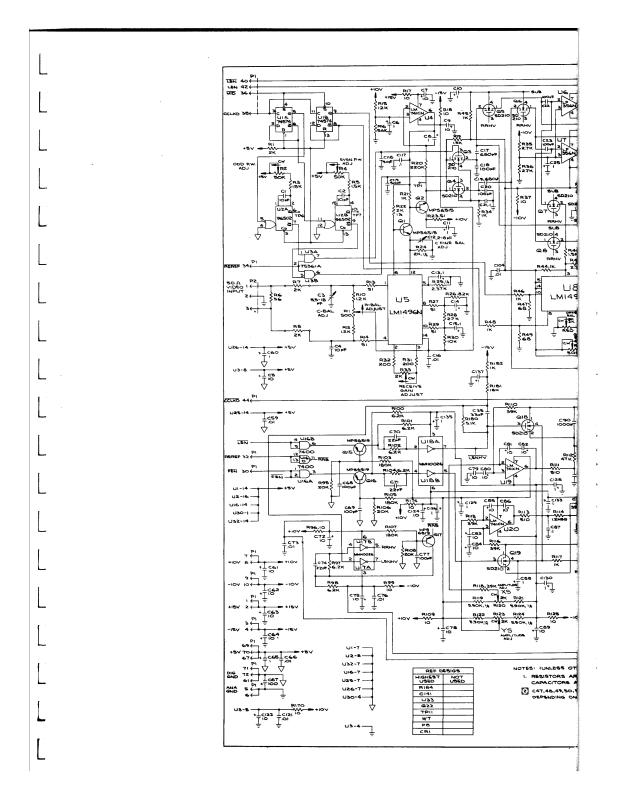

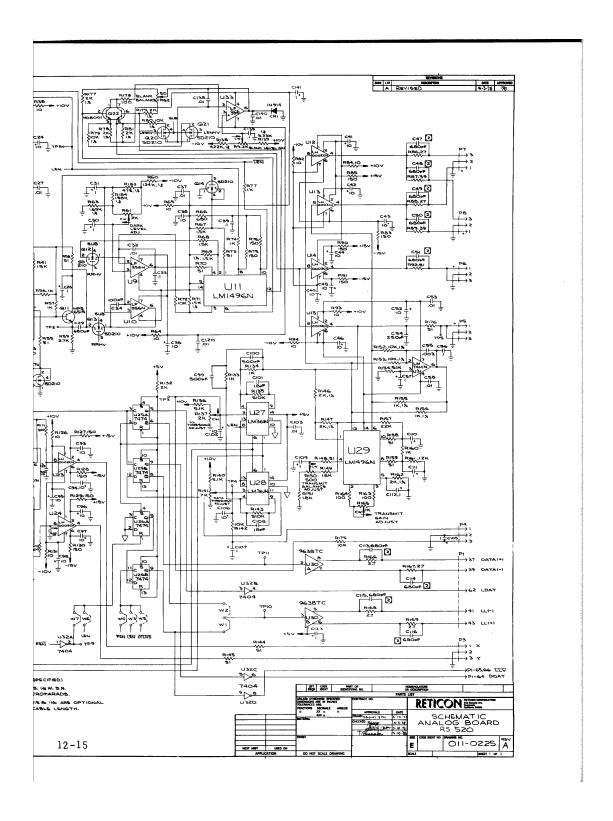

| 010-0225    | Assembly, P.C. Board, Analog Board-A6       | 12-14       |

| 011-0225    | Schematic, Analog Board-A6                  | 12-15       |

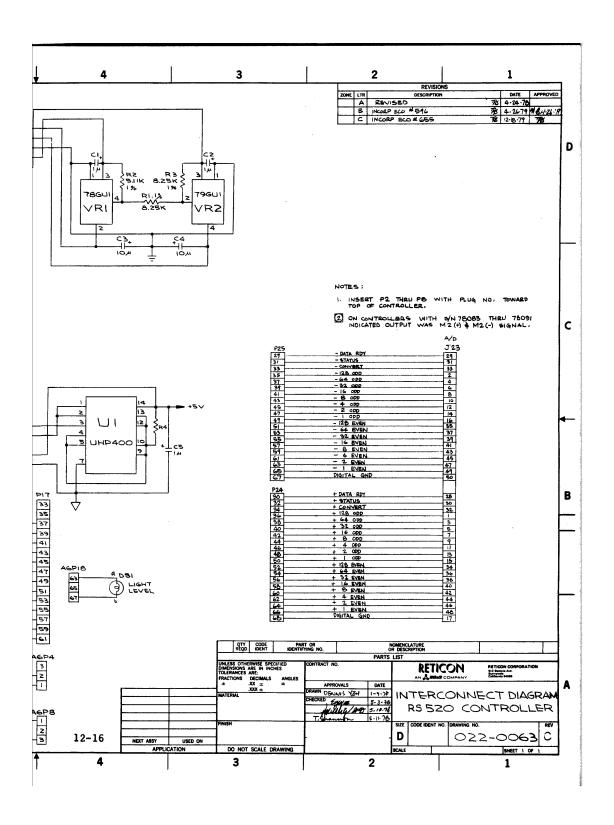

| 022-0063    | Interconnect Diagram, RS520                 | 12-16       |

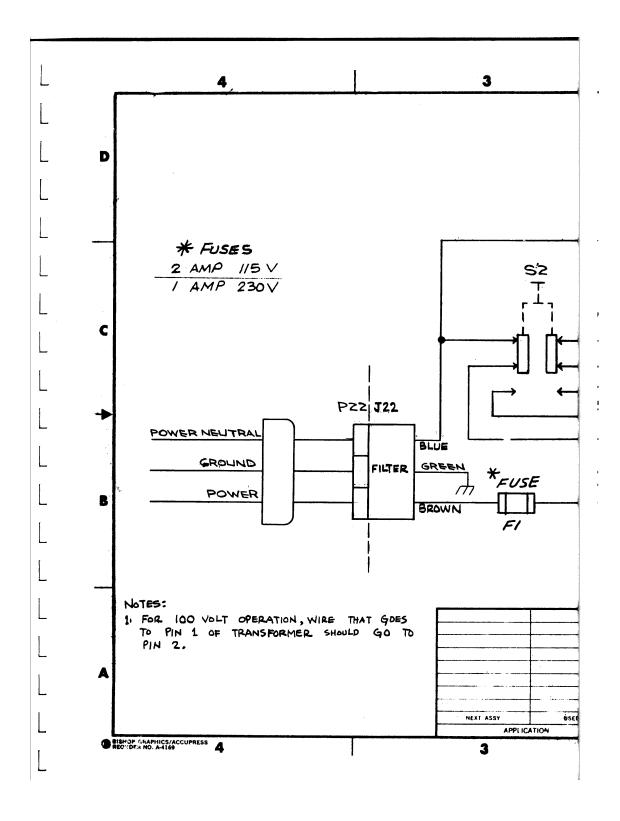

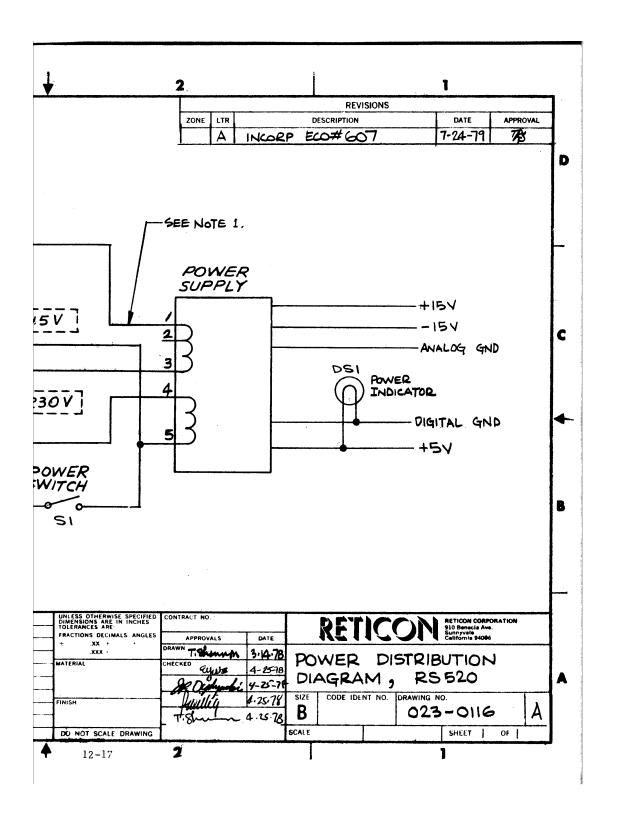

| 023-0116    | Power Distribution Diagram, RS520           | 12-17       |

# SECTION XIII LIST OF PHOTOGRAPHS

| Photograph<br><u>Number</u> | <u>Description</u>                                                           |  |

|-----------------------------|------------------------------------------------------------------------------|--|

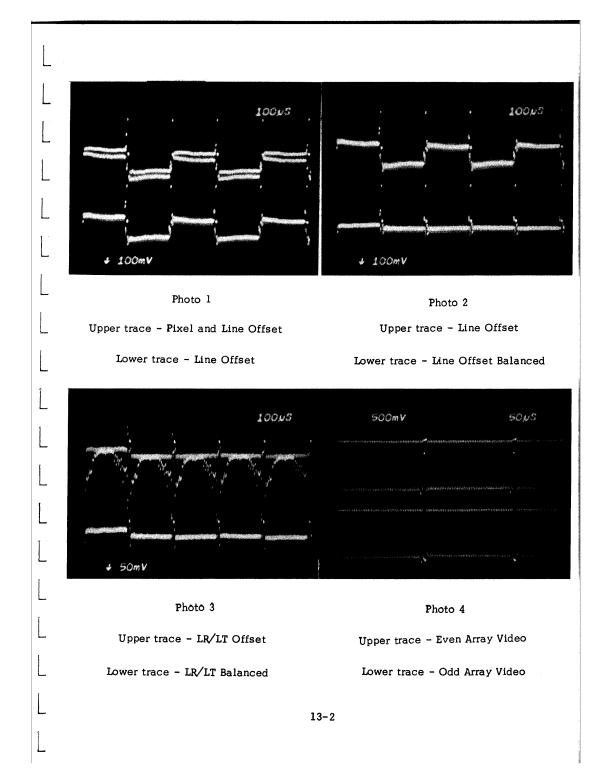

| 1                           | Upper Trace - Pixel and Line Offset  Lower Trace - Line Offset               |  |

| 2                           | Upper Trace - Line Offset  Lower Trace - Line Offset Balanced                |  |

| 3                           | Upper Trace - LR/LT Offset  Lower Trace - LR/LT Balanced                     |  |

| 4                           | Upper Trace - Even Array Video  Lower Trace - Odd Array Video                |  |

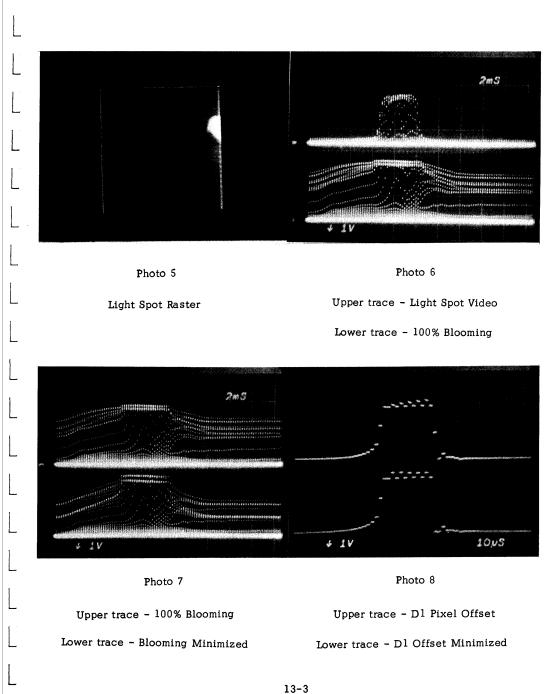

| 5                           | Light Spot Raster                                                            |  |

| 6                           | Upper Trace - Light Spot Video  Lower Trace - 100% Blooming                  |  |

| 7                           | Upper Trace - 100% Blooming  Lower Trace - Blooming Minimized                |  |

| 8                           | Upper Trace - D1 Pixel Offset  Lower Trace - D1 Offset Minimized             |  |

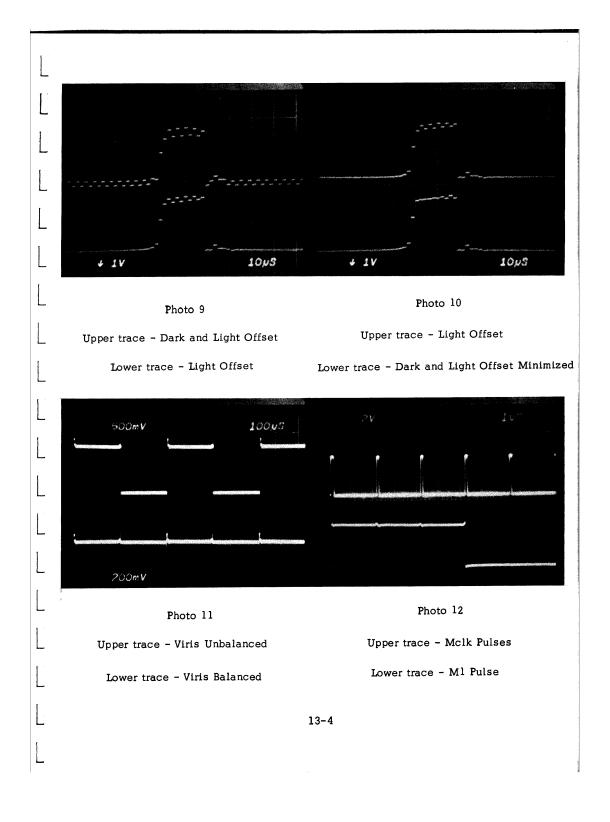

| 9                           | Upper Trace - Dark and Light Offset  Lower Trace - Light Offset              |  |

| 10                          | Upper Trace - Light Offset<br>Lower Trace - Dark and Light Offset Minimized. |  |

| 11                          | Upper Trace - Viris Unbalanced  Lower Trace - Viris Balanced                 |  |

| 12                          | Upper Trace - MCLK Pulses  Lower Trace - M1 Pulse                            |  |

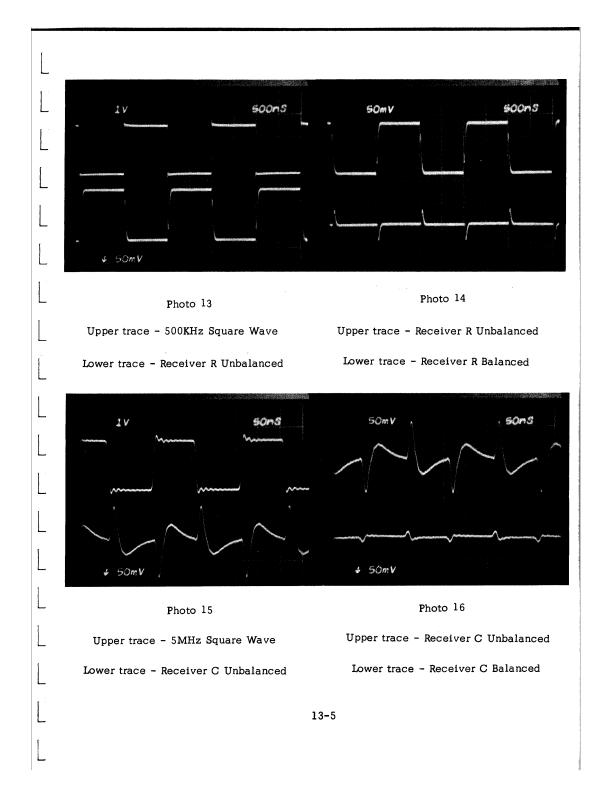

| 13                          | Upper Trace - 500 KHz Square Wave  Lower Trace - Receiver R Unbalanced       |  |

| 14                          | Upper Trace - Receiver R Unbalanced  Lower Trace - Receiver R Balanced       |  |

| 15                          | Upper Trace - 5 MHz Square Wave  Lower Trace - Receiver C Unbalanced         |  |

| 16                          | Upper Trace - Receiver C Unbalanced  Lower Trace - Receiver C Balanced       |  |

| Photograph<br>Number | Description                                                                                                            | PAGE |

|----------------------|------------------------------------------------------------------------------------------------------------------------|------|

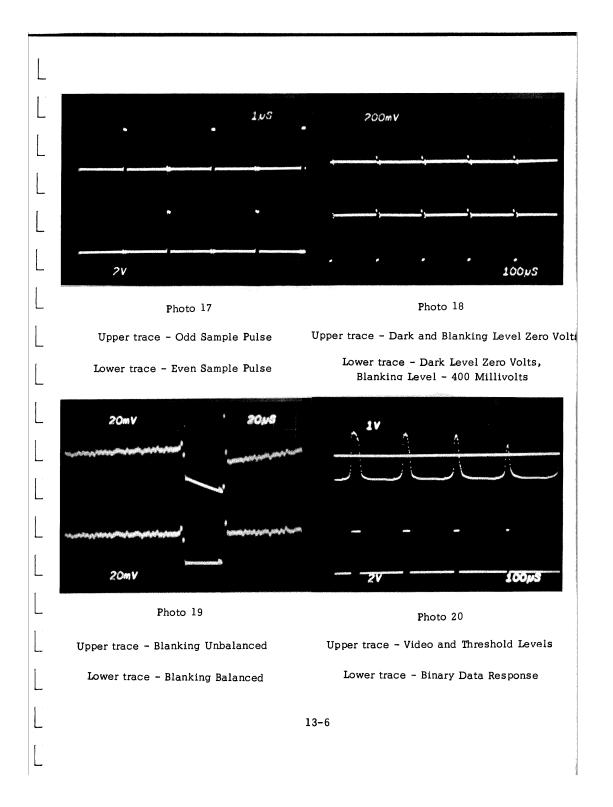

| 17                   | Upper Trace - Odd Sample Pulse  Lower Trace - Even Sample Pulse                                                        | 13-6 |

| 18                   | Upper Trace - Dark and Blanking Level Zero Volts  Lower Trace - Dark Level Zero Volts  Blanking Level - 400 Millivolts | 13-6 |

| 19                   | Upper Trace - Blanking Unbalanced  Lower Trace - Blanking Balanced                                                     | 13-6 |

| 20                   | Upper Trace - Video and Threshold Levels  Lower Trace - Binary Data Response                                           | 13-6 |

| 21                   | Upper Trace - Positive X Sweep  Lower Trace - Negative X Sweep                                                         | 13-7 |

| 22                   | Upper Trace - Positive Y Sweep                                                                                         | 13-7 |

#### SECTION I

#### SYSTEM STARTUP

#### 1.1 UNPACKING

Carefully remove the MC 520 Camera and RS 520 Controller from their shipping boxes and inspect them for any visual damage. Remove the two fasteners holding the controller top cover and inspect the interior for any damage. Assure that the two P/C boards in positions A4 and A6 are properly seated in their connectors.

Immediately report any shipping damage to the common carrier who delivered the equipment, and to Reticon, describing type and extent of damage. Reticon will then determine disposition and means of repair.

#### 1.2 POWERING UP

If no damage is found, install the camera lens, and connect the camera to the controller with the interconnecting cable provided. The camera connector is clearly marked on the controller rear panel, and a similar connector is easily recognized on the camera rear panel. Also connect the X,Y,Z, BNC outputs of the controller to a video monitor.

Make sure the line voltage selector switch on the controller rear panel is set for the required voltage, and the correct fuse is installed for the selected voltage, 2 amp. for 115 VAC and 1 amp. for 220 VAC.

Connect the controller to the AC line with the cable provided and depress the red power switch on the controller front panel. Note that the red indicator lamp illuminates.

#### 1.3 SYSTEM CHECKOUT

Perform a rough system checkout as follows: Set the lens to its smallest f/number, and point the lens at an intense light source such as a lamp, flashlight, or match flame. Note that the green light level indicator illuminates on the controller front panel.

Set the lens to its largest f/number and observe that a raster is on the monitor screen previously connected to the controller. Adjustment of the monitor contrast and focus controls may be necessary to see the raster clearly. Also, adjustment of the controller X and Y gain controls may be necessary to obtain a picture of proper size. These adjustments are clearly

marked on the card retainer plate at the edge of the controller A6 P/C board. Be sure not to adjust any other controls at this time.

"Look" at a well lighted scene with the camera, preferably an outdoor scene where sunlight assures enough illumination intensity. While observing the picture on the monitor, adjust the lens focus and f/number until a good picture is obtained. The data rate has been set at the factory to 1 MHz, which should give sufficient sensitivity for the outdoor scene on a sunny day. This frequency can be changed to any value between 0.25-5 MHz and these adjustments will be described in later sections of the manual. Observance of a good monitor picture concludes the rough system checkout.

#### SECTION II

#### INTRODUCTION

#### 2.1 MC520/RS520 SYSTEM

The MC520 Camera and RS520 Controller form the MC520/RS520 system which has many applications in high resolution, high speed, non-contact measurement of size, shape, and position.

These applications include:

Automatic Semiconductor Bonding

Laser Beam Profiling

Optical Surface Inspection

Finger/Palm Print Recognition

Blood Cell/Bacteria Colony Counting

Security Observation

Ink Print Quality Determination

Robot Arm Vision.

$$\operatorname{Basically}$  , any object or pattern may be inspected if it has contrast against its background.

#### 2.2 MC520 CAMERA - GENERAL

The MC520 Camera, Figure 1, is about the size of and operates similar to an ordinary photographic camera, with the exception that the film is replaced by an array of 10,000 photodiodes arranged in a 100 x 100 pattern on 2.4 mil (60  $\upmu$ m) center-to-center spacing.

The accuracy of measurement is determined by the field of view, which can range from a fraction of an inch to many feet depending on the working distance. For example, with a 5 inch (127mm) field of view, size differences of 0.05 inch (1.27mm) can be resolved, and with a 0.5 inch (12.7mm) field of view, 0.005 inch (127 $\mu$ m) can be resolved.

The field of view is imaged through the lens onto the photodiode array which is electronically scanned by signals from the RS520 Controller at data rates adjustable from  $0.25-5\,\mathrm{MHz}$ . (25-500 Frames/Second.)

#### 2.2.1 MC520 Mechanical Configuration

The MC520 is enclosed in a cast aluminum, environmentally protected enclosure with dimensions shown in Figure 2.

Camera construction is ruggedized for industrial environments, and with optional lens cover it is sealed against intrusion of dust and moisture.

The camera is available in both "C" and "V" versions. The "C" version will accept both "C" and "U" mount lenses, and one "C" mount lens with the following choice of focal lengths is supplied with the camera: 8.5, 12.5, 25, 50, or 75mm.

The "V" version provides a through the lens viewer similar to that of a reflex type photographic camera, enabling the operator to see the subject directly through the camera lens. A reticle in the viewer outlines the area actually scanned by the  $100 \times 100$  sensor array. The "V" camera accepts "U" mount lenses only.

Camera mounting is accomplished by means of four 6-32 screws, or a 1/4-20 threaded tripod mount, as shown in Figure 2.

# 2.2.2 MC520 Electronic Configuration

The MC520 electronics, Figure 3, are contained on three printed circuit cards mounted within the housing. These electronics process data from the  $100 \times 100$  sensor on command from the RS520 controller.

The array is scanned at a rate determined by clock pulses from the controller and may be set to any value from 0.25 -5MHz. The camera video output is a train of sampled-and-held pulses with an amplitude proportional to light intensity and frame integration time. A long scan time is desirable for high sensitivity, while a short time is desirable to obtain a sharp image of a rapidly moving object. The frame scan time can be set to any value between 2 and 40 milliseconds.

The specific characteristics of the application, such as light level, and rate of object motion, will determine the optimum value. See Section V for a discussion of optical parameters.

Signals enter and exit the camera through an 18 pin Bendix connector, J4, located on the camera rear panel, and additionally three BNC connectors provide test points for setup and servicing the camera. These test points and their functions are shown in Figure 2. A more detailed discussion of camera electronics will be found in Section VII, Principles of Operation.

#### 2.3 RS520 CONTROLLER - GENERAL

The RS520 Controller, Figure 4, provides electronics P/C boards, power supply, and data I/O connectors to operate the MC520 camera when it is connected to the camera I/O connector.

Three spare P/C board positions and additional power are available to the user for building his own system within the controller housing if desired. See Section IV for power specifications.

# 2.3.1 RS 520 Mechanical Configuration

The RS 520 Controller is enclosed in a bench top cabinet with dimensions shown in Figure 5. Optional standard 19 inch rack mounting hardware is also available if desired.

# 2.3.2 RS 520 Electronic Configuration

RS 520 electronics, Figure 6, are contained on two P/C boards in positions A4 and A6. Position A4 is the Digital Board which generates clock and synchronizing signals to the camera, and re-synchronizes with signals from the camera to control the video processing and sweep circuits on the Analog Board in position A6. An additional P/C board position, A5, is present for A/D option P & S.

An interconnect P/C board on the rear of the P/C board connector bracket contains  $\pm$  10 volt regulators for the A6 board, and also provides signal connection between the A4, 5, and 6 board connectors. The controller will operate the MC 520 camera at data rates from 0.25-5MHz, while providing video and synchronizing signals for transmission over up to 100 feet (30m) of additional cable between controller and users equipment. The controller also provides X,Y, and Z output signals for direct connection to a video monitor. A more detailed discussion of controller electronics will be found in Section VIII, Principles of Operation.

#### SECTION III

# MC 520 CAMERA SPECIFICATIONS

#### 3.1 MECHANICAL

Dimensions  $3.58 \times 3.8 \times 3.75$  inches  $(9.09 \times 9.65 \times 9.53 \text{ cm.})$

Mounting Four 6-32 screws on a 2.25 inch (57.15 mm)

square, or a 1/4-20 threaded tripod mount.

Weight 1.5 lbs. (0.68Kg).

# 3.2 OPTICAL

Array Size 10,000 pixels arranged in a 100 x 100 matrix.

Spacing 2.4 mils (60  $\mu$  m) center-to-center in X or Y

direction.

Active Area  $0.24 \times 0.24$  inches (6 x 6 mm.)

Saturation Exposure  $0.25 \mu \text{ w-sec/cm}^2 \oplus 2870 \text{K typical}$ . See

Figure 7 for transfer characteristic.

Blooming Characteristic See Figure 8 and description of measurement

in 5.2.2.

# 3.3 ELECTRICAL

# 3.3.1 BNC Connectors

#### 3.3.1.1 Video

The Video BNC is connected to one side of the differential line driver output, hence its signal to noise ratio will not be as good as at the controller after the differential line receiver. As a result, the Video BNC output is intended as a test point only to assure that the camera is generating video properly to the controller.

Dark Level

0 volts  $\pm 30 \, \text{mv}$ . 0.25-5 MHz, determined by clock frequency Scanning Rate

from controller.

3.3.1.2 Frame Sync

> Level +2.4 volts min. during line 100, +0.8 volts

> > max. during lines 1-99.  $1K\Omega$  load min.

100 line intervals. Pulse Period

Pulse Width One line interval.

3.3.1.3 Line Sync

> +2.4 volts min. during line retrace, +0.8 volts Level

max. after retrace.  $1\mbox{K}\,\Omega$  load min.

Pulse Rate Line rate.

Equal to width of M1C pulse from controller, Pulse Width

adjustable from 3 to 15 pixel periods in controller.

3.3.2 Bendix Connector, J4

The Bendix connector, on the camera rear panel, carries power, video, and sync signals between the camera and controller. Cable length can be determined from the following formula:

> length in feet =  $\left[\frac{227}{\text{FMHz}}\right]$ -16 or 75 feet, whichever is less.

FMHz is the maximum data rate used. Recommended cable type is Belden 8774. An 8 foot length with connectors is supplied with the system. Other lengths are optionally available.

# 3.3.2.1 Analog Signals

The differential video output is designed to be received by the controller analog line receiver. The following video specifications are at the output of this receiver, which removes connecting cable induced noise. The output of the receiver is on the controller A6 P/C board, Test Point 1.

3.3.2.1.1 Video (+) and (-) Outputs (Exits camera on pins G & H respectively; specs are at TP-1 as described above)

Saturated Light Level 2 volts p-p, AC coupled, averaging around

dark level.

Dark Level +3 volts nominal

Dynamic Range ≥ 200:1

Ramdom Noise ≤ 10 mv p-p

Coherent Noise ≤ 200 mv p-p

Scanning Rate 0.25-5MHz

Settling Time ≤ 120 ns to 95% of saturation level.

DC Restoration Provided by controller video processing.

# 3.3.2.2 Digital Signals

The camera digital I/O signals are transmitted or received by  $\mu$  A9638 or  $\mu$  A9637 line transmitters or receivers respectively. The camera provides 100  $\Omega$  terminations for signals received, and the R5520 Controller provides 100  $\Omega$  terminations for camera transmitted signals.

# 3.3.2.2.1 MCLK (+) and (-) Inputs (Pins M and N respectively)

Level This is the X scan clock input to be driven by a  $\,\mu\,A9638$  line

transmitter or equivalent device meeting EIA-RS-422 specifi-

cations.

Pulse Rate 0.25-5MHz, set by controller master clock frequency control.

Pulse Width 100 ns minimum, set by controller master clock pulse width

control.

# 3.3.2.2.2 M1C(+) and (-) Inputs (Pins P and U respectively)

Level This is the Y scan clock input to be driven by a  $\,\mu$  A9638

line transmitter or equivalent device meeting EIA-RS-422

specifications.

Pulse Rate Line scan rate, 25-500 per second depending on X scan

rate set by controller.

Pulse Width Set by controller retrace counter and adjustable 3-15 pixel

intervals. Count is determined by:

Count minimum = 2 (FMHz +1), where FMHz is maximum X scan rate required. For 5 MHz, this count

would be 2(5+1) = 12 minimum.

# 3.3.2.2.3 CCLK (+) and (-) Outputs (Pins B and C respectively)

Level This is a re-transmission of the camera MCLK input which

is used by the controller to re-synchronize the data and remove cable propagation delay differences. It is received by a  $\mu \text{A9637}$  line receiver or equivalent device meeting

EIA-RS-422 specifications.

Pulse Rate Same as MCLK signal. (3.3.2.2.1)

Pulse Width Same as MCLK signal. (3.3.2.2.1)

#### 3.3.2.2.4 EOF (+) and (-) Outputs (Pins K and L respectively)

Level This is the End of Frame sync signal output generated

by the 100 x 100 array, and is used to synchronize the controller. It is received by a type  $\mu \, A9637$  or equivalent

line receiver meeting EIA-RS-422 specifications.

Pulse Rate Frame Rate, 25-500 per second.

Pulse Width One line interval (true during line 100).

#### 3.3.2.3 Power

The camera requires nominally +5, +15, and -15 volts which is supplied by the controller when the camera is connected to it. Voltage tolerances, regulation, and current requirements are as follows:

# 3.3.2.3.1 +5 Volts and Digital Ground (Pins T and J respectively)

Voltage Setting +5 volts  $\pm$  5%

Voltage Regulation ≥ 1%

Current 250 ma maximum

| - |           |                         |                           |                                   |  |

|---|-----------|-------------------------|---------------------------|-----------------------------------|--|

|   | 3.3.2.3.2 | +15 Volts (Pin E)       |                           |                                   |  |

| L |           | Voltage Setting         |                           | +15 volts ± 5%                    |  |

| L |           | Voltage Regulation      |                           | ≥ 1%                              |  |

|   |           | Current                 |                           | 150 ma maximum                    |  |

|   | 3.3.2.3.3 | -15 Volts and Analog Gr |                           | round (Pins R and S respectively) |  |

| L |           | Voltage Setting         |                           | -15 volts ± 5%                    |  |

| L |           | Voltage Reg             | gulation                  | ≥ 1%                              |  |

| 1 |           | Current                 |                           | 100 ma maximum                    |  |

| L | 3.4       | ENVIRONMENTAL           |                           |                                   |  |

| L | <u> </u>  | HIVI CIVII              | 411 41 44                 |                                   |  |

|   | 3.4.1     | Temperature             |                           |                                   |  |

| - |           | Operating A             | Ambient                   | 0 to 50°C                         |  |

| L |           | Storage                 |                           | -20 to +100 <sup>o</sup> C        |  |

|   | 3.4.2     | Humidity                |                           |                                   |  |

|   |           | 90% R.H. I              | Non-Condens               | sing, Camera is splash resistant  |  |

|   | 3.5       | ADJUSTMENTS             |                           |                                   |  |

| L | 3.5.1     | <u>Internal</u>         |                           |                                   |  |

| L | 0.0.1     | Al Board                | LR/LT (R14                | ), Gain Balance (R33)             |  |

|   |           |                         | ØY Balance                |                                   |  |

|   |           | A2 Board                | VQ (R20), V<br>VBB (R21), | /Q Balance (R19)<br>VBUF (R23)    |  |

| L |           |                         | VIRIS Zero                |                                   |  |

|   |           | External                |                           |                                   |  |

|   |           | A3 Board                | Gain (R20)                |                                   |  |

| L |           |                         |                           |                                   |  |

| L |           | 3-5                     |                           |                                   |  |

|   |           |                         |                           |                                   |  |

#### SECTION IV

# RS520 CONTROLLER SPECIFICATIONS

#### 4.1 MECHANICAL

Dimensions  $16.9 \times 5.6 \times 16.7$  inches  $(42.93 \times 14.22 \times 42.42 \text{ cm.})$

Mounting Bench top, or with optional hardware can be mounted

in standard 19 inch rack.

Weight 22.5 lbs. (10.2 kg)

# 4.2 ELECTRICAL

#### 4.2.1 BNC Connectors

# 4.2.1.1 Z Output

The Z output is a series of sampled and held video pulses having amplitudes proportional to the light intensity on each pixel and the frame integration time. Specifications are with a 50 ohm termination.

Blank Level Adjustable +0.1 volts to -1 volt, Drift≤0.5mv/°C.

Dark Level Adjustable +0.1 volts to -1 volt, Drift ≤0.5mv/°C.

Saturation Level Adjustable to +1 volt above dark level.

Dynamic Range ≥ 200:1

Random Noise ≤ 5 mv p-p

Coherent Noise ≤ 50 mv p-p

Data Rate 0.25 -5MHz

Settling Time  $<50\,\mathrm{ns}$  to 95% of saturation level.

The X,Y, and Z outputs may be directly connected to a monitor for presentation of the camera field of view.

### 4.2.1.2 Y Output

The Y output is a linear ramp synchronized with the camera frame rate, and is intended to provide Y axis sweep for a monitor presentation of the camera field of view. Specifications are with 50 ohm termination.

Retrace Level 0 volts ± 50 mv

Peak Ramp Level Adjustable to ± 1 volt

Linearity Within 2% of best straight line.

Ramp automatically maintains level with scan rate changes. Y output is not usable if camera external start mode is used and camera is stopped for longer than  $\left\lceil \frac{1}{\text{FMHz}} \right\rceil$  milliseconds, where FMHz is data rate;

i.e., at 5 MHz, maximum stop interval would be  $\frac{1}{5}$  millisecond.

# 4.2.1.3 X Output

The X output is a linear ramp synchronized with the camera line rate, and is intended to provide X axis sweep for a monitor presentation of the camera field of view. Specifications are with  $50\,\mathrm{ohm}$  termination.

Retrace Level 0 volts  $\pm 50 \,\text{mv}$

Peak Ramp Level Adjustable to ± 1 volt

Linearity Within 2% of best straight line.

i.e., at 0.5 MHz, maximum stop interval would be  $\frac{1}{0.5}$  ms. = 2 milliseconds.

#### 4.2.1.4 75 $\Omega$ Output

The 75 ohm output is a differential presentation of the Z output (4.2.1.1) and is intended for driving up to 100 feet of cable. Recommended cable is Belden 9272 or equivalent. Specifications are with 75 ohm termination and differential output. Shield should be connected to users chassis ground, and the analog ground in either the Data A or Data B connector to user signal ground.

Blank Level Adjustable +0.2 to -2 volts, Drift  $\leq 0.5$ mv/ $^{\circ}$ C.

Dark Level Adjustable +0.2 to -2 volts, Drift  $\leq 0.5$  mv/ $^{\circ}$ C.

Saturation Level Adjustable to +2 volts above dark level.

Dynamic Range ≥ 200:1

Random Noise

$\leq 10 \, \text{mv p-p}$

Coherent Noise

≤ 100 mv p-p

Data Rate

$0.25 - 5 \, MHz$

Settling Time

< 50 ns to 95% of saturation level.

$\label{eq:control_state} If the 75 ohm output is used, the differential output on Data B connector cannot be used simultaneously.$

#### 4.2.1.5 Threshold

The threshold output is the DC level used by the Data level detector to determine the data threshold. This output is presented through a  $10\,\mathrm{K}\Omega$  resistor, and must not be loaded if accurate threshold measurements are to be obtained.

Level

Adjustable 0 to +2 volts

If the threshold level is compared to the unterminated Z output, a  $\pm$  30 mv error in threshold setting can occur. A more accurate measurement can be made by comparing the threshold level to the video at TP-5 on the A6 board.

#### 4.2.1.6 Sync

The Sync output is the controller Frame Enable signal presented through a 50 ohm resistor from a TTL buffer. Specifications are with 1K  $\Omega$  load.

Level

+2.4 volts minimum during Frame Enable, +0.8 maximum

during line 100 retrace.

Pulse Rate

Frame Rate, 25-500 per second.

Pulse Width

100 line intervals

#### 4.2.2 Bendix Connectors

#### 4.2.2.1 Data A Connector

The Data A Connector I/O signals are plug to plug compatible with Reticon Automatic Measurement Systems. These signals of course can be

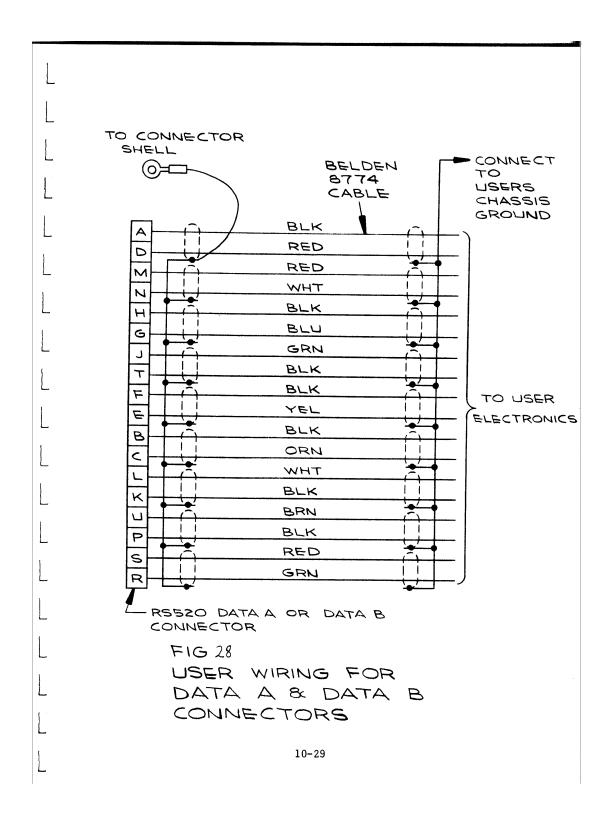

connected directly to the users equipment as well. See Figure 9 for a timing diagram showing their relationship to the camera video. All signals in this connector are digital and differential. Up to 100 feet of Belden 8774 cable may be used, and all shields should be connected to the connector shells only. See Figure 28.

# 4.2.2.1.1 Digital Ground (Pin A)

$\qquad \qquad \text{This is the common digital return for all signals in the } \\ \text{Data A connector.}$

# 4.2.2.1.2 ECLK (+) and (-) Inputs (Pins E and F respectively)

Level To be driven by a µA9638 line transmitter or equivalent

device meeting EIA-RS-422 specifications. This signal will synchronize the camera with the users external clock. Switch selection of external clock (ECLK) must be made on Switch S1-C4 of the controller A4 P/C board.

See Table I, "Sl switch settings."

Pulse Rate 0.25 - 5 MHz

Pulse Width ≥ 100 ns

# 4.2.2.1.3 Data (+) and (-) Outputs (Pins H and G respectively)

Level This is the Binary Data Output signal, logically

true for pixels above threshold, logically false below threshold. To be received by a  $\mu A9637$  or equivalent device meeting EIA-RS-422 speci-

fications.

Pulse Period Variable, depending on video levels.

Pulse Width Variable, depending on video levels, minimum of

1 pixel interval.

# 4.2.2.1.4 Light Level (+) and (-) Outputs (Pins L and K respectively)

Level This is another Binary output which may be used identically as Data (+)(-) above, thus providing

two different thresholds to examine the video.

With jumper options it may be selected to latch when a pixel exceeds the threshold, and remain latched for an entire line or frame. See Section VI for a description of the jumper options available on this signal. It is to be received by a  $\,\mu$  A 9637 line receiver or equivalent device meeting EIA-RS-422 specifications.

Pulse Period

Variable, depending on video levels and jumper options.

Pulse Width

Variable, depending on video levels and jumper options.

### 4.2.2.1.5 GCLK (+) and (-) Outputs (Pins M and N respectively)

Level

This is the primary clock output and may be selected to be continuous, or gated off during retrace intervals. See Table I "S1 switch settings" for options available. The signal is to be received by a  $_{\mu}A9637$  line receiver or equivalent device meeting EIA-RS-422 specifications.

Pulse Rate

0.25 - 5 MHz

Pulse Width

Adjustable 100-300 ns by means of clock pulse width control on controller A4 P/C board. (Negative Pulse.)

#### 4.2.2.1.6 FEN (+) and (-) Outputs (Pins P and U respectively)

Level

This is the Frame Enable Signal which goes logically true at the beginning of pixel 1 of line 1 and false at the end of pixel 100 of line 100. The signal is to be received by a  $~\mu A\,9637$  line receiver or equivalent device meeting EIA-RS-422 specifications.

Pulse Rate

Frame Rate, 25-500 per second

Pulse Width

100 line intervals

#### 4.2.2.1.7 ESTART (+) and (-) Inputs (Pins S and R respectively)

Level

This is the External Start input which will initiate the camera scan on user command. It is to be driven with a  $\;\mu\text{A}\,9638$  line transmitter or equivalent device meeting EIA-RS-422 specifications.

Note: Data contained in lines 1 and 100 of each frame is invalid when the system is operated in external start mode.

Pulse Rate

Frame Rate, synchronized with FEN or (MØ  $\bullet$  EOF). See

Timing Diagram, Figure 9.

Pulse Width

Two pixel intervals minimum. See Timing Diagram,

Figure 9.

Note: Data contained in lines I and 100 of each frame is invalid when the

system is operated in external start mode.

# 4.2.2.2 Data B Connector

The Data B Connector contains signals in addition to those in the Data A Connector that are useful in synchronizing the users system, re-referencing the differential video output, and master-slaving several cameras. Up to 100 feet of Belden 8774 cable may be used, and shields should be connected to the connector shells only. See Figure 28.

### 4.2.2.2.1 LEN (+) and (-) Outputs (Pins B and C respectively)

Level

This is the Line Enable signal which indicates the beginning and end of valid video for each line. It goes logically true at the beginning of pixel 1, and false at the end of pixel 100. It is to be received by a  $\mu A\,9637$  line receiver or equivalent device meeting

EIA-RS-422 specifications.

Pulse Rate

Line Rate

Pulse Width

100 pixel periods

#### 4.2.2.2 Analog and Signal Ground (Pins E and F respectively)

The Analog Ground connects to the power supply ground in the controller. It should be connected to the users signal ground. Shields in the Data B cable should be tied to the connector shell only. Belden type 8774 cable is recommended.

#### 4.2.2.2.3 50 (+) and (-) Video Output (Pins G and H respectively)

This is the differential video output of the controller and is in parallel with the 75 ohm twinax output, therefore, only one of these outputs can be used, not both simultaneously. This output can drive up to 100 feet of Belden 8774 shielded cable and should be received by an analog line receiver

circuit like that used in the controller to receive the camera video. See Figure 10. Specifications are with 50 ohm termination and differential output.

Blank Level Adjustable +0.2 to -2 volts. Drift 0.5mv/°C.

Dark Level Adjustable +0.2 to -2 volts. Drift 0.5mv/°C.

Saturation Level Adjustable to +2 volts above dark level.

Dynamic Range ≥ 200:1

Random Noise ≤ 10 mv p-p

Coherent Noise ≤ 100 mv p-p

Data Rate 0.25 -5 MHz

Settling Time < 50 ns to 95% of saturation level.

#### 4.2.2.4 Digital Ground (Pins J and T)

This is the return for digital signals in the Data B connector.

# 4.2.2.2.5 RE-REF (+) and (-) Output (Pins K and L respectively)

Level This signal can be used to DC restore the 50 or

75 ohm analog video at the far end of a cable, thus removing any baseline drift due to cable characteristic changes from temperature and humidity. It goes logically true at the end of pixel 100 of each line, and false two pixel intervals before pixel 1 of each line. It is to be received by a  $\mu A 9637$  line receiver

or equivalent device meeting EIA-RS-422.

Pulse Rate Line Rate

Pulse Width 3-15 pixel intervals set by retrace counter. If system

is in external start mode, this signal will remain true after the end of a frame until a start command initiates

a new scan.

#### 4.2.2.2.6 HCLK (+) and (-) Output (Pins M and N respectively)

Level This is the primary continuous running clock output from the system. It is to be received by a  $\mu A 9637$

line receiver or equivalent device meeting EIA-RS-422 specifications.

Pulse Rate

0.25 -5 MHz

Pulse Width

100-300 ns adjustable

#### 4.2.2.2.7 MؕEOF (+) and (-) Outputs (Pins P and U respectively)

Level

This signal can be used to synchronize multiple cameras, and/or as a flag for the External Start Signal (4.2.2.1.7). The external logic required to use the MؕEOF signal for multiple camera synchronization is shown in Figure 29.

NOTE: Controllers with serial nos. 78083 through 78091 have the M2 signal as this output. See Section 6 for changes required on these units to change to  $M\emptyset \bullet EOF$  output.

Pulse Rate

Frame Rate

Pulse Width

2 pixel periods minimum

#### 4.2.2.3 Camera Connector

The controller camera connector is plug to plug compatible with the MC520 camera which  $\mathbf{m}$ ay be connected to it by a length of cable determined by the following formula:

Length =

$$\left[\frac{227}{\text{FMHz}}\right]$$

feet or 75 feet,

whichever is less. FMHz is the maximum data rate used. Recommended cable type is Belden 8774, and an 8-foot length, with connectors installed, is supplied with the system.

4.2.2.3.1 Video (+) and Video (-) Inputs (Pins G and H respectively)

Specifications are at output of line receiver on TP-1 of

A6 P/C board.

Saturated Light Level

2 volts p-p AC coupled, averaging around dark level.

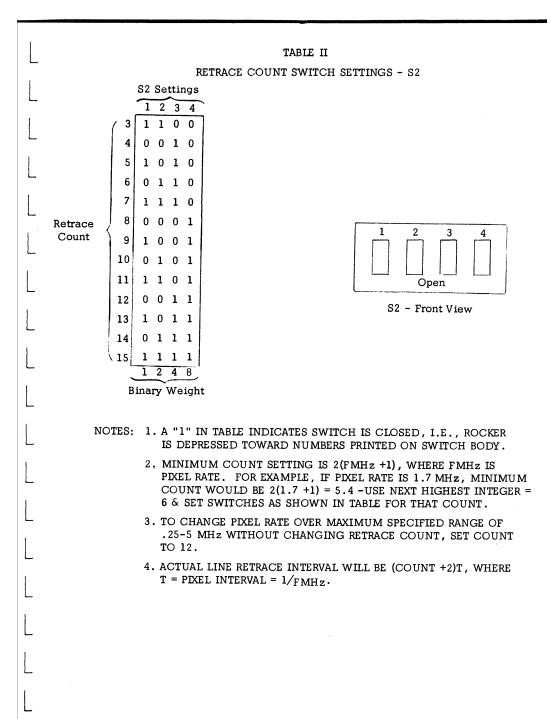

+3 volts nominal Dark Level Dynamic Range ≥ 200:1 ≤ 10 mv p-p Random Noise Coherent Noise  $\leq 200 \, \text{mv p-p}$ Scanning Rate 0.25 -5MHz  $\leq$  120 ns to 95% of saturation level Settling Time DC Restoration Provided by controller video processing. MCLK (+) and (-) Output (Pins M and N respectively) 4.2.2.3.2 Master "X" Clock from controller to camera, received Level by a  $\mu A 9637$  line receiver, with 100 ohm termination in camera. Adjustable 0.25 -5 MHz. Pulse Rate Adjustable 100 ns to 300 ns Pulse Width MIC (+) and (-) Output (Pins P and U respectively) 4.2.2.3.3 Master "Y" Clock from controller to camera, received Level by a  $\mu \, A \, 9637$  line receiver, with 100 ohm termination in camera. Pulse Rate Line Rate Adjustable 3-15 pixel intervals by retrace counter in Pulse Width controller. Minimum count is determined by: Count Min. = 2(FMHz + 1)where FMHz is maximum data rate used. For  $^5\mathrm{MHz}$ count will be 2(5+1) = 12 minimum. See Table II for Counter Switch (S2) settings.

4.2.2.3.4 CCLK (+) and (-) Input (Pins B and C respectively)

Level This is the Master Clock from the camera which is

used to synchronize the controller to eliminate cable propagation delay differences. It is received by a  $\upmu$  A9637 line receiver, and a 100 ohm termination

is provided in the controller.

Pulse Rate Adjustable 0.25 - 5 MHz. (Clock Frequency Adjust)

Pulse Width Adjustable 100-300 ns. (Clock Pulse Width Adjust)

4.2.2.3.5 EOF (+) and (-) Input (Pins K and L respectively)

Level This is the End of Frame Signal from the camera which

is used to Frame synchronize the controller. It is received by a  $\mu$ A9637 line receiver, and a 100 ohm

termination is provided in the controller.

Pulse Rate Frame Rate, 25-500 per second.

Pulse Width One line interval (True during line 100.)

4.2.2.3.6 +5 Volts and Digital Ground (Pins T and J respectively)

$\qquad \qquad \text{The controller will supply camera power plus an additional } 4.0 \text{ amperes to spare card positions A1 through A3 for user circuits.}$

4.2.2.3.7 +15 Volts (Pin E)

The controller will supply camera power plus an additional 1.0 ampere to spare card positions A1 through A3 for user circuits.

4.2.2.3.8 -15 Volts and Analog Ground (Pins R and S respectively)

The controller will supply camera power plus an additional 1.0 ampere to spare card positions A1 through A3 for user circuits.

4.3 ENVIRONMENTAL

4.3.1 Temperature

Operating Ambient 0 to +50°C

Storage  $-20 \text{ to } +100^{\circ}\text{C}$

## 4.3.2 Humidity 90% R.H. Non-Condensing 4.4 ADJUSTMENTS A4 - PC board R-Clock Frequency Adjust (R18), C-Clock Frequency Adjust (C1), Clock Pulse Width Adjust (R21), Int./Ext. Select (S1), Retrace Count (S2). Receiver R Balance (R11), Receiver C Balance (C3), A6 - PC board Receiver C Fine Balance (C12), Receiver Gain Adjust (R33), Y Sweep Amplitude Adjust (R123), X Sweep Amplitude Adjust (R120), Odd/Even Gain Balance (R52), Odd/Even Offset Balance (R50), Light Level Threshold (R137), Data Threshold (R141), Dark Level Adjust (R61), Blank Level Adjust (R9), Blank Level Balance (R62), Transmit Gain Adjust (R165), Transmit Balance (R150), Odd Pulse Width Adjust (R2), Even Pulse Width Adjust (R4). 4.5 P/C BOARDS Digital Board - A4 Analog Board - A6 A/D Option P & S Board - A5 Interconnect Board

#### SECTION V

## DETERMINATION OF OPTICAL, ILLUMINATION, AND MOUNTING REQUIREMENTS

## 5.1 OPTICAL RELATIONSHIPS

#### 5.1.1 Field of View (F)

Field of View is defined as the length of the array side imaged onto the object plane. Since the array is square, this length will be identical in both the X and Y axes. For a size measurement, the field of view will be the maximum size of the part plus an alignment tolerance.

#### 5.1.2 Magnification (M)

Magnification is the ratio of the field of view to the length of the array:

$$M = \frac{F}{AL}$$

where F is the field of view, and AL is the array length = 0.24 inch (0.60 cm) in both X and Y axes.

#### 5.1.3 Static Resolution (RS)

Static resolution is defined as the array element spacing imaged onto the object plane.

$$RS = M \times ES$$

where M is the magnification, and ES is the element spacing = 2.4 mils (60  $\mu$  m).

Static resolution is the smallest detectable change in the object dimensions, with the object stationary within the field of  ${\bf v}$ iew.

For a measurement which includes both sides of an object, the best resolution is generally considered to be  $\pm~\text{RS}_{\star}$

For a given geometrical relationship the resolution is fixed, but the accuracy depends on:

Image sharpness

Contrast Vibration or movement of the object Light level Threshold setting and other related parameters.

## 5,1.4 Dynamic Resolution (RD)

When the object to be measured is moving in the field of view, the resolution is the static resolution (SR), plus a dynamic component equal to the distance the object moves during the time it is scanned.

For a measurement which includes both sides of an object the worst case dynamic resolution will be:

$$RD = \pm \left( RS + \frac{V \times T}{2} \right)$$

where:

RS = Static resolution

V = Average velocity of measured part during T

T = Time to scan part.

The dynamic resolution will be different in the X and Y axes, since Y axis scan time is 100 times the X axis scan time. Therefore, the smallest dimension of the moving object to be measured should be scanned in the X axis of the 100 x 100 sensor to obtain greatest measurement accuracy.

#### 5.1.5 Working Distance (D)

The distance from the front of the camera lens to the object plane is defined as working distance. In general, the larger the working distance the more stable the measurement system. With greater working distances, movement of the object along the camera line-of-sight has less effect on magnification, consequently, calibration will hold for greater variations in this distance.

A longer working distance also means a narrower angular field, reduced geometrical distortion, and better lighting uniformity. Figure 11 shows working distance versus object magnification for standard "C" mount lenses.

#### 5.1.6 Depth of Field

Depth of field is defined as the distance an object may move on the Z axis and still maintain a sharp image. Figure 12 shows depth of field versus magnification versus f-stop.

When objects are expected to move in the Z axis, the camera lens should be "stopped down" to increase the depth of field and maintain focus. This reduction in lens opening requires increasing the exposure by a factor of two for every increase in f-number. This is linear so that the depth of field at f/16 is 8 times that at f/2.

## 5.1.7 Optical Determination Example

At a working distance of 20", it is required to measure the dimensions of a rectangular plate 0.96" x 2.18" with an accuracy of  $\pm$  2.5%. The plate is moving in the Y direction of scan at 10 inches/second. For best measurement accuracy the 0.96" dimension will be scanned in the X direction and the 2.18" dimension in the Y direction.

The field of view must be 2.18 " plus an alignment tolerance which we will choose as 10% = 2.18 + 0.218 = 2.4"

The magnification will then be:

$$M = \frac{F}{AL} = \frac{2.4"}{0.24"} = 10$$

The resolution in the X axis will be the static resolution since the part has no motion in that direction:

$$RS = \pm (M \times ES) = \pm (10 \times 0.0024) = \pm 0.024$$

"

The measurement accuracy will then be 0.96"  $\pm$  0.024", or 0.96"  $\pm$  2.5%.

In the Y direction the dynamic resolution will be:

RD =

$$\frac{1}{2}$$

$\left( M \times ES + \frac{V \times T}{2} \right) = \frac{1}{2} \left( 10 \times 0.0024 + \frac{10 \times T}{2} \right)$

$$= \pm (0.024" + 5T)$$

It is required that RD be  $\pm 2.5\%$  of 2.18" or  $\pm 0.0545$ "

so that:

$$+ (0.024 + 5T) \le + 0.0545$$

or

$$5T \le 0.0305$$

"

$$T \le 0.0061 \text{ sec.}$$

Where T is the time required to scan the 2.18  $\!\!^{"}$  dimension of the part.

To determine the camera scan rate we first find the number of lines required to scan the 2.18" dimension:

No. of Scan Lines =

$$\frac{2.18"}{\text{M} \times \text{ES}}$$

=  $\frac{2.18}{0.024}$  = 91

we must then scan 91 lines in 6.1 ms or less. This is equivalent to 91 lines x 100 pixels = 9100 pixels in this time, which gives a scan rate of:

Camera Scan Rate  $\approx 9100$  pixels  $\approx 1.5$  MHz,  $\approx 150$  frames/second 6.1 ms

From Figure 11, for a magnification of 10 and working distance of 20", a 50 mm focal length "C" mount lens is required with a lens extension tube of 50 mm/10 = 5 mm (0.20").

Illumination tests are then run on the 0.96" x 2.18" part at 20" working distance, and, for purposes of this example, it is assumed an f/5.6 lens opening is required.

From Figure 12, the depth of field for f/5.6 and magnification of 10 will be 2.7".

## 5.2 ILLUMINATION REQUIREMENTS

To obtain a useful signal from the MC 520 camera, a certain exposure of the sensor element is required. Since exposure is defined as the light intensity on the sensor (  $\mu \text{watt/cm}^2$ ) multiplied by the frame scan time (sec.), the required light intensity is directly proportional to the frame scan rate. Although light intensity required on the sensor is well defined, only a small percentage of the light output from a typical light source actually illuminates the sensor. Therefore, in choosing a suitable light source, factors such as f-number, magnification, lighting arrangements, and surface condition of the object, i.e. light, dark, diffuse or specular, must be considered together with sensor sensitivity and scan rate.

$$\operatorname{Rear}$  illumination is preferred where possible because less energy is required.

There are so many variables that no simple formula can be given. For many applications one of several available Reticon illumination sources will meet the users requirements. A complete analysis of the static, dynamic, and sensitivity factors is required to determine the best approach.

#### 5.2.1 Array Sensitivity Characteristics

Figure 7 shows the RA- $100 \times 100$  typical illumination characteristics, indicating the excellent sensitivity, linearity, and dynamic range obtained.

#### 5.2.2 Array Blooming Characteristics

Figure 8 shows the RA- $100 \times 100$  array blooming characteristics. These measurements were made by illuminating a spot in the center of the array covering an area of approximately  $10 \times 10$  pixels. A line approximately 15 lines outside of the illuminated area is examined to determine the worst case effect of the charge "spillover" due to the excess light above saturation level within the illuminated area. This is expressed in a percentage of the actual photosensor saturation. For example, if the  $10 \times 10$  pixel area is illuminated at 2X the photodiode saturation level, the blooming will typically be 5%, meaning that a photodiode outside the illuminated area can produce an error signal of 5% of its saturated output.

#### 5.2.3 Camera Mounting

The MC 520 camera is supplied with four 6-32 drilled and tapped holes in its case, as well as a single 1/4-20 threaded tripod mounting hole.

It is recommended that for permanent installation the four 6-32 holes be used to securely fix the camera to its mounting position. The tripod mounting is provided for temporary or movable mounting only.

Figure 2 details the MC 520 mounting hole dimensions. It is best to mount the camera so that it has some freedom of movement along the Z axis for focus and magnification settings.

If precise alignment is required between the camera field and an object whose position is fixed, the mounting arrangement should also allow for transverse movement of the camera.

## SECTION VI INSTALLATION AND ADJUSTMENT

#### 6.1 GENERAL

Before mounting the camera or using the controller, internal electronic adjustments may be required to suit the particular user's application.

$\label{thm:continuous} This section details both electronic and optical adjustments necessary to provide appropriate operating characteristics for a typical industrial environment.$

#### 6.2 MC520 CAMERA ELECTRONIC ADJUSTMENT