The S-100 and Other Micro Buses

|       | · |  |

|-------|---|--|

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

| L Ap. |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

|       |   |  |

## **Preface**

Everyone's computer seems to shrink with age. This shrinkage is usually first apparent in the memory as what was, initially, an enormous memory becomes very confining. The addition of another memory board or two temporarily solves the problem. Also, at first, the lack of hardcopy seems almost a blessing but, with every passing clock cycle, the need for a written record becomes more important. A printer interface board is added in hopes that it will do the trick. However, there are a host of expansion boards available for expansion and the present system always seems to be wanting and waiting for more and more. The key to system expansion is the bus through which the processor communicates with the present and future system components.

This book is about buses. A general discussion in Chapter 1 is used to acquaint the reader with bus basics. Then, the mechanical data, pinout designations, and bus signal definitions of the 11 most widely used bus systems are listed and explained in the following chapters so that the reader may better understand the bus of his or her system, or evaluate the bus of another system, or plan the interface of one bust a control of the system. face of one bus to another. Expansion and interface boards are described and explained so that a greater use of the bus system can be obtained. Many photographs and pinout drawings are shown so that a better understanding of microcomputers, interface boards,

and buses can be realized.

We would like to express our appreciation to the many manufacturers who participated in the preparation of this book by sharing their schematics and system descriptions. Thus, they have helped the reader to better understand and use their products. We also want to give special thanks to Debbie for her meritorious service in

preparing the manuscript.

# Contents

| CHAFTER                                                                              |       |   |    |

|--------------------------------------------------------------------------------------|-------|---|----|

| Bus Structures                                                                       | •     | • | 7  |

| CHAPTER 2                                                                            |       |   |    |

| THE S-100 Bus                                                                        | •     | • | 17 |

| CHAPTER 3                                                                            |       |   |    |

| THE BENTON HARBOR BUS                                                                | •     | ٠ | 29 |

| CHAPTER 4                                                                            |       |   |    |

| THE SBC MULTIBUS                                                                     | •     | • | 35 |

| CHAPTER 5                                                                            |       |   |    |

| THE TRS-80 Bus                                                                       |       |   | 41 |

| CHAPTER 6                                                                            |       |   |    |

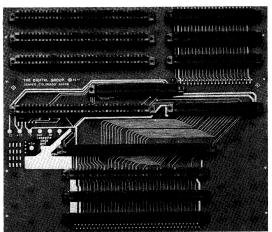

| THE DIGITAL GROUP BUS .  Memory Bus Signal Definitions—I/O Signal Definitions—Discus | ssion | • | 51 |

| THE SS-50 Bus                  |

|--------------------------------|

| CHAPTER 8                      |

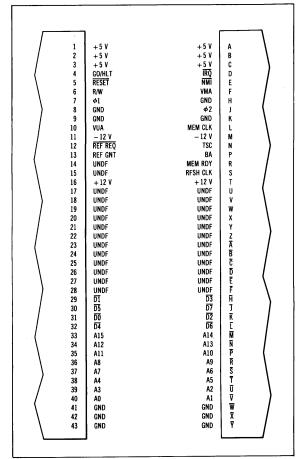

| THE EXORCISOR BUS              |

| CHAPTER 9                      |

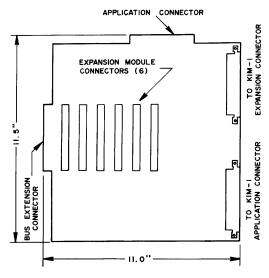

| THE KIM Bus                    |

| CHAPTER 10                     |

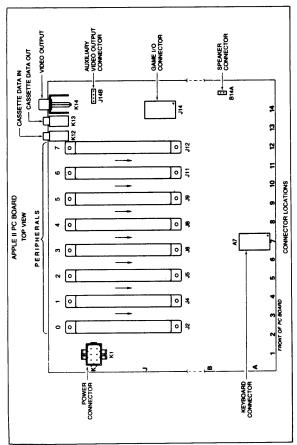

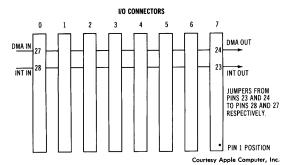

| THE APPLE II BUS               |

| CHAPTER 11                     |

| THE PET Bus                    |

| CHAPTER 12                     |

| The Ohio Scientific Bus        |

| CHAPTER 13                     |

| Benton Harbor Bus to S-100 Bus |

| CHAPTER 14                     |

| TRS-80 Bus to S-100 Bus        |

| CHAPTER 15                     |

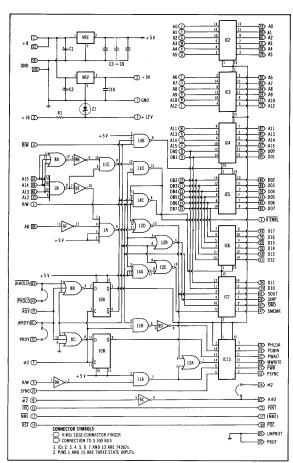

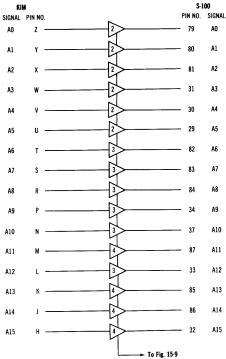

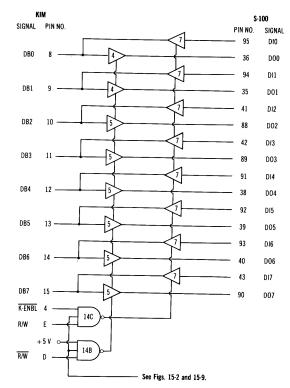

| 6502/6800 to S-100 Conversion  |

| APPENDIX                       |

| Pinout Designations            |

## **Bus Structures**

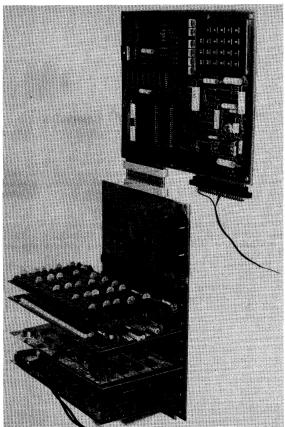

After the introduction of the Altair 8800 in early 1975, interest in microcomputers by hobbyists began to grow rapidly. In those early days, getting a system set up and running was often a formidable challenge. Yet, even then, the need for system expansion was quickly felt. Companies producing Altair-compatible memory boards soon appeared and flourished. By the end of the year, the Altair had become a leader with over 50 companies producing plug-compatible boards for the "Altair" or S-100 bus. During this period, several other successful systems, including the SWTP 6800, KIM-1 and IMSAI, were introduced. Some of these systems used the Altair bus but many did not. Since then, many systems and buses have appeared. Memory, serial and parallel I/O, video and graphics display, analog I/O, voice systems and recognition, music synthesis, and a host of other boards are available for these systems. Figs. 1-1 through 1-9 show some typical systems and plug-in boards.

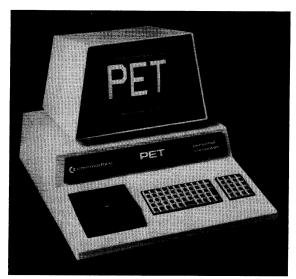

The Commodore PET shown in Fig. 1-1 is a complete micro-computer system in one unit. It has its own bus. The Bytemaster illustrated in Fig. 1-2 is also a complete micro-computer system with its own bus. The SOL-20 computer shown in Fig. 1-3 has an S-100 bus system containing several slots for expansion but it lacks a video monitor. The Heathkit H8 uses Heath's Benton Harbor Bus. It is complete as shown in Fig. 1-4 using keypad and octal displays or it is usable with other I/O devices.

Fig. 1-5 shows the Vector 1, an S-100-based system that relies entirely on external I/O devices. An S-100 Serial Communications Board is illustrated in Fig. 1-6, while a Heath H8-2 Parallel Interface Board is shown in Fig. 1-7. Notice the bus connector on the right side of the H8-2 board. Fig. 1-8 shows the Percom Floppy

Courtesy Commodore Business Machines, Inc.

Fig. 1-1. PET, a complete microcomputer system.

Courtesy The Digital Grou

Fig. 1-2. BYTEMASTER, a complete microcomputer system.

Courtesy Processor Technology Corp.

Disk and Controller for SS-50 systems, while Fig. 1-9 illustrates the Video Digitizer Board. It is using the SS-30 connector in an SS-50 system.

The bus of a system is the selection and arrangement of its signal and power lines on a connector for distribution to other boards. Bus structure becomes important when system expansion is considered, since the needed signals must be available. Careful examination of the bus of a system should be made before a system is purchased. The most popular buses will be subsequently discussed in detail.

### ADDRESS LINES

Regardless of the microprocessor used in a system or the number of lines on its bus, the address, data, and control signals must be available. The address lines are used by the processor to indicate to memory and other peripherals the location with which it wants

Courtesy Heath Co.

Fig. 1-4. Heathkit H8 digital computer mainframe.

Courtesy Vector Graphic, Inc.

Fig. 1-5. VECTOR 1 is an S-100-based system.

Courtesy DCHayes Associates

Fig. 1-6. An S-100 serial communications board.

Courtesy Heath Co.

Fig. 1-7. Heath H8-2 parallel interface board.

to communicate. The 8080, Z80, 6800 and 6502 have 16 address lines, generally labeled A0-A15, that are divided into two 8-bit bytes. Lines A0-A7 comprise the low-address byte and lines A8-A15 comprise the high-address byte. Not all address lines may be used by any one board.

Courtesy Percom Data, Inc.

Fig. 1-8. Percom floppy disk and controller for SS-50 systems.

### DATA LINES

The eight data lines, usually designated D0-D7, carry instructions and data between the processor and all the peripherals, including the memory. All processors have bidirectional data lines which carry information both into and out of the processor. The direction of information flow on these lines is usually under processor control. All buses, except the S-100 and the Digital Group, maintain the bidirectional data lines. The S-100 splits the data lines into eight data-input and eight data-output lines. The Digital Group splits them into eight memory-data in, eight memory-data out, eight I/O in and eight I/O out.

#### **CONTROL LINES**

The control lines coordinate the operations of all system components. Most buses include a master clock line, often  $\phi 2$  on the processor, that indicates to peripherals that the address placed on the bus is settled and valid. The master clock line also indicates valid data is on the data lines during a Write operation and that the processor can accept data placed on the data lines during a Read operation. The 8080 and Z80 buses may include an M1 line that

Courtesy The Micro Works

Fig. 1-9. Video digitizer board using the SS-30 connector in an SS-50 system.

signals the beginning of an op code fetch and a sync line that signals the beginning of each machine cycle.

Direction of data flow on the data lines is determined by one or more processor outputs. The 6800 and 6502 systems use a single Read/Write line to control data direction. When the line is high, a Read operation is indicated, when low, a Write operation will occur. The 8080- and Z80-based systems use separate Read and Write lines and they separate memory from other I/O with two sets of control lines. The Memory-Read and Memory-Write lines control direction of data flow during memory operations. The I/O Read and Write lines control data direction during I/O operations. Most buses include a ready line that can be used by slow memory or I/O to momentarily halt the processor until valid data can be accessed.

Most buses include Reset lines. Although a few of these are connected directly to the processor's Reset input, many are not. Some are outputs of a reset pulse generator that can be used to reset peripherals. Others are inputs to circuitry that reset the operating system, often through a nonmaskable Interrupt input, without resetting the processor.

Interrupt inputs are common to all systems. These inputs allow in-

frequent or important peripherals to get the attention of the system. A maskable Interrupt input line can be ignored by the processor on direction from the program. A nonmaskable input cannot be ignored, it must be serviced by the processor. Vectored Interrupt inputs feed an interrupt controller that assigns priority if more than one interrupt request should occur at one time. The number and type of Interrupt inputs varies widely among buses. The 8080 and Z80 buses may include status lines that indicate the condition of the maskable input or acknowledge the processor's recognition of an interrupt request.

intion of an interrupt request.

The DMA operations are facilitated on most buses by the inclusion of bus disable lines. These lines are inputs that will cause some or all of the bus lines of the processor to enter a high-impedance state, which effectively disconnects them from the bus. An external device can then control the buses for Memory-Read and -Write operations. A status line signals that the buses have been floated and the DMA can begin.

All processors require at least +5 volts dc. The 8080 also needs -5 and +12 volts dc. PROMs and communications devices may need -5, -9, or -12 volts. Most buses supply these voltages as filtered but unregulated +8 and  $\pm 16$  volts, with regulation occurring on the individual boards.

Courtesy Quay Corp.

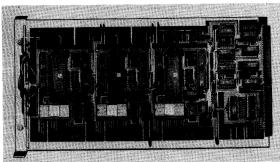

Fig. 1-10. A 12-slot expandable \$-100 motherboard.

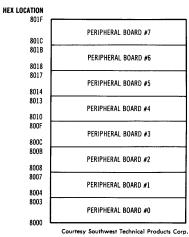

#### SYSTEM EXPANSION

Expansion of systems occurs via a motherboard as shown in Fig. 1-10. A motherboard is a printed-circuit board that distributes bus signals to several connectors which mate with system boards. Motherboards are an integral part of some systems but single-board computers may require their addition to allow for expansion. Adding a board to a system is not as simple as just purchasing it and plugging it in. A space must be available on the motherboard; indeed, a motherboard must be present. The power supply of the system must produce the necessary voltages and be able to provide the extra current required by the new board. The power requirement may become critical in a system that is presently expanded.

The microprocessor board of the system must be able to electrically drive the devices on the new board. The processor has very limited drive capabilities so most systems pass the signals of the processor through buffer chips. These devices provide little load on the processor and are capable of driving up to 100 other devices. Without buffering, the processor can be fatally damaged. However, if a system does not buffer the signals of the processor, a buffer board may have to be added. Also, the speed of the new board must be compatible with the system. Memory and peripherals may not be able to respond to the timing demands of the processor. Although most systems include the Ready input to temporarily slow the processor, this may be unacceptable.

Care should be taken when assigning addresses to the newly added boards. New boards must be placed in unused locations. The memory map of the system can be examined to determine the locations of existing boards and possible addresses for the new boards.

Finally, plug compatibility must be carefully examined. A board designed for one bus will not plug directly into another but bus interface boards are commercially available. Yet, compatibility problems exist between boards that are built for the same bus. The old rule of buying the processor and all additional boards from the same company no longer holds true. The pinout and signal definitions for both the system and the new board should be examined before the purchase is made. Specifications of the most popular buses are listed and explained in the following pages.

## The S-100 Bus

The S-100 bus was introduced by MITS Inc. on their 8080-based Altair kit. In fact, many of the bus lines are signals which are generated by the 8080 processor. It has become the most popular bus, if not the industry standard, in use by hobbyists today. Fig. 2-1 shows an S-100 microcomputer system which includes a keyboard, video monitor, and dual floppy disk. There are more than 300 boards being advertised as directly compatible with the S-100 bus. These include a multitude of memory boards, serial and parallel interface boards, floppy disk controller boards, video boards, music

Courtesy Processor Technology Corp.

Fig. 2-1. Sol System III microcomputer system.

Courtesy Quay Corp.

Fig. 2-2. A memory board (8K static RAM).

synthesizer boards, and speech recognition boards. Some examples are shown in Figs. 2-2 through 2-5.

The standard S-100 circuit board (e.g., Fig. 2-2) has overall dimensions of 5.3 inches by 10 inches. It fits into a 100-pin edge con-

Courtesy Processor Technology Corp.

Fig. 2-3. A floppy disk with control boards.

Courtesy Xitex Corp.

Fig. 2.4. Stand-alone video board. Only +7 V dc and GND on the bus are used.

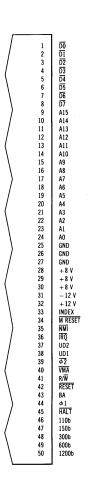

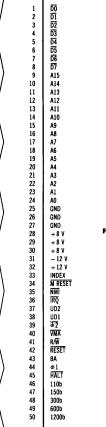

nector (50 on each side spaced 0.125 inch apart) on a motherboard (Fig. 2-6). The pins are numbered from left to right as seen in Fig. 2-2 with pins 1-50 on the component side and pins 51-100 on the opposite side. The bus supplies unregulated voltages to the boards; therefore, all boards must contain the necessary regulators. The pins are offset toward one end so that the boards cannot be inserted backwards. The S-100 pinout designations are listed in Fig. 2-7.

Courtesy Computalker Consultants

Fig. 2-5. Speech synthesizer board.

Courtesy CMC Marketing Corp.

Fig. 2-6. S-100 mainframe including chassis, 12-slot motherboard and power supply.

| 51                   | + 8 V                        | +8 V                         | 1                | 7         |

|----------------------|------------------------------|------------------------------|------------------|-----------|

| 52<br>53<br>54<br>55 | - 16 V<br>SSW DSB<br>EXT CLR | + 16 V<br>XRDY<br>VIO<br>VI1 | 2<br>3<br>4<br>5 | $\rangle$ |

| 56 57                | :                            | VI2<br>VI3                   | 6<br>7           |           |

| 58<br>59<br>60       | *                            | VI4<br>VI5<br>VI6            | 8<br>9<br>10     |           |

| 61 62 63             | •                            | VI7<br>*<br>•                | 11<br>12<br>13   |           |

| 64 65 66             | •                            | *                            | 14<br>15<br>16   |           |

| 67<br>68<br>69       | MWRITE<br>PS                 | STAT DSB<br>C/C DSB          | 17<br>18<br>19   | \         |

| 70 71                | PROT<br>RUN                  | UNPROT<br>SS<br>ADD DSB      | 20<br>21<br>22   |           |

| 72 73 74             | PRDY<br>PINT<br>PHOLD        | DO DSB<br>Φ2                 | 23<br>24         | )         |

| 75<br>76<br>77       | PRESET<br>PSYNC<br>PWR       | Φ1<br>PHLDA<br>PWAIT         | 25<br>26<br>27   |           |

| 78<br>79<br>80       | PDBIN<br>A0<br>A1            | PINTE<br>A5<br>A4            | 28<br>29<br>30   | \. \      |

| 81<br>82<br>83       | A2<br>A6<br>A7               | A3<br>A15<br>A12             | 31<br>32<br>33   |           |

| 84<br>85<br>86       | A8<br>A13<br>A14             | A9<br>D01<br>D00             | 34<br>35<br>36   |           |

| 87<br>88<br>89       | A11<br>D02<br>D03            | A10<br>D04<br>D05            | 37<br>38<br>39   | /         |

| 90<br>91<br>92       | D07<br>D14<br>D15            | D06<br>D12<br>D13            | 40<br>41<br>42   | \         |

| 93 94 95             | DI6<br>DI1<br>DI0            | DI7<br>SM1<br>SOUT           | 43<br>44<br>45   |           |

| 96<br>97<br>98       | SINTA<br>SWO                 | SINP<br>SMEMR<br>SHLTA       | 46<br>47<br>48   |           |

| 99 100               | SSTACK<br>POC<br>GND         | CLOCK<br>GND                 | 48<br>49<br>50   |           |

|                      |                              |                              |                  |           |

Fig. 2-7. S-100 pinout designations.

## S-100 SIGNAL DEFINITIONS

| Pin No. | Signal                                  | Definition                                               |

|---------|-----------------------------------------|----------------------------------------------------------|

| 1       | +8 V                                    | Unregulated input to +5 V regulators                     |

| 2       | +16 V                                   | Positive unregulated voltage supply                      |

| 3       | XRDY                                    | External Ready—ANDed with PRDY (pin 72) and con-         |

|         | (READY 1)                               | nected to READY on the 8080. If XRDY and/or PRDY         |

|         |                                         | are pulled low, the CPU will enter a Wait state until    |

|         |                                         | both are high. XRDY is often used as a front panel con-  |

|         |                                         | trol and can allow single stepping. PRDY usually is used |

|         |                                         | to signal when valid data from slow memory is on the     |

|         |                                         | bus.                                                     |

| 4       | VI0                                     | Vectored Interrupt 0-A vectored interrupt system is used |

|         |                                         | when very fast multiple interrupt response is required   |

|         |                                         | and is implemented with a special circuit card.          |

| 5       | VII                                     | Vectored Interrupt 1                                     |

| 6       | VI2                                     | Vectored Interrupt 2                                     |

| 7       | VI3                                     | Vectored Interrupt 3                                     |

| 8       | VI4                                     | Vectored Interrupt 4                                     |

| 9       | VI5                                     | Vectored Interrupt 5                                     |

| 10      | VI6                                     | Vectored Interrupt 6 Vectored Interrupt 7                |

| 11      | VI7<br>XRDY 2                           | External Ready 2                                         |

| 12*     | NMI 2                                   | Nonmaskable Interrupt                                    |

|         | +12 V                                   | Battery backup                                           |

|         | READY 3                                 | bullety buckup                                           |

| 13*     | ĪRQ                                     | Interrupt Request                                        |

| 13      | CK3                                     | Phase 3 shift clock                                      |

|         | STDBY                                   | Standby power                                            |

|         | PAUSE                                   | -                                                        |

|         | _                                       | Bank Select 8                                            |

| 14*     | RDS BL/L                                | Phase                                                    |

|         | φ1                                      | M6800 Phase 1 clock                                      |

|         | ĆK1                                     | Phase 1 shift clock                                      |

|         | STDBY                                   | Standby power                                            |

|         | _                                       | Bank Select 9                                            |

|         | OPREQ                                   |                                                          |

| 15*     | $\Phi^2$                                | M6800 Phase 2 clock                                      |

|         | BWE                                     | Write Enable ANDed with Write                            |

|         | NWI                                     | Nonmaskable Interrupt                                    |

|         | _                                       | Battery backup                                           |

|         | STOP CLK                                | Bank Select 10/Address 18                                |

| 16*     | R/W                                     | M6800 Read/Write                                         |

| 10      | LDM                                     | Load Medium Address Byte                                 |

|         |                                         | Bank Select 11/Address 16                                |

|         | INTAK                                   |                                                          |

| 17*     | BDSEL                                   | Acknowledge signal from addressed memory board           |

| ••      | NMI                                     | Nonmaskable Interrupt                                    |

|         | • • • • • • • • • • • • • • • • • • • • | •                                                        |

| Pin No.  | Signal         | Definition                                                                                                                                                                                                                                                                                                                                               |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | BGNT+          | CPU Bus Grant                                                                                                                                                                                                                                                                                                                                            |

| 18       | STAT DSB       | Bank Select 12/Address 17 Status Disable—A low on this line puts the 8 status line buffers (SMEMR, SINP, SMI, SOUT, SHLTA, SSTACK, SWO, and SINTA) into a high impedance state.                                                                                                                                                                          |

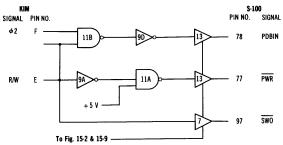

| 19       | C/C DSB        | Command/Control Disable—A low on this line puts the 6 command/control line buffers (PHLDA, PSYNC, PDBIN, PINTE, PWR, and PWAIT) into a high impedance state.                                                                                                                                                                                             |

| 20       | UNPROT         | Unprotect—A positive pulse resets the Protect flip-flop on the currently addressed board so that it can accept data. A positive pulse on PROT (pin 70) sets the flip-flop so that data cannot be written into the currently addressed memory board. Protect Status (PS, pin 69) indicates the flip-flop status; low for Protect and high for Unprotect.  |

| 21       | SS             | Single Step—Used by front panel, a high disables input buffer while panel drives bidirectional data bus.                                                                                                                                                                                                                                                 |

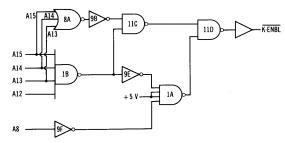

| 22       | ADD DSB        | Address Disable—A low on this line puts the 16 address line buffers into a high impedance state.                                                                                                                                                                                                                                                         |

| 23       | DO DSB         | Data Out Disable—A low on this line puts the 8 data line buffers into a high impedance state.                                                                                                                                                                                                                                                            |

| 24       | φ2             | Phase 2 clock—The master timing signal for the bus.                                                                                                                                                                                                                                                                                                      |

| 25       | $\dot{\phi}$ 1 | Phase 1 clock                                                                                                                                                                                                                                                                                                                                            |

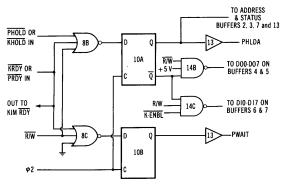

| 26       | PHLDA          | Halt Acknowledge—Processor command/control output signal which goes high in response to the HOLD signal. It indicates that the data and address buses will go to the high impedance state and the processor (8080) will enter HOLD state after completion of current machine cycle. Note: ADD DSB and DO DSB must be pulled low to float the system bus. |

| 27       | PWAIT          | Wait—Command/control signal out which, when high, acknowledges that processor is in Wait state.                                                                                                                                                                                                                                                          |

| 28       | PINTE          | Interrupt Enable—Command/control signal out which indicates condition of Interrupt Enable flip-flop. When set (high), interrupts are accepted. Flip-flop is set by Enable Interrupt (EI) instruction. It is reset by Disable Interrupt (DI) instruction, when an interrupt is accepted, and by RESET signal.                                             |

| 29       | A5             | Address Bit 5                                                                                                                                                                                                                                                                                                                                            |

| 30       | A4             | Address Bit 4                                                                                                                                                                                                                                                                                                                                            |

| 31       | A3             | Address Bit 3                                                                                                                                                                                                                                                                                                                                            |

| 32       | A15            | Address Bit 15                                                                                                                                                                                                                                                                                                                                           |

| 33       | A12            | Address Bit 12                                                                                                                                                                                                                                                                                                                                           |

| 34       | A9             | Address Bit 9                                                                                                                                                                                                                                                                                                                                            |

| 35       | DOI            | Data Out Bit 1                                                                                                                                                                                                                                                                                                                                           |

| 36<br>27 | DO0            | Data Out Bit 0                                                                                                                                                                                                                                                                                                                                           |

| 37<br>38 | A10<br>DO4     | Address Bit 10 Data Out Bit 4                                                                                                                                                                                                                                                                                                                            |

| 30       | D-04           | Data Out bit 4                                                                                                                                                                                                                                                                                                                                           |

| Pin No. | Signal            | Definition                                                                                                                                                                                          |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39      | DO5               | Data Out Bit 5                                                                                                                                                                                      |

| 40 .    | DO6               | Data Out Bit 6                                                                                                                                                                                      |

| 41      | DI2               | Data In Bit 2                                                                                                                                                                                       |

| 42      | DI3               | Data In Bit 3                                                                                                                                                                                       |

| 43      | DI7               | Data In Bit 7                                                                                                                                                                                       |

| 44      | SM1               | SM1 status output signal which, when high, indicates that the current bus cycle is an op code fetch.                                                                                                |

| 45      | SOUT              | Status output signal which, when high, indicates that the address bus contains the address of an output device and the data bus will contain the output data when PWR is active.                    |

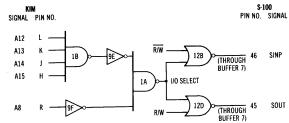

| 46      | SINP              | In—Status output signal which, when high, indicates that<br>the address bus contains the address of an input device<br>and the input data should be placed on the data bus<br>when PDBIN is active. |

| 47      | SMEMR             | Memory Read—Status output signal which, when high, indicates that the data bus will be used to read memory data.                                                                                    |

| 48      | SHLTA             | Halt Acknowledge—Status output signal which, when high, acknowledges that a HALT instruction has been executed.                                                                                     |

| 49      | CLOCK             | Phase 2 clock inverted                                                                                                                                                                              |

| 50      | GND               | Signal and power ground                                                                                                                                                                             |

| 51      | +8 V              | Same as pin 1                                                                                                                                                                                       |

| 52      | <u>_16 V</u>      | Negative unregulated voltage supply                                                                                                                                                                 |

| 53      | SSW DSB           | Sense Switch Disable—A low disables the data input buffers so the input from the sense switches may be strobed onto the bidirectional data bus.                                                     |

| 54      | EXT CLR           | External Clear—A low clears I/O devices. Generated by front panel switch.                                                                                                                           |

| 55*     | RTC               | Real Time Clock                                                                                                                                                                                     |

|         | GND               | Ground                                                                                                                                                                                              |

| 56*     | STSTB             | Status Strobe—A low indicates that status signals are on data bus.                                                                                                                                  |

|         | DMAGR7            | DMA Grant 7                                                                                                                                                                                         |

|         | $v_{cc}$          | Standby                                                                                                                                                                                             |

| 57*     | DIG1              | Data Input Gate 1                                                                                                                                                                                   |

|         | DMAGR6            | DMA Grant 6                                                                                                                                                                                         |

| 58*     | FRDY              | Front Panel Ready—When low, it disables WRITE driver.                                                                                                                                               |

|         | DMAGR5            | DMA Grant 5                                                                                                                                                                                         |

| 59*     | DMAGR4            | DMA Grant 4                                                                                                                                                                                         |

|         | cw                | Conditioned Memory Write                                                                                                                                                                            |

|         | _                 | Memory Disable (PGANTOM)                                                                                                                                                                            |

|         | EXINH0            | Bank Select 0                                                                                                                                                                                       |

|         | INH               | Shadow Memory                                                                                                                                                                                       |

|         | Program<br>Switch | To enable programmer                                                                                                                                                                                |

| 60*     | DMAGR3            | DMA Grant 3                                                                                                                                                                                         |

|         | ABX               | NOT Alternate Bank X (A 16)                                                                                                                                                                         |

| Pin No.  | Signal       | Definition                                                                  |

|----------|--------------|-----------------------------------------------------------------------------|

|          | MBS          | Memory Bank Select                                                          |

|          | _            | Bank Select 1                                                               |

|          | MONITOR      | Enable user's monitor                                                       |

| 61*      | A17          | Address line 17                                                             |

|          | DMAGR2       | DMA Grant 2                                                                 |

|          | KRDY         | KIMSI Ready                                                                 |

|          |              | Bank Select 2                                                               |

|          | GND          | Ground                                                                      |

| 62*      | DMAGR1       | DMA Grant 1                                                                 |

|          | CK4          | Phase 4 shift clock                                                         |

|          | Кф2          | KIMSI φ2 clock                                                              |

|          |              | Bank Select 3                                                               |

|          | A18          | Address line 18                                                             |

| 63*      | DMAGR0       | DMA Grant 0                                                                 |

|          | CK2          | Phase 2 shift clock                                                         |

|          | KHOLD        | KIMSI Hold                                                                  |

|          | _            | Bank Select 4                                                               |

|          | A19          | Address Line 19                                                             |

| 64*      | DMA RCVD     | DMA Grant Flag                                                              |

|          | BCE          | Chip Enable                                                                 |

|          | RTC          | Real Time Clock (60 Hz)                                                     |

|          | _            | Bank Select                                                                 |

|          | RDSBL/H      |                                                                             |

| 65*      | MREQ         | Memory Request                                                              |

|          | WRITE        | Write Enable                                                                |

|          |              | Bank Select 6                                                               |

| 66*      | RFSH         | Refrest                                                                     |

|          | LDH          | Load High Address Byte                                                      |

|          | CMCLK        | Variable video clock                                                        |

|          | <del>-</del> | Bank Select 7                                                               |

|          | 8/16         |                                                                             |

| 67*      | PHANTOM      | Phantom Disable—Used to disable RAM and I/O ad-                             |

|          |              | dressing                                                                    |

|          | NMI          | Nonmaskable Interrupt                                                       |

|          | RESHDSBL     | Refrest Disable                                                             |

|          | MDSBL        | Memory Disable                                                              |

|          | BBSY +       | Phantom                                                                     |

|          | RFSH         | Refrest                                                                     |

|          | SCLK         | Clock (Video Sample)<br>Address Line 19                                     |

|          | A19          | Memory Write—A high indicates that the current data                         |

| 68       | MWRITE       | on the Data Out Bus is to be written into the memory                        |

|          |              | location currently on the address bus.                                      |

| 40       | PS           | Protect Status—See pin 20.                                                  |

| 69       | PROT         |                                                                             |

| 70<br>71 |              | Protect—See pin 20. Run—A high indicates that the Run/Stop flip-flop is set |

| 71       | RUN          | to RUN on the front panel.                                                  |

| 72       | PRDY         | Ready—See pin 3.                                                            |

| 72<br>73 | PINT         | Interrupt Request—A low causes the processor to recog-                      |

| /3       | FIINI        | menopi redoesi-v ion conses me processor to recog-                          |

| Pin No. | Signal     | Definition                                                                                                                                                                                        |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |            | nize an interrupt request at the end of the current instruction or while halted. If the CPU is in the Hold state or if the Interrupt Enable flip-flop is reset, it will not honor the request.    |

| 74      | PHOLD      | Hold—A low requests the processor to enter the Hold<br>state. It allows an external device to gain control of the<br>address and data buses as soon as the current machine<br>cycle is completed. |

| 75      | PRESET     | Reset—A low causes the contents of the program counter to be cleared and the instruction register is set to 0.                                                                                    |

| 76      | PSYNC      | Sync—The command/control signal out which, when high, identifies the beginning of a machine cycle.                                                                                                |

| 77      | PWR        | Write—The command/control signal out which, when low, signifies the presence of valid data on the Data Out bus for memory write or I/O output.                                                    |

| 78      | PDBIN      | Data Bus In—The command/control signal out which, when high, requests data on the DI bus from the currently addressed memory or I/O.                                                              |

| 79      | A0         | Address Bit 0                                                                                                                                                                                     |

| 80      | Al         | Address Bit 1                                                                                                                                                                                     |

| 81      | A2         | Address Bit 2                                                                                                                                                                                     |

| 82      | A6         | Address Bit 6                                                                                                                                                                                     |

| 83      | A7         | Address Bit 7                                                                                                                                                                                     |

| 84      | A8         | Address Bit 8                                                                                                                                                                                     |

| 85      | A13        | Address Bit 13                                                                                                                                                                                    |

| 86      | A14        | Address Bit 14                                                                                                                                                                                    |

| 87      | A11        | Address Bit 11                                                                                                                                                                                    |

| 88      | DO2        | Data Out Bit 2                                                                                                                                                                                    |

| 89      | DO3        | Data Out Bit 3                                                                                                                                                                                    |

| 90      | DO7        | Data Out Bit 7                                                                                                                                                                                    |

| 91      | DI4        | Data In Bit 4                                                                                                                                                                                     |

| 92      | DI5        | Data In Bit 5                                                                                                                                                                                     |

| 93      | DI6        | Data In Bit 6                                                                                                                                                                                     |

| 94      | DII        | Data In Bit 1                                                                                                                                                                                     |

| 95      | DIO        | Data In Bit 0                                                                                                                                                                                     |

| 96      | SINTA      | Interrupt Acknowledge—The status output signal which, when high, identifies the instruction fetch cycle(s) that immediately follow an accepted interrupt request presented on PINT.               |

| 97      | <u>swo</u> | Write/Output—The status output signal identifying a bus cycle which, when low, transfers data from processor to memory or I/O port.                                                               |

| 98      | SSTACK     | Stack—Status output signal which indicates, when high, that the address bus holds the pushdown stack address from the Stack Pointer and that a stack operation will occur on the current cycle.   |

| 99      | POC        | Power On Clear—Generated by PRESET or power on. Used to reset CPU and I/O devices.                                                                                                                |

| 100     | GND        | Signal and power ground.                                                                                                                                                                          |

#### DISCUSSION

As can be seen from the signal definitions, the S-100 bus is standardized except for those pins marked with an asterisk, pins 12–17 and 55–67. In the signal definitions column, some of the known uses for these lines have been listed; although, some new ones have probably been omitted. Some systems that are not 8080-based systems do not generate all of the signals listed. If a board requires one or more of these missing signals, then a real problem exists which may require extensive modifications.

which may require extensive modifications.

To effectively use the S-100 bus, care must be taken in reading the specifications of all boards used or contemplated being used. All boards must have the proper lines on the proper pin or capability for jumpering to the proper pin. All signals required by any of these boards must be generated somewhere in the system. Information on systems and boards may be obtained from manufacturers, computer stores, computer clubs, and other hobbyists.

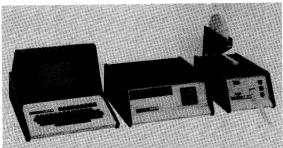

## The Benton Harbor Bus

The Benton-Harbor Bus was developed by Heath Company for use on their 8080-based H8 System (shown in Fig. 3-1). Heath Company now offers the H8 System which includes the H8 (chassis, power supply, motherboard, control board, and CPU board), the H8-1 (8K × 8 memory board with 4K of memory), the H8-2 (parallel interface board), the H8-3 (4K × 8 memory for the H8-1), and the H8-5 (serial I/O and cassette interface). Heath Company also offers the H10 papertape reader/punch and the H9 video terminal (both shown in Fig. 3-1), and the H8 floppy disk (shown in Fig. 3-2). Heath Company plans to offer other boards and accessories.

Courtesy Heath Co.

Fig. 3-1. The H8 system with H9 video terminal and H10 papertape reader/punch.

Courtesy Heath Co.

Fig. 3-2. The WH17 floppy disk system.

Other companies will surely offer boards for the popular Heath

other companies will surely other boards for the Francisco system.

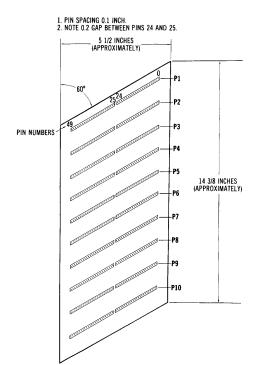

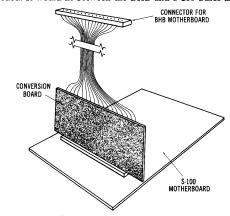

The approximately 5½-inch × 14¾-inch motherboard (Fig. 3-3) is mounted vertically and has slots (P1-P10) for ten other boards to be inserted at an unusual angle. Slot P1 is reserved for the H8 control board, P2 is reserved for the H8 CPU board and slot P10 is reserved for an expansion connector. That leaves seven slots for expansion within the H8 mainframe.

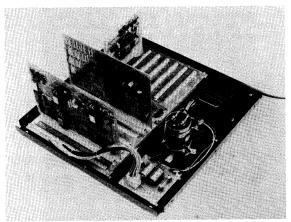

A board for the Benton Harbor Bus is approximately 6 inches × 12 inches with two 25-pin connectors on one end. The connectors slide onto the pins on the motherboard. See Figs. 3-4 and 3-5 for typical boards. A bracket on the opposite end from the connectors

typical boards. A bracket on the opposite end from the connectors supports the boards when they are inserted into the H8 chassis.

### BENTON HARBOR BUS SIGNAL DEFINITIONS

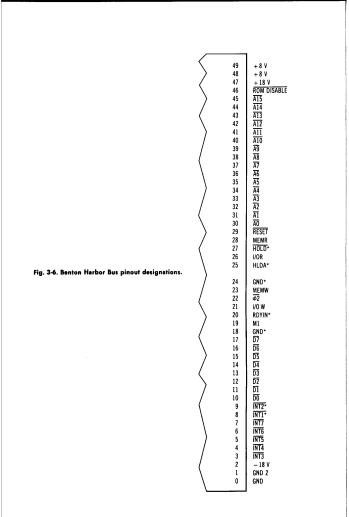

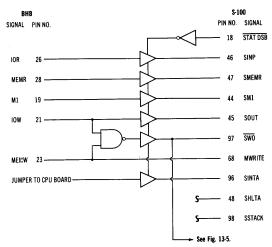

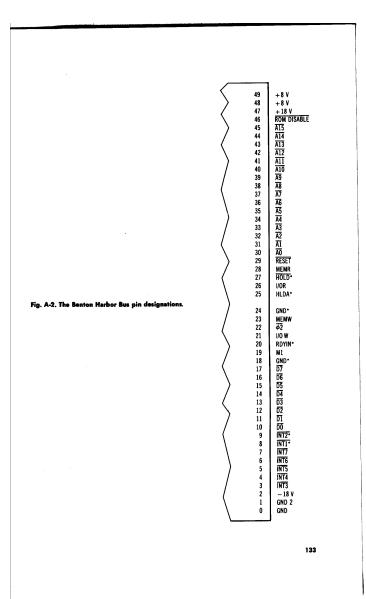

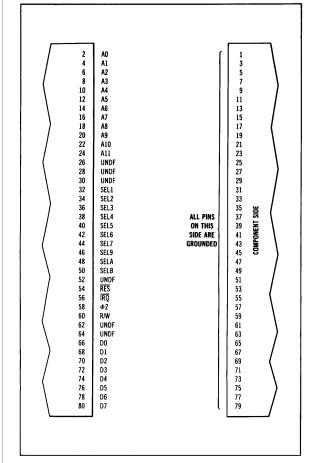

The Benton Harbor Bus pinout designations are shown in Fig. 3-6.

| Pin No. | Signal        | Definitions                                                                                                                                                                                               |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

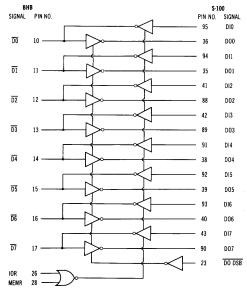

| 10–17   | <u>DO-</u> D7 | Data Bus—The tri-state data bus provides bidirec-<br>tional communication between the CPU, memory, and<br>I/O devices for instructions and data transfers. DO<br>is least significant bit. Negative true. |

| 23      | MEMW          | Memory Write—A high strobes data on the data bus                                                                                                                                                          |

Fig. 3-3. Diagram of the Benton Harbor Bus motherboard used in the H8.

| Pin No. | Signal | Definitions                                                                                                                              |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | to the currently addressed memory or memory-<br>mapped I/O devices.                                                                      |

| 21      | I/OW   | I/O Write—A high strobes data on the data bus to<br>the output device currently addressed by the lower<br>eight bits of the address bus. |

| 28      | MEMR   | Memory Read—A high strobes data from the ad-<br>dressed memory or memory-mapped I/O device onto<br>the data bus and into the CPU.        |

| 26      | I/OR   | I/O Read—A high strobes data from the addressed                                                                                          |

Courtesy Heath Co

Fig. 3-4. H8-5 serial I/O and cassette interface board.

Courtesy Heath Co.

Fig. 3-5. H8 CPU board.

| Pin No. | Signal | Definitions                                                                                             |

|---------|--------|---------------------------------------------------------------------------------------------------------|

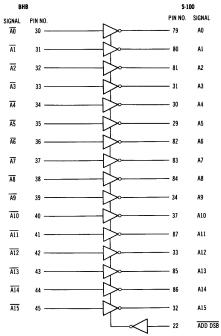

| 30-45   | A0-A15 | I/O device onto the data bus and into the CPU.  Address Bus—Sixteen fully buffered lines that can       |

| 30-43   | A0-A13 | select any one of 65,536 memory locations or 256 I/O ports. Negative true. A0 is least significant bit. |

| 19      | M1     | Machine Cycle One—A high signifies that the ma-<br>chine cycle being executed is an instruction fetch.  |

| 20      | RDYIN* | Ready In—A low causes the processor to enter a                                                          |

<sup>\*</sup> Heath Company reserves the right to change these pin designations.

| Pin No. | Signal                       | Definition                                                                                                                                                                                                                                                                                                            |

|---------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                              | WAIT state until pulled high again. Used by slow memory.                                                                                                                                                                                                                                                              |

| 27      | HOLD*                        | Hold—A low causes the CPU to enter a HOLD state at the end of the current machine cycle. The address and data buses will be tri-stated allowing a DMA device to control these buses.                                                                                                                                  |

| 25      | HLDA*                        | Hold Acknowledge—A high appears in response to the HOLD signal and indicates that the data and address buses will be tri-stated.                                                                                                                                                                                      |

| 46      | ROM DISABLE                  | When the X1, X2 jumper on the H8 CPU board is installed, a low on this signal disables the on-board ROM allowing a test board or other ROM board to use the monitor address space.                                                                                                                                    |

| 37      |                              | Interrupts—A low on any combination of these lines activates the Interrupt Request of the CPU.                                                                                                                                                                                                                        |

| 8, 9    | <u>ัท</u> รี₁, <b>เ</b> ทรี₂ | Not Dedicated—The H8 CPU board has jumper pads available to jumper INT <sub>1</sub> and INT <sub>2</sub> to these bus lines in order to share the front panel interrupts, if desired. Otherwise, these lines may be used by the customer. With jumper installed, a low will activate an Interrupt Request of the CPU. |

| 29      | RESET                        | Reset—Goes low in response to a manual reset or<br>CPU power on. Used to put devices on bus in a<br>known state for an orderly start up.                                                                                                                                                                              |

| 22      | $\overline{\phi^2}$          | Phase Two Clock—This buffered inverted signal is used to synchronize system devices connected to the bus.                                                                                                                                                                                                             |

| 0, 1    | GND                          | Ground—Signal and power ground for bus.                                                                                                                                                                                                                                                                               |

| 18, 24  | CPU GND                      | CPU Ground—These lines are grounded on the H8<br>CPU board but can be floated for other use by re-<br>moving one jumper.                                                                                                                                                                                              |

| 2       | −18 V                        | —18 V—Unregulated negative supply voltage.                                                                                                                                                                                                                                                                            |

| 47      | +18 V                        | +18 V—Unregulated positive supply voltage                                                                                                                                                                                                                                                                             |

| 48, 49  | +8 V                         | +8 V—Unregulated positive supply voltage                                                                                                                                                                                                                                                                              |

## DISCUSSION

Heath Company in designing the Benton Harbor Bus has stuck to the basics. Only the address bus, data bus, and generalized control lines are included. Specialized control lines are omitted so that the bus does not need to change with future alterations. A convenient design consideration on the bus is the positioning of the data bus, address bus, and interrupt lines so that the last digit of their respective number coincides with the last digit of the bus line (e.g.  $\overline{A6}$  is on line 36).

<sup>\*</sup> Heath Company reserves the right to change these pin designations.

## The SBC Multibus

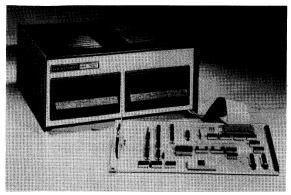

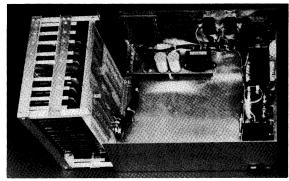

The Multibus was developed by Intel for their SBC series of boards that includes CPUs, memory, I/O, communications, high-speed math, DMA control, and others. Fig. 4-1 shows an SBC system with chassis, power supply, backplane with card cage, and CPU board. Figs. 4-2 and 4-3 show an SBC 80/20 CPU board and a combination memory and I/O expansion board, respectively. Several companies produce a wide variety of boards which will operate on the Multibus.

The SBC series is a general-purpose, inexpensive board set originally designed for OEMs so that they would not have to develop their own hardware for every new product in which they used an

Courtesy Intel Corp.

Fig. 4-1. The SBC-based 80/20 system.

Courtesy Intel Corp.

Fig. 4-2. SBC 80/20 single-board computer.

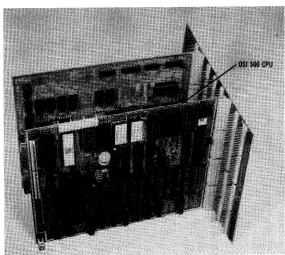

Intel processor. The SBC system allows implementation of a tremendous variety of inputs and outputs with a small number of boards. Multimaster operation having multiplexed CPUs, DMA controllers, and disk controllers controlling the bus is easily realized. A typical board for the Multibus is shown in Fig. 4-3. It is 12 inches long, 6.75 inches high and 0.062 inch thick with two edge connectors along the bottom as shown. (The P1 Multibus is on the left in the photo and the P2 Auxiliary Connector is on the right.) Depending on the board type, there may be up to three edge con-

Fig. 4-3. SBC 517 combination I/O expansion board.

| 1 | 6 8 8 100 112 14 116 18 200 222 244 266 268 300 32 32 344 366 388 38 400 42 42 44 44 46 48 500 522 54 56 66 66 66 66 66 66 66 66 66 66 66 66 | + 5 V + 12 V - 5 V COND INIT BPRO BREO MWTC IOWC INHI INHE UNDF UNDF UNDF UNDF INTS INTS INTS INTS INTS INTS INTS INTS | + 12 V - 5 V GND BGLK BPRN BUSY MRDC IORC VACK AACK AACK UNDF CGLK INT6 INT4 INT2 INT0 ADRE ADRA ADRA ADRA ADRA ADRA ADRA ADRA | 7 9 111 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 55 55 56 67 69 61 63 75 77 77 79 81 83 83 | COMPONENT SIDE |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------|--|

|---|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------|--|

Fig. 4-4. SBC pinout designations.

nectors along the top of the board. The 86-pin P1 (Multibus) edge-connector numbers its pins from left to right as the board is viewed in Fig. 4-3. The odd pin numbers are on the component side and the even pin numbers are on the opposite side. The pinout designations are listed in Fig. 4-4.

### SBC SIGNAL DEFINITIONS

|        |           | SEE SIGNAL PERMANNIONS                                    |

|--------|-----------|-----------------------------------------------------------|

| Pin No | . Signal  | Definitions                                               |

| 67-74  | DATO-DATZ | Data Bus—Active low, bidirectional.                       |

| 5966   | DATS-DATE | Data Bus—For upper 8 bits in 16-bit systems.              |

| 19     | MRDC      |                                                           |

| • •    | made      | Memory Read Command—A low indicates that a certain        |

|        |           | memory location is on the address bus and its contents    |

| 20     | MWTC      | are to be put on data bus.                                |

| 20     | WAIC      | Memory Write Command—A low indicates that a certain       |

|        |           | memory location has been addressed and data to be         |

|        |           | written into it is on the data bus.                       |

| 21     | IORC      | I/O Read Command—A low indicates that an input port       |

|        |           | has been addressed and the data at that port is to be     |

|        |           | placed on the data bus.                                   |

| 22     | IOWC      | I/O Write Command—A low indicates that an output          |

|        |           | port has been addressed and that the data bus contents    |

|        |           | are to be outputted.                                      |

| 43-58  | ADRO-ADRE | Address Bus—Active low address lines.                     |

| 14     | INIT      | Initialize—A low resets the entire system.                |

| 15     | BPRN      | Bus Priority In—A low indicates that no higher priority   |

|        |           | master module is requesting use of the system bus. It is  |

|        |           | connected to signal ground in a single master system;     |

|        |           | synchronized with BCLK in a multimaster system. It is     |

|        |           | not bused on the motherboard.                             |

| 16     | BPRO      |                                                           |

| 10     | DFRO      | Bus Priority Out—Connected to BPRN of master module       |

|        |           | with next lower bus priority. A low indicates to the next |

|        |           | lower master module that a higher priority master is in   |

|        |           | control of the buses. It is not bused on motherboard.     |

| 17     | BUSY      | Bus Busy—A low indicates that the bus is currently in     |

|        |           | use and prevents other master modules from gaining        |

|        |           | control.                                                  |

| 18     | BREQ      | Bus Request—A low indicates that a particular master      |

|        |           | module requires use of the bus. It is synchronized with   |

|        |           | BCLK.                                                     |

| 23     | XACK      | Transfer Acknowledge—A low from a memory location         |

|        |           | or I/O port indicates that the specified read/write op-   |

|        |           | eration is complete.                                      |

| 25     | AACK      | Advanced Acknowledge—A low allows memory to com-          |

|        |           | plete access without having the CPU wait.                 |

| 33     | INTR      | Direct Interrupt—A low from an external device gen-       |

| 55     | HAIR      | erates an interrupt request.                              |

|        |           | cruies un mierropi requesi.                               |

# The TRS-80 Bus

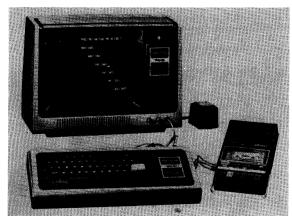

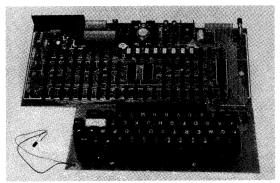

The TRS-80, shown in Fig. 5-1, is Radio Shack's very popular microcomputer system. The keyboard enclosure, shown removed in Fig. 5-2, houses the CPU, RAM, executive and BASIC ROMs, the keyboard, video and cassette interfaces, and the power supply. Floppy disk units and printers (not shown) are available to expand the system.

Courtesy R

Fig. 5-1. The TRS-80 microcomputer system.

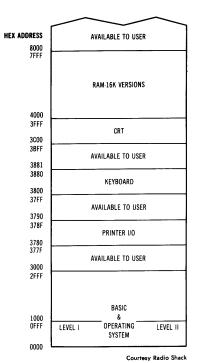

Fig. 5-4. Memory map for the TRS-80.

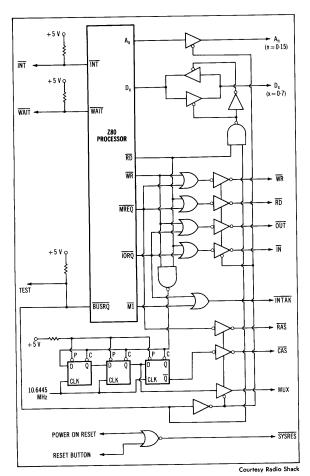

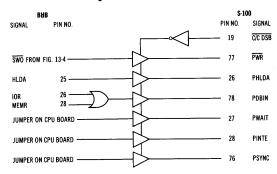

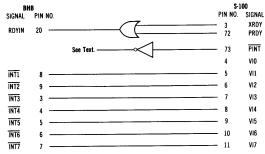

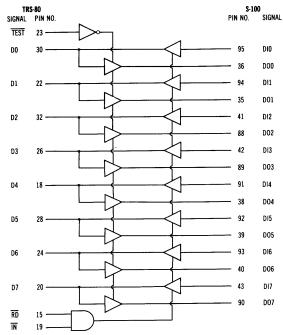

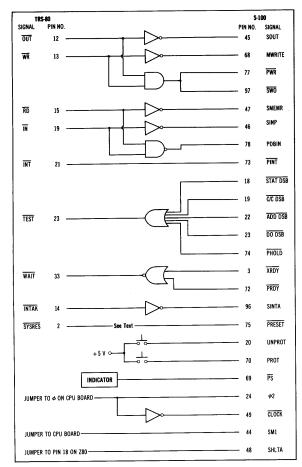

Because its bus is relatively straightforward, the TRS-80 is easy to expand. TRS-80 to S-100 interface boards are commercially available. The TRS-80 bus pinout designations are shown in Fig. 5-5.

### TRS-80 SIGNAL DEFINITIONS

| Pin No. Si   | gnal | Definition                                       |

|--------------|------|--------------------------------------------------|

| 18, 20, D0-D | 7    | Data Bus—The bidirectional data bus carries data |

| 22, 24,      |      | between the processor and peripherals.           |

| 26, 28,      |      |                                                  |

| 30, 32       |      |                                                  |

Courtesy Radio Shack

Fig. 5-2. The keyboard unit of the TRS-80 system.

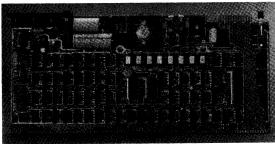

Expansion of the Z80-based system is accomplished via the 40-pin (0.1-inch spacing) edge connector shown in the upper right-hand corner of Fig. 5-3. No positive indexing is provided. All lines, except as noted, are buffered. Use of dynamic RAM is simplified by address multiplex signals that are brought to the connector. The memory space above Hex 8000 is available for expansion. This is shown in the memory map given in Fig. 5-4.

Courtesy Radio Shack

Fig. 5-3. The TRS-80 board. The expansion connector is shown in the upper right-hand edge of the board.

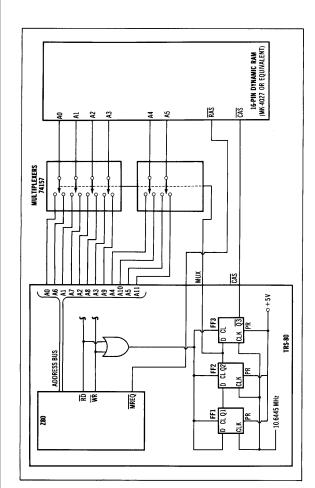

Fig. 5-6. Diagram showing a Z80-to-bus interface.

| Γ   |                | 2  | SYSRES | RAS        | 1  | $\neg$ |

|-----|----------------|----|--------|------------|----|--------|

| -   |                | 4  | A10    | CAS        | 3  | - 1    |

| 1   |                | 6  | A13    | A12        | 5  | )      |

| 1   |                | 8  | GND    | A15        | 7  | - /    |

| \   |                | 10 | A14    | A11        | 9  | - /    |

| \   |                | 12 | OUT    | A8         | 11 | (      |

| \   | Ä              | 14 | INTAK  | WR         | 13 | - 1    |

| )   | COMPONENT SIDE | 16 | MUX    | RD         | 15 | - 1    |

| /   | ×              | 18 | D4     | A9         | 17 | \      |

| 1   | 8              | 20 | D7     | ĪN         | 19 | - /    |

| (   | ₹              | 22 | D1     | ĪNT        | 21 | - 1    |

| \   | 8              | 24 | D6     | TEST       | 23 | - 1    |

| \   |                | 26 | D3     | A0         | 25 | (      |

| - \ |                | 28 | D5     | A1         | 27 | 1      |

| - 1 |                | 30 | D0     | GND        | 29 | 1      |

| - / |                | 32 | D2     | A4         | 31 | 1      |

| 1   |                | 34 | A3     | WAIT       | 33 | - 1    |

| 1   |                | 36 | A7     | A5         | 35 | - 1    |

| \   |                | 38 | A6     | GND        | 37 | - /    |

| \   |                | 40 | A2     | + 5 or GND | 39 | - 1    |

| \_  |                |    | J      |            |    |        |

Fig. 5-5. Pinout designations for the TRS-80 bus.

Signal

Definition

12, 13, RD, WR, IN, OUT Read, Write, Input, Output—The bus Read, Write, 15, 19 Input and Output lines control the memory and Input and Output lines control the memory and I/O operations. They are derived from the Read, Write, Memory Request and I/O Request outputs of the Z80 as shown in Fig. 5-6. The processor's Read and Write lines are active low outputs used to determine the direction of flow on the data bus. The MREQ line is an active low output used to indicate a Memory-Read or -Write operation and the  $\overline{\text{IORQ}}$  line is an active low output used to indithe IORQ line is an active low output used to indicate an input or output operation. The bus RD line is the ORed combination of the processor's Read and MREQ lines and goes low to indicate a Memory-Read operation. The bus WR line is the ORed combination of the processor's Write and MREQ lines and goes low to indicate a Memory Read. The lines and goes low to indicate a Memory Read. The line is on active low output that indicates bus  $\overline{|N|}$  line is an active low output that indicates an input operation, derived by  $\overline{QRing}$  the  $\overline{RD}$  and  $\overline{IORQ}$  of the processor. The bus  $\overline{QUT}$  line is an active low output that indicates an output operation, derived by ORing the processor's WR and IORQ.

Row Address Select, Column Address Select, Address Multiplex—These lines are used in addressing industry standard 16-pin 4-kilobyte dynamic RAMs. Since only six address pins, A0–A5, are available

1, 3, RAS, CAS, MUX 16

Fig. 5-7, A typical interface circuit for addressing the dynamic RAM.

on the RAM integrated circuit, the address must be fed to it in parts—multiplexed.