# Contents

| Introduction                                                    | 1  |

|-----------------------------------------------------------------|----|

| The adventure and excitement of personal computing, 1           |    |

| It's easy to build a home computer system, 3                    |    |

| What do people do with home computers, 3                        |    |

| What this book is about, 4                                      |    |

| 1. Computer Codes, Bits, Bytes, and Arithmetic                  | 6  |

| Binary numbers, 6                                               |    |

| Octal and hex numbers, 8                                        |    |

| Binary arithmetic, 10                                           |    |

| BCD numbers, 11                                                 |    |

| 2. Digital Logic                                                | 13 |

|                                                                 |    |

| Logic states, 13                                                |    |

| Digital logic gates, 14                                         |    |

| The parity-bit and error-checking, 21                           |    |

| Arithmetic circuits, 22                                         |    |

| DeMorgan's Theorems, 23 Building inverters from other gates, 24 |    |

| Encoder and decoder circuits, 24                                |    |

| TTL, CMOS, and MOS, 26                                          |    |

| Tri-state and open-collector ICs, 28                            |    |

| Tri-state and open concessor res, 20                            |    |

| 3. More about Digital Logic                                     | 30 |

| The basic flip-flop (R-S), 30                                   |    |

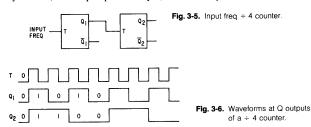

| The T flip-flop and the counter, 31                             |    |

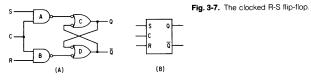

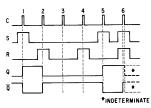

| The clocked R-S flip-flop, 33                                   |    |

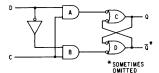

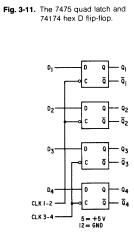

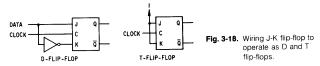

| The D flip-flop, 33                                             |    |

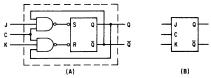

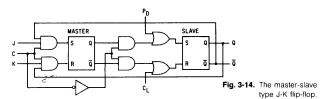

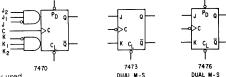

| The J-K flip-flop, 35                                           |    |

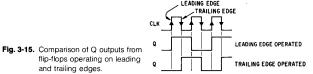

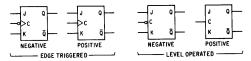

| Edge-triggered flip-flops, 36                                   |    |

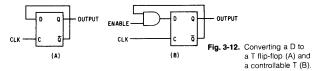

| Using J-K flip-flops as D and T flip-flops, 37                  |    |

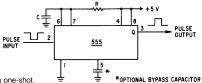

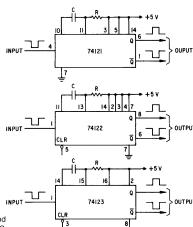

| One-shots, 37                                                   |    |

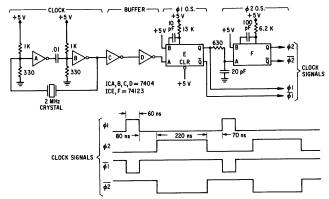

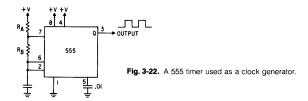

| Clock circuits, 39                                              |    |

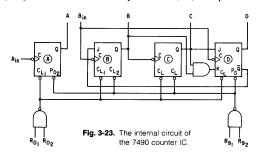

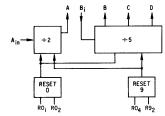

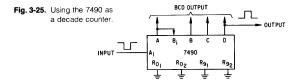

| Counters, 40                                                    |    |

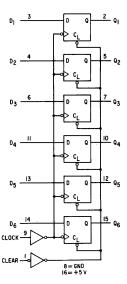

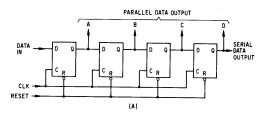

| Shift registers, 41                                             |    |

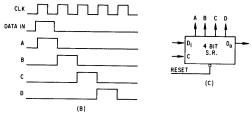

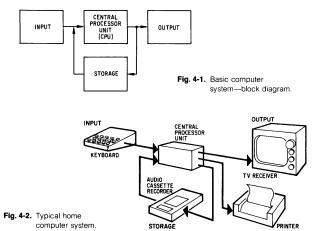

| 4. An Introduction to Computer Systems                          | 44 |

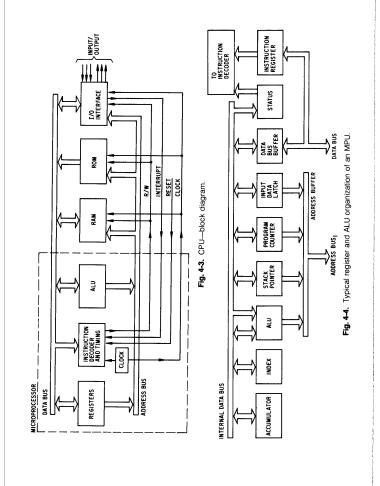

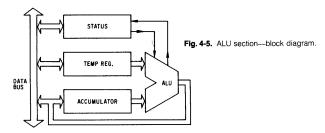

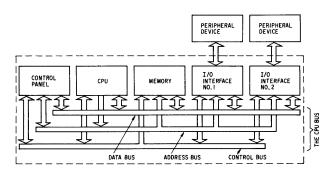

| The CPU—The system control center, 44                           |    |

| Hardware vs. software, 50                                       |    |

| The CPU instruction set, 50                                     |    |

| Computer programming, 50                                        |    |

| Microcomputers vs. large computers, 51                          |    |

|                                                                 |    |

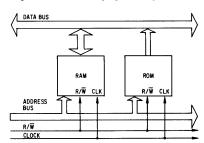

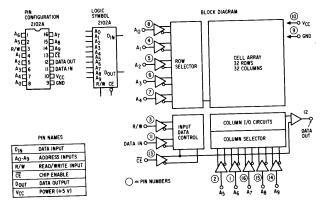

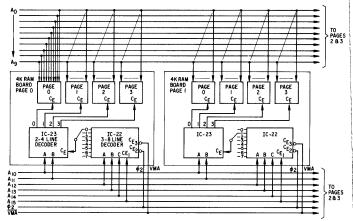

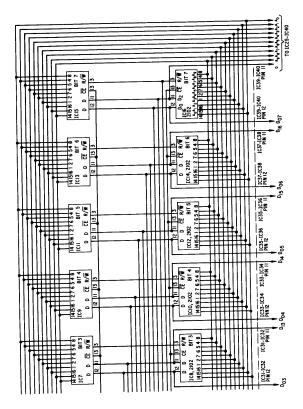

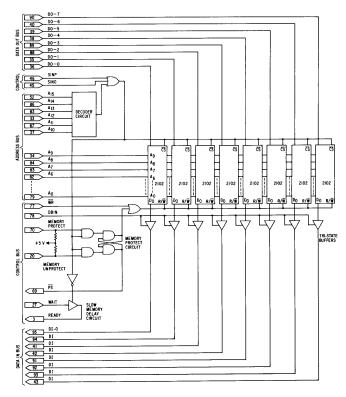

| Memory basics, 53                                       |     |

|---------------------------------------------------------|-----|

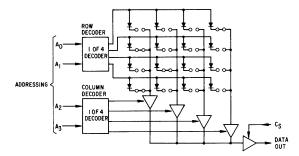

| Memory addressing, 54                                   |     |

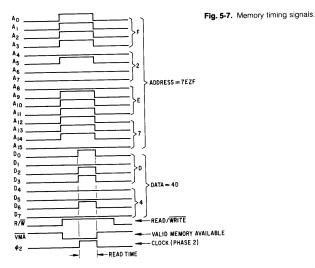

| Memory timing, 60                                       |     |

| Static vs. dynamic RAMs, 60                             |     |

| ROMs and PROMs, 61                                      |     |

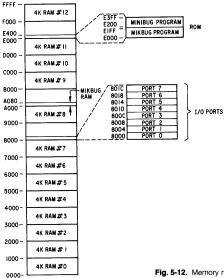

| Memory mapping, 64                                      |     |

|                                                         |     |

| 6. Microprocessors                                      | 66  |

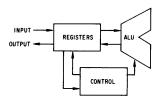

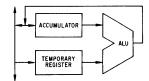

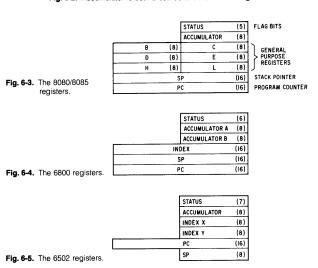

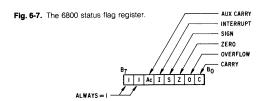

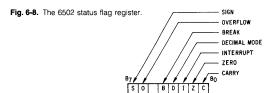

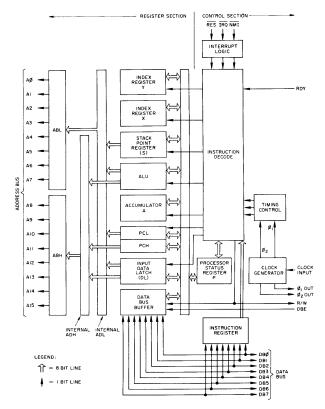

| Microprocessor architecture, 66                         |     |

| Computer operations, 71                                 |     |

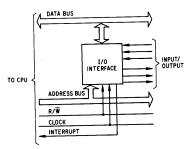

| Input/output (I/O), 72                                  |     |

| Interrupts, 72                                          |     |

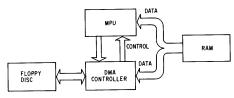

| Direct memory access (DMA), 72                          |     |

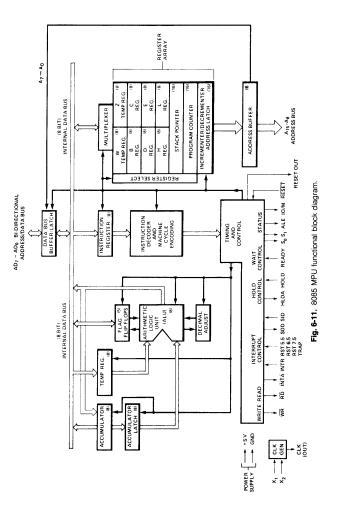

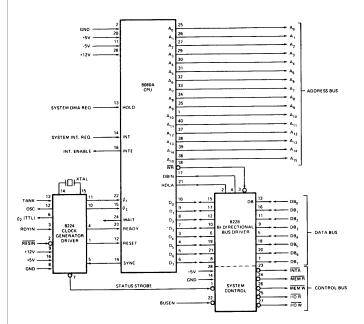

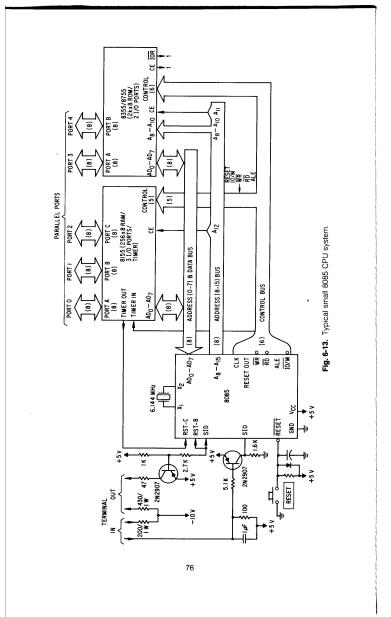

| The 8080/8085, 73                                       |     |

| The 6800, 77                                            |     |

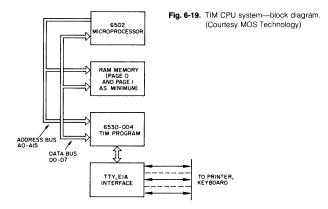

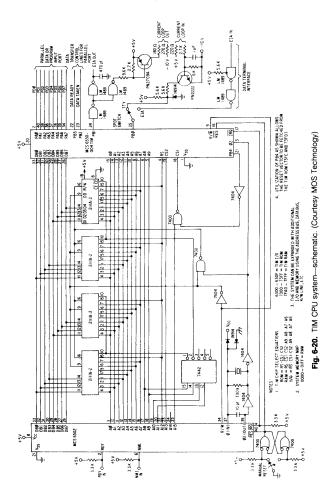

| The 6502, 80                                            |     |

| The Z-80, 84                                            |     |

| The 2-00, 04                                            |     |

| 7. The Ins and Outs of Interfacing                      | 86  |

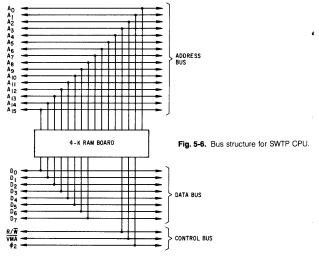

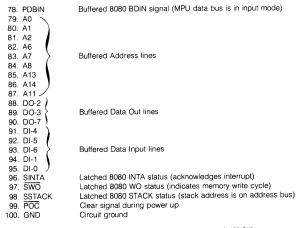

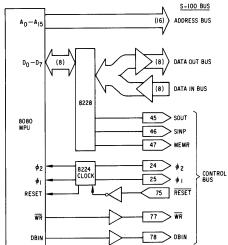

| The CPU bus (S-100), 87                                 |     |

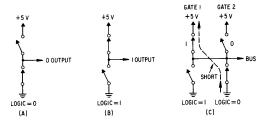

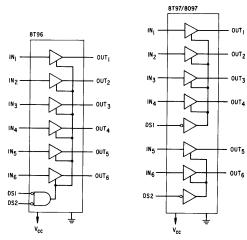

| Tri-state busing (TSL), 91                              |     |

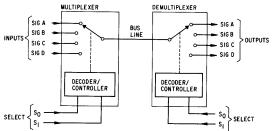

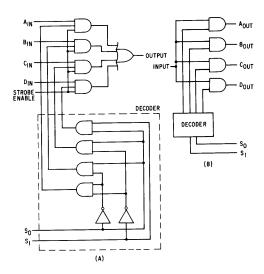

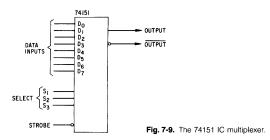

| Multiplexing and demultiplexing, 92                     |     |

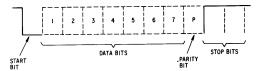

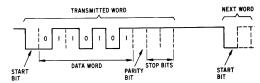

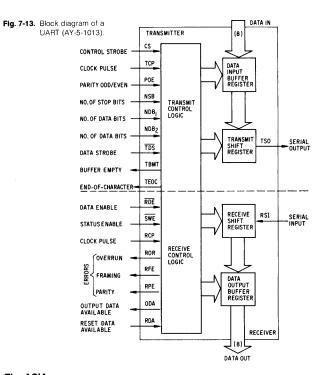

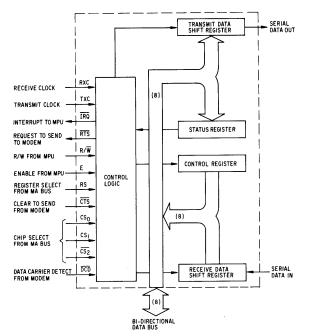

| Serial interfacing, 94                                  |     |

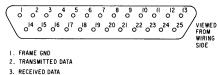

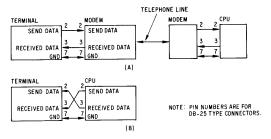

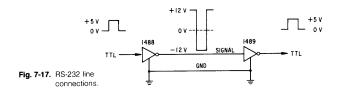

| RS-232 interface, 97                                    |     |

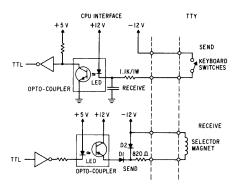

| Current loop interface, 99                              |     |

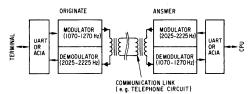

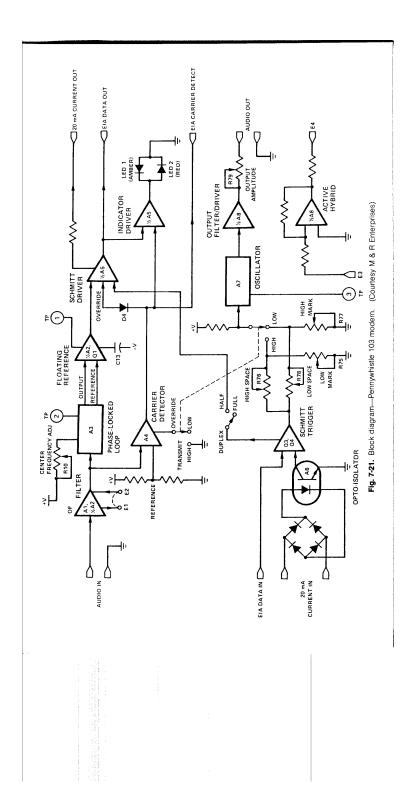

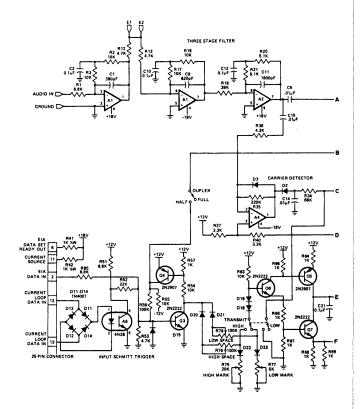

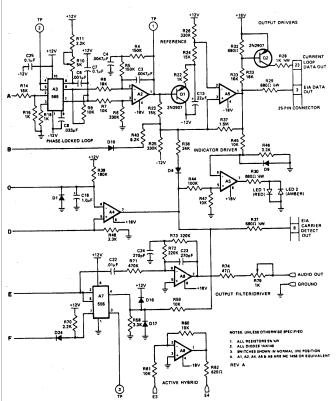

| Modems, 100                                             |     |

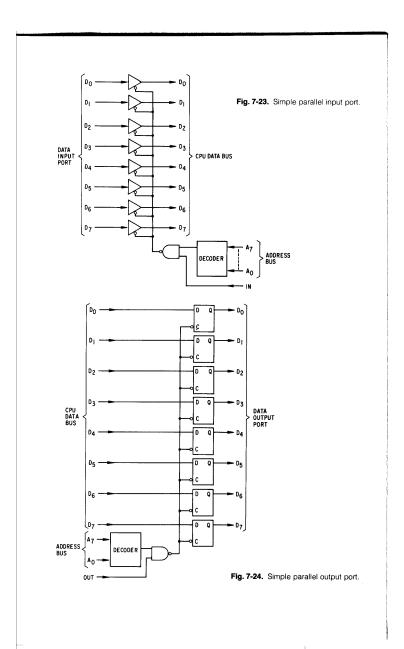

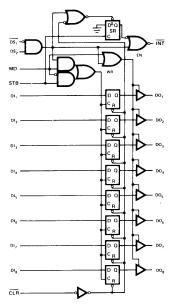

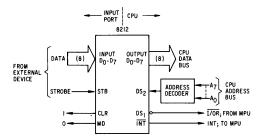

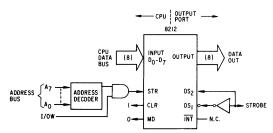

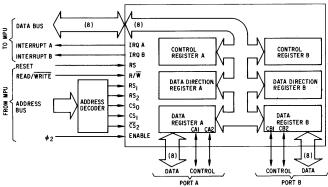

| Parallel interfacing, 103                               |     |

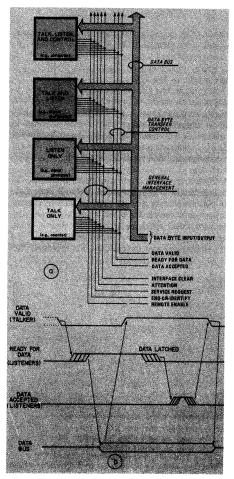

| The IEEE Std 488 bus, 109                               |     |

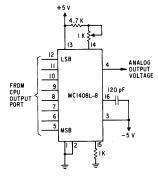

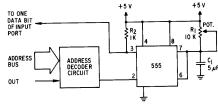

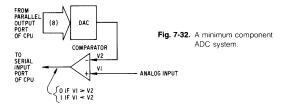

| Analog-to-digital and digital-to-analog conversion, 109 |     |

| Analog-to-aighta and aighta-to-analog conversion, 107   |     |

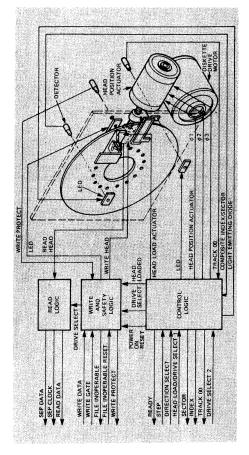

| 8. Mass Storage Systems                                 | 113 |

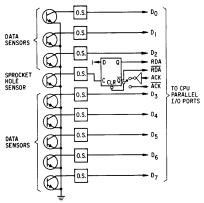

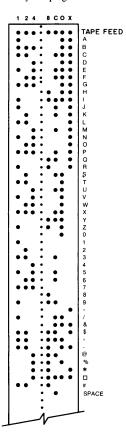

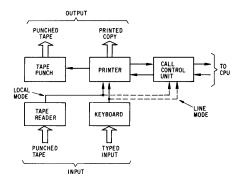

| Paper tape, 113                                         |     |

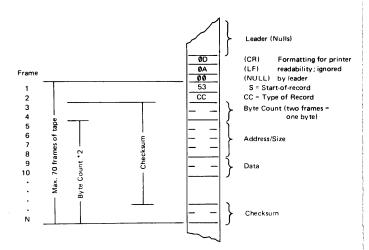

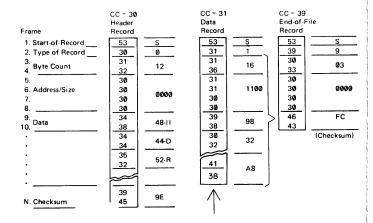

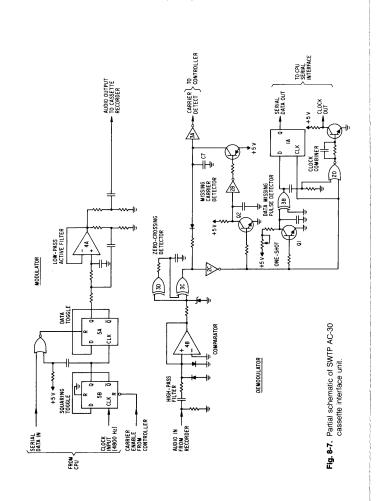

| Tape cassette, 117                                      |     |

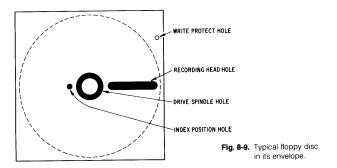

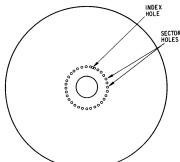

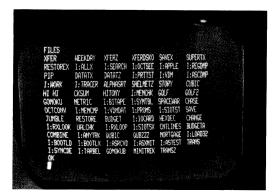

| Floppy discs, 122                                       |     |

| Bubble memory, 126                                      |     |

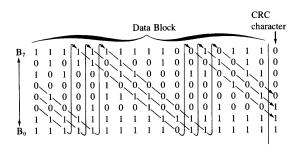

| Error-checking, 126                                     |     |

| Error Checking, 120                                     |     |

| 9. Input/Output Devices                                 | 128 |

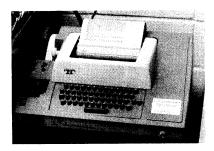

| Teletypes, 128                                          |     |

| Teletypewriters, 131                                    |     |

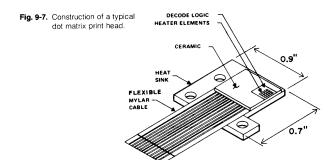

| Dot matrix printers, 132                                |     |

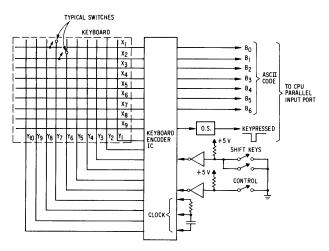

| Keyboards, 134                                          |     |

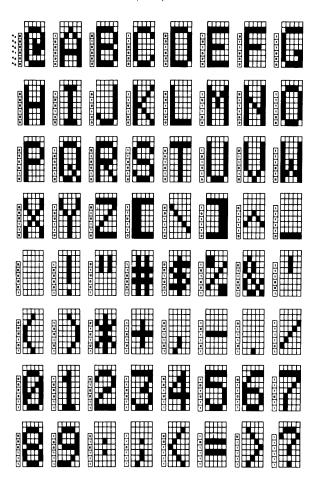

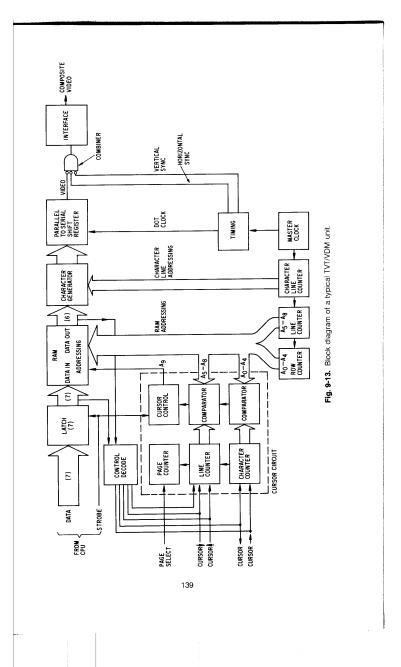

| The TVT and VDM, 135                                    |     |

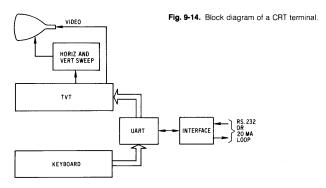

| CRT terminals, 137                                      |     |

| Line printers, 140                                      |     |

| · F                                                     |     |

53

5. To and From RAM and ROM

| 10  | C                                                                                                                                                                                                                                                                                                                                                                                                             | 142               |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 10. | Computer Software                                                                                                                                                                                                                                                                                                                                                                                             | 142               |

|     | What is software and programming, 142                                                                                                                                                                                                                                                                                                                                                                         |                   |

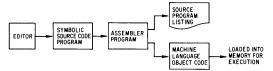

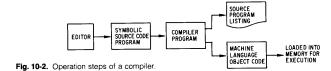

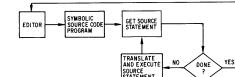

|     | Program codes—from the lowest to highest levels, 142                                                                                                                                                                                                                                                                                                                                                          |                   |

|     | High-level computer languages, 146                                                                                                                                                                                                                                                                                                                                                                            |                   |

|     | Systems software, 147 Other forms of assemblers and disassemblers, 147                                                                                                                                                                                                                                                                                                                                        |                   |

|     | Other forms of assemblers and assassemblers, 147                                                                                                                                                                                                                                                                                                                                                              |                   |

| 11. | The Computer's Instruction Set                                                                                                                                                                                                                                                                                                                                                                                | 148               |

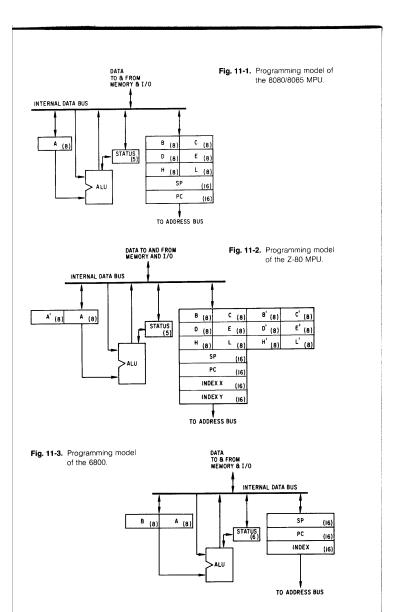

|     | MPU architecture, 148                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|     | MPU instructions, 150                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|     | Addressing modes, 151                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|     | I/O addressing, 152                                                                                                                                                                                                                                                                                                                                                                                           |                   |

|     | The instruction set, 153                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|     | In conclusion, 157                                                                                                                                                                                                                                                                                                                                                                                            |                   |

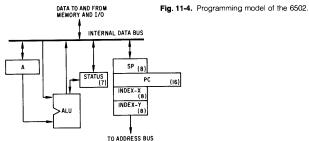

| 12. | Introduction to Programming                                                                                                                                                                                                                                                                                                                                                                                   | 159               |

|     | Which language to use, 159                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|     | Writing assembly level programs, 161                                                                                                                                                                                                                                                                                                                                                                          |                   |

|     | The editor/assembler, 162                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|     | Macroassemblers, 164                                                                                                                                                                                                                                                                                                                                                                                          |                   |

|     | Debugging, 165                                                                                                                                                                                                                                                                                                                                                                                                |                   |

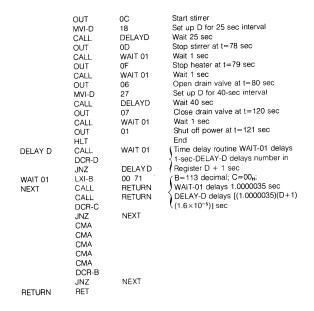

|     | Program examples, 165                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 12  | Programming with BASIC                                                                                                                                                                                                                                                                                                                                                                                        | 168               |

| 13. |                                                                                                                                                                                                                                                                                                                                                                                                               | 100               |

| 13. |                                                                                                                                                                                                                                                                                                                                                                                                               | 108               |

| 13. | The BASIC program, 168                                                                                                                                                                                                                                                                                                                                                                                        | 100               |

| 13. | The BASIC program, 168 Some BASIC fundamentals, 169                                                                                                                                                                                                                                                                                                                                                           | 108               |

| 13. | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170                                                                                                                                                                                                                                                                                                                                      | 100               |

| 13. | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170                                                                                                                                                                                                                                                                                                                 | 106               |

| 13. | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171                                                                                                                                                                                                                                                                                           | 100               |

| 13. | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170                                                                                                                                                                                                                                                                                                                 | 100               |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174                                                                                                                                                                                                                                        |                   |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173                                                                                                                                                                                                                                                            | 177               |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174                                                                                                                                                                                                                                        |                   |

|     | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications                                                                                                                                                                                                                          |                   |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications Game playing, 177                                                                                                                                                                                                        |                   |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications Game playing, 177 Word processing, 179                                                                                                                                                                                   |                   |

|     | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications Game playing, 177 Word processing, 179 Computer music, 180                                                                                                                                                               |                   |

|     | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182                                                                                                                                            |                   |

|     | The BASIC program, 168 Some BASIC fundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications  Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182 Business applications, 183                                                                                                                |                   |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications  Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182 Business applications, 183 Robotics, 184                                                                                                  |                   |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications  Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182 Business applications, 183 Robotics, 184 Automatic control, 185                                                                           | 177               |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications  Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182 Business applications, 183 Robotics, 184 Automatic control, 185  Appendix A. Hex-ASCII table                                              | 177               |

|     | The BASIC program, 168 Some BASIC jundamentals, 169 BASIC operators, 170 BASIC functions, 170 BASIC statements, 171 Lists, tables, and arrays, 173 Fun with BASIC, 174  Applications  Game playing, 177 Word processing, 179 Computer music, 180 Amateur radio, 182 Business applications, 183 Robotics, 184 Automatic control, 185  Appendix A. Hex-ASCII table Appendix B. 8080 instruction codes, by group | 177<br>188<br>189 |

# Introduction

# THE ADVENTURE AND EXCITEMENT OF PERSONAL COMPUTING

Bob Adams sits down in front of the computer terminal. He presses some keys on the keyboard and a message appears on the screen:

HELLO BOB

TODAY IS WEDNESDAY

TIME IS 12:30 P.M.

OUTSIDE TEMPERATURE IS 10°C

INSIDE TEMPERATURE IS 20°C

ALL SYSTEMS ARE OPERATING CORRECTLY

Bob hits another key. A new message appears on the screen.

THE FOLLOWING PROGRAMS ARE ON-LINE:

CHESS

CAI

OPTIONS

1

Bob types ''chess'' on the keyboard. Immediately a chess board appears on the screen with a full array of chessmen and the message:

Bob types "yes" and the game is under way. Bob is playing chess with the computer.

Bob is doing all this at home. In his own study, with his own home-built computer. It may sound like science fiction from the year 2000, but it isn't. It's today and Bob is not unique. He is one of thousands of computer hobbyists who have built their own home personal computer systems. In fact, Bob found that building his computer was as exciting as using it.

Two years ago Bob was very ignorant about computers. Quite by chance one day, he passed a computer store. Being curious he went in and he found it to be a fascinating place. He spent 2 hours playing with several demonstration systems that were in operation. Bob learned of the kits that were available, and he bought some books on computer basics. He also went to some meetings of a local amateur computer club. He learned from his reading and from other hobbyists that computers, although very powerful machines, are not really that complicated.

As he came to know more about computers he realized that a computer is really nothing more than a machine, but it is the ultimate machine. Machines are designed and built by man to perform operations previously done by man himself. Machines can usually do these tasks better and faster. For example, the automobile performs the job of transporting us from one place to another, which was previously done only by our legs. But, in many cases, the automobile does it better and faster.

The computer is taking over operations previously done only by our brain. We could say that a computer is man's attempt to emulate the human mind. The mind is the central control center of our bodies. The computer is also a control center. Today's computers can perform many tasks performed previously by human minds. As such, it becomes an extension of the human mind, enabling us to do things better and faster.

Introduction

It is these realizations that so excited Bob. Finally, Bob decided to build his own computer.

# IT'S EASY TO BUILD A HOME COMPUTER SYSTEM

Bob consulted some of the computer club members and he got advice on which kits to buy for his intended system. Bob already had experience in assembling a kit—a Heathkit hi-fi receiver.

Much to his amazement he found that the computer kits were simpler than that of the hi-fi receiver. However, the instructions were not always clear and there were a great many unfamiliar terms. He proceeded slowly, consulting his computer club friends and the computer store owner. He found that many of the components were similar to his hi-fi kit, and assembling the electronics required basically the same tools he had used for his hi-fi kit.

He built one unit at a time. First he assembled the *TV terminal* and then the *keyboard*. He connected it to his TV receiver and was delighted when he saw the screen fill up with alphanumeric characters. Following the checkout procedure in the manual, he found that he could type on the keyboard and the characters appeared on the TV screen. He had, in effect, assembled a "TV typewriter."

He was eager now. He proceeded to assemble the *central processor unit*, called a *CPU* for short. Following the manual, he performed some simple electrical tests with an inexpensive voltmeter. It passed the electrical tests.

Now the day came. Bob connected the TV terminal to the CPU. He turned on power and pressed the reset switch. The computer responded by typing ''ready'' on the screen. Bob jumped for joy. The computer was communicating with him, telling him it was ready to be programmed.

Bob was now over the hardware phase of building his system, and he had done it in only a few weeks of spare-time activity. He felt a sense of accomplishment.

#### WHAT DO PEOPLE DO WITH HOME COMPUTERS

Now that Bob had his computer system working—or, as the pro's say, "his hardware was operational":—Bob found that a lot more work was required to make his computer really work. This is what the pro's called the *software* phase. Software is the program—the instructions, to tell the computer what to do and how to do it.

The computer brain, as created, is essentially empty... like a newborn baby. Just as it is the responsibility of parents to teach an infant what to do and how to do it, the computer must be trained for its tasks. This training is called programming.

Bob attended some classes in programming run by his computer club and a nearby college. He found that the computer understood a limited set of instructions, and that with these, a language could be constructed to make it easier to communicate with the computer.

Bob learned that there was a simple computer language, called BASIC, already available for his computer system. He soon learned how to educate his computer quickly by loading the BASIC language into the memory of his computer, using an ordinary audio cassette recorder. The entire process took only a few minutes, and Bob now had an intelligent computer system. He could now communicate with the computer by using ordinary English words like "let" and "print."

Soon Bob found that he could instruct the computer—in the BASIC language—to maintain his financial records, calculate things like interest and depreciation, and even help prepare his income tax return. As Bob came to have a better understanding of hardware and software, he found that his system was extremely versatile and could be expanded to handle the storage of records, control the operation of appliances, and even work as an intelligent typewriter (the pro's call this word processing). At computer club meetings he heard about other applications for which home computers are being used. He saw both a computer-controlled robot built by a young high school student and a computer-controlled amateur radio station. He learned of how one amateur uses his computer to assist him in playing the stock market; and he discovered many of the marvelously sophisticated games that could be played with computers.

#### WHAT THIS BOOK IS ABOUT

This book is intended to be a handbook and primer for those new to the field of personal home computers. It provides the necessary background in digital logic fundamentals, number systems, computer hardware, and software basics. Only a minimal knowledge of electronics is required. The theory is presented in a straightforward manner without need to resort to complex theorems. The emphasis is on the important practical knowledge that the home computer user should have to be able to purchase components intelligently, assemble them, and interconnect them.

The material contained in this book has been organized into four basic sections: background information (Chapters 1 through 4), personal computer hardware (Chapters 5 through 9), personal computer software (Chapters 10 through 13), and personal computer applications (Chapter 14).

Further, it provides an introduction to the area of programming on both the lower machine level and the use of higher-level languages such as BASIC. This book will also serve as a reference handbook. Hence the reader can keep it handy to look up facts and definitions, as required, when reading other books.

Introduction

This book is esentially an overview of the entire subject. The subject is far too extensive to be covered thoroughly in such a short book. Hence, many references are given, at the end of each chapter, for further in-depth reading. Additionally, the reader might also wish to study the author's other texts—one entitled Fundamentals and Applications of Digital Logic Circuits, also published by Hayden Book Company, Inc.; the other on microcomputer interfacing, which is now in preparation.

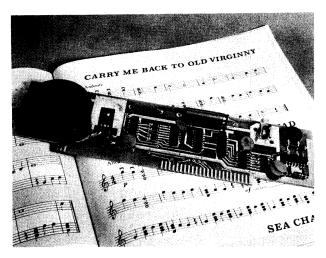

The author at work on a typical home personal computer system.

# 1.

# Computer Codes, Bits, Bytes, and Arithmetic

When we count, we are using a code. We use a code based on the number 10. This code was adopted by man thousands of years ago, probably because man has ten fingers on his two hands. Thus we count 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, etc. We call this "base 10."

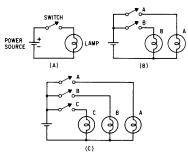

A computer uses only switches. Actually, transistors are used as electronic switches. A switch has two positions, open and closed. Hence, it has only two states and we say that it can count by two. Fig. 1-1A illustrates a simple switching circuit consisting of a switch, lamp, and power source. When the switch is open, the lamp is unlit, and when it is closed the lamp is lit.

Fig. 1-1. Simple switch-lamp binary counting circuit.

## **BINARY NUMBERS**

When the lamp is unlit we consider this a count of zero (0) and when it is lit, it is a count of one (1). There are only these two counts (or states) and hence it

is called a binary system, meaning two states. Therefore, computers that use

switching circuits are called binary computers.

To count to higher numbers we can add switches and lamps, as shown in Fig. 1-1. Two switches (Fig. 1-1B) allow us to count four states:

| Binary<br>B A | Decima |

|---------------|--------|

| 0 0           | 0      |

| 0 1 1 0       | 1 2    |

| 1 1           | 3      |

Three switches (Fig. 1-1C) permit us to count eight states.

| Binary |   |   |   |  |        |

|--------|---|---|---|--|--------|

|        | С | В | Α |  | Decima |

|        | _ | _ | _ |  |        |

|        | 0 | 0 | 0 |  | 0      |

|        | 0 | 0 | 1 |  | -1     |

|        | 0 | 1 | 0 |  | 2      |

|        | 0 | 1 | 1 |  | 3      |

|        | 1 | 0 | 0 |  | 4      |

|        | 1 | 0 | 1 |  | 5      |

|        | 1 | 1 | 0 |  | 6      |

|        | 1 | 1 | 1 |  | 7      |

|        |   |   |   |  |        |

We are actually counting to the base 2. Hence the A column has a value of

We are actuary counting to the Case 2. There are a command where 3 (2°), the B column is 2 (2¹), and the C column is 4 (2²). If we added a fourth switch and lamp, it would have a value of 8 (2³), and we could count 16 states.  $(2^3 + 2^2 + 2^1 + 2^0 = 8 + 4 + 2 + 1 = 15$ , which when added to the zero state gives us the 16 states.)

| -   |                                                     |                                                                                                                                                                                                                               |                                                                                                                              |                                                                                                                                                                          |

|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bin | ary                                                 |                                                                                                                                                                                                                               |                                                                                                                              |                                                                                                                                                                          |

| С   | В                                                   | Α                                                                                                                                                                                                                             |                                                                                                                              | Decimal                                                                                                                                                                  |

| 0   | 0                                                   | 0                                                                                                                                                                                                                             | Î                                                                                                                            | 0                                                                                                                                                                        |

| 0   | 0                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 1                                                                                                                                                                        |

| 0   | 1                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 2                                                                                                                                                                        |

| 0   | 1                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 3                                                                                                                                                                        |

| 1   | 0                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 4                                                                                                                                                                        |

| 1   | 0                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 5                                                                                                                                                                        |

| 1   | 1                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 6                                                                                                                                                                        |

| 1   | 1                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 7                                                                                                                                                                        |

| 0   | 0                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 8                                                                                                                                                                        |

| 0   | 0                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 9                                                                                                                                                                        |

| 0   | 1                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 10                                                                                                                                                                       |

| 0   | 1                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 11                                                                                                                                                                       |

| 1   | 0                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 12                                                                                                                                                                       |

| 1   | 0                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 13                                                                                                                                                                       |

| 1   | 1                                                   | 0                                                                                                                                                                                                                             |                                                                                                                              | 14                                                                                                                                                                       |

| 1   | 1                                                   | 1                                                                                                                                                                                                                             |                                                                                                                              | 15                                                                                                                                                                       |

|     | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0 | 0 0 0 0 0 1 0 1 1 0 0 0 0 0 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | C B A  0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 1 0 1 1 0 0 1 1 1 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 1 1 1 1 0 0 1 1 1 1 0 0 1 1 1 1 0 1 | C B A  0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 1 0 0 1 1 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 1 0 0 1 1 1 1 1 0 0 1 1 1 1 1 0 0 1 1 1 1 1 1 0 0 1 1 1 1 |

We could continue increasing the number of switches to count to larger numbers. Our binary numbers use only the digits 0 and 1. Each digit is called a binary bit, and a group of bits is called a binary word. We usually group the bits into groups of 8 bits and refer to such a grouping as a byte. The A-bit would be called the LSB (least significant bit) and the D-bit would be called the MSB (most significant bit).

#### Converting from Binary to Decimal and Vice Versa

To convert from binary-to-decimal we sum the place values of the 1-bits. For example, convert the binary number 10010111 to decimal, as follows:

Notice that we have summed the decimal place values for all the 1-bits. The decimal place values for the 0-bits are ignored.

Now to convert from decimal-to-binary. This is done by subtracting the largest base-2 value from the decimal number, then subtracting the next largest subtractable base-2 number from the remainder. A 1 is used for each base-2 value subtracted and a 0 for each value not subtractable. Here is an example—convert decimal 182 to binary as follows:

182 decimal number

-128

$$2^7(128)$$

→ 1

54  $2^6(64)$  not used→0

-32  $2^5(32)$  → 1

-16  $2^4(16)$  → 1

-6  $2^3(8)$  not used→0

-4  $2^2(4)$  → 1

-2  $2^1(2)$  → 1

0  $2^0(1)$  not used→0

182<sub>10</sub> = 10110110<sub>2</sub> →

## **OCTAL AND HEX NUMBERS**

The computer works with binary words. However, humans have difficulty working with larger binary numbers and have adopted other codes to simplify computer work. The two most used codes are the *octal* and *hexidecimal* (called

$\it hex$  for short) codes. The octal code is based on grouping the bits into groups of threes. For example:

| 011 | 000 | 101          | 110 | binary |

|-----|-----|--------------|-----|--------|

| 1   | ↓   | $\downarrow$ | 1   |        |

| 2   | Δ   | -            | 6   | ootal  |

It is much easier to remember octal 3056 than its binary equivalent of 011000101110. Thus, to convert from binary to octal, group the bits into groups of three each and convert each 3-bit group to its octal number. It is called octal since only eight numbers, 0-7, are used.

Here is another example: Convert 1234 (octal) to binary:

Notice the subscripts 8 and 2 are used to indicate the octal and binary numbers.

Hex code is also very popular because it is even easier to remember than octal. To convert from binary to hex, group the bits into groups of four. Note that to represent 16 states it is necessary to use letters as well as numbers as follows:

| Hex | Decimal | Binary |

|-----|---------|--------|

| 0   | 0       | 0000   |

| 1   | 1       | 0001   |

| 2   | 2       | 0010   |

| 3   | 3       | 0011   |

| 4   | 4       | 0100   |

| 5   | 5       | 0101   |

| 6   | 6       | 0110   |

| 7   | 7       | 0111   |

| 8   | 8       | 1000   |

| 9   | 9       | 1001   |

| Α   | 10      | 1010   |

| В   | 11      | 1011   |

| С   | 12      | 1100   |

| D   | 13      | 1101   |

| Ε   | 14      | 1110   |

| F   | 15      | 1111   |

To convert from binary to hex, group and convert as follows:

This is the same number we converted originally into octal 3056. Note now that only three hex digits are needed compared to the four octal digits. Fewer digits make the number easier to remember and cut down the chance for errors to be made. Observe that a subscript H is used to denote the hex number.

If we wish to convert from octal to hex or vice versa, an easy way to do it is to convert to binary first. For example, to convert from  $5F_{\rm H}$  to octal:

Several other computer codes are used, but octal and hex are the most popular. When communicating between the computer and a terminal, such as a Teletype\*, an expanded code which can be used to denote all the printable characters and control codes is required. For this purpose the computer industry has tstandardized on the ASCII code (American Society for Communications Interface and Interchange). The ASCII (pronounced as-key) code uses an 8-bit byte and is included in Appendix A.

#### **BINARY ARITHMETIC**

We can add binary numbers in a manner similar to adding decimal numbers. Here are the four basic rules:

Rule 1, Rule 2, Rule 3, Rule 3, Rule 4,

$$\bigcirc$$

11 carry  $\bigcirc$  12 carry  $\bigcirc$

In Rules 3 and 4 note that a *carry* is generated from the previous column to the next column. Here are two examples:

### **Binary Subtraction**

Most microprocessors use a technique called 2's complement subtraction. In this way the basic adder circuit can also be used to perform subtraction. The technique requires that the number being subtracted be complemented and a 1 added to it. To complement a binary number means to change each 1 to 0 and

<sup>\*</sup>Registered trademark of the Teletype Corp.

each 0 to a 1. Then adding a 1 to the complemented binary word makes it a 2's complement. For example:

Binary number Complement 2's Complement 011

$$\longrightarrow$$

010 +1 = 011 0001  $\longrightarrow$  1110 +1 = 1111

Subtraction is performed by adding the 2's complement of the number being subtracted to the number from which it is being subtracted and disregarding the last carry. Example:

y. Example:

Decimal 10 1010

$$\longrightarrow$$

1010 (no change)

$-6 \longrightarrow 4$   $\longrightarrow$  1001+1 $\longrightarrow$ +1010 (2's complement)

$\longrightarrow$  disregard last carry

Another example:

When the last carry = 1, the answer is positive. When the carry = 0 (no carry), the answer is negative and is the 2's complement of the result.

## **Binary Multiplication**

Binary multiplication is similar to decimal multiplication. The technique is called *summing partial products*. The following rules apply:

Rule 1, 0 Rule 2, 0 Rule 3, 1 Rule 4, 1

$$\frac{\times 0}{0}$$

$\frac{\times 1}{0}$   $\frac{\times 1}{0}$   $\frac{\times 0}{0}$

To multiply we find all the partial products, shifting each to the left one place and summing the partial products. In this way the operation can be done by the adder circuit in the computer. For example:

$$\begin{array}{ccc}

9 & 1001 \\

\times 5 & \times & 101 \\

\hline

45 & 0000 & \leftrightarrow \text{partial products} \\

\hline

1001 & & \leftarrow \text{final product}

\end{array}$$

### **BCD NUMBERS**

Most calculators and some computers use a BCD code (binary-coded-decimal). Although this code uses more bits it is easier to handle. The code

consists of using 4-bit binary groups to represent the decimal digits 0 through 9. Hence, there will be a 4-bit binary group for each decimal digit. For example, the decimal number 185 would be represented as follows:

BCD arithmetic is performed somewhat differently than binary arithmetic. For example, each 4-bit group is added in standard binary fashion. However, if the sum is greater than  $1001_2(9_{10})$ , then a carry is generated to the next group, and  $1010_2(10_{10})$  is subtracted from the group. Here is an example.

Most microprocessors have instructions which facilitate BCD arithmetic operations.

## **Recommended Further Reading**

Sol Libes, Fundamentals and Applications of Digital Logic Circuits, Revised Second Edition, Hayden Book Co., Inc., Rochelle Park, N.J., 1978.

# 2.

# Digital Logic

The circuitry of a computer consists of millions of electronic switches. These switches are arranged to perform operations and make decisions and hence are called *logic* circuits. Present technology can house thousands of switching circuits in one case called an integrated circuit (Fig. 2-1).

Fig. 2-1. Typical integrated circuit.

The switches are actually transistors which are caused to turn on or off. For short, we call an *integrated circuit* an *IC*.

## LOGIC STATES

In our simple logic circuit (Fig. 2-2) we indicate that the switch is ON by a 1 and OFF by a 0. Often a +5 V (actually between +2.4 and +5 V) is usually taken to be a 1-logic level and 0 V (actually 0 to 0.4 V) a 0-logic level. We may also say that a 1 is a high or hi logic level and a 0 is a low or lo logic level.

Fig. 2-2. Simple logic circuit.

#### **DIGITAL LOGIC GATES**

Logic circuits are electronic circuits that switch between logic-0 and 1 states. They are like switches that open and close and are, therefore, referred to as *gates*. A gate has two or more inputs and one output. This output occurs when certain conditions are met. The gate's operation is analyzed with a *truth table* which shows all input and output possibilities of the gate.

The very earliest gate circuits used relays. Later, vacuum tubes, diodes, and transistors were used. Today, gates are made from integrated circuits (ICs) almost exclusively. The IC is a plastic or ceramic package which contains transistors, diodes, and resistors assembled to form gates. Therefore, it will be better to concern ourselves with the gate as a functional block rather than the inner workings of the circuit.

There are three basic logic circuits. They are the AND, OR, and NOT (inverter). All other logic circuits are built from these basic logic circuits.

#### The AND Gate

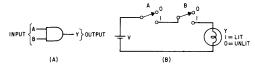

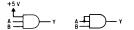

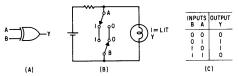

The AND gate (Fig. 2-3A) has two inputs. When one or both inputs = 0, the output is 0. Only when both inputs = 1 will the output = 1. It operates in the same way as two switches connected in series (Fig. 2-3B). Only when switches A and B are closed (1 position) will the lamp light (1).

Fig. 2-3. A 2-input AND gate (A) and equivalent switch circuit (B).

Only when A and B are 1 will Y (output) be 1, hence the name AND gate. If either or both switches are open, or 0, no current will flow through the switches and there will be a 0 output (Y).

We can construct a truth table (Table 2-1) which describes the output Y of the AND gate. It shows that there are four possible combinations of input states

Table 2-1. 2-Input AND Gate

|        | -      |

|--------|--------|

| Inputs | Output |

| B A    | Y      |

| 0 0    | 0      |

| 0 1    | 0      |

| 1 0    | 0      |

| 1 1    | 1      |

giving 1 and 0 at the output. In three of the combinations Y=0. Only if A and B are 1 will Y=1.

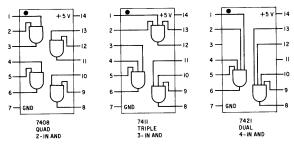

The number of gate inputs can be increased, just as the number of switches can be increased. Figure 2-4 is a 3-input AND gate with its switch equivalent circuit. The truth table is shown in Table 2-2. Notice that the 3-input gate has eight possible states, but again only when all inputs =1 will the output =1. Figure 2-5 shows the pin-out diagrams for three popular IC AND gates.

Fig. 2-4. A 3-input AND gate (A) and equivalent switch circuit.

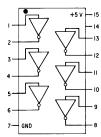

Fig. 2-5. Popular AND gate IC packages.

The diagram shows the pin connections within the IC. Note that a dot on the IC case usually indicates pin #1. On a 14-pin IC pins 7 and 14 are often used for the ground and +5~V connections, respectively.

Frequently when constructing circuits it is necessary to convert a gate with many inputs to one with fewer inputs. Two methods for doing this are shown in Fig. 2-6; in both, the 3-input AND gate will function as a 2-input AND gate.

**Fig. 2-6.** Two methods of converting a 3-input AND gate to a 2-input AND gate.

# The OR Gate

The schematic symbol for an OR gate is illustrated in Fig. 2-7A. The 2-input OR gate will have a 1 output when A or B=1, hence the name OR gate. The equivalent switch circuit is shown in Fig. 2-7B. Note that the two switches are in parallel so that if switch A or B is closed, current flows and lights the lamp. The truth table is shown in Fig. 2-7C. The logic symbol, equivalent

Fig. 2-7. The 2-input OR gate.

Fig. 2-8. The 3-input OR gate.

**Fig. 2-9.** Pin-out diagram for the 7432 quad 2-input OR gate IC.

Digital Logic 17

switch circuit, and truth table for a 3-input OR gate are shown in Fig. 2-8. Figure 2-9 shows the pin-out diagram for a popular IC OR gate.

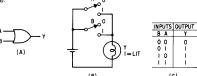

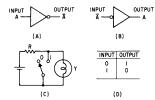

## The NOT (Inverter) Gate

The NOT circuit, usually called an *inverter* (Fig. 2-10), inverts a logic level. This is indicated by a circle, usually called a *bubble*, at the gate's input or output. A bar is placed above the input or output letter  $(\bar{A})$  to represent the opposite (inverted) logic state. It is said that the circle and bar indicate the action of *complementing* and *negating*. Hence, if the inverter input = 0, the output = 1; and if the input = 1, the output = 0 (Fig. 2-10A and B).

Fig. 2-10. The inverter or NOT gate.

In other words, the output is always the opposite state or complement of the input and hence, NOT the input. The equivalent switch circuit and the truth table are shown in Fig. 2-10C and D, respectively. Note that a resistor is used in when the switch circuit in order to prevent the power source from being short-circuited when the switch is in the 1 position. Figure 2-11 illustrates the pin-out diagram for a popular IC inverter.

Fig. 2-11. Pin-out diagram for the 7404 hex-inverter IC.

#### The NAND and NOR Gates

The NAND and NOR gates are the most widely used logic gates, because any type of gate can be made from them. There have been entire systems built exclusively with NAND or NOR gates. Hence, they are considered to be universal gates.

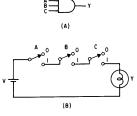

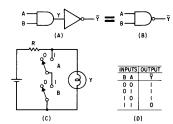

The NAND is basically an AND gate followed by an inverter (Fig. 2-12A). Hence, the logic symbol is an AND gate symbol with a bubble on the output (Fig. 2-12B). The equivalent switch circuit and truth table for the NAND gate are shown in Fig. 2-12C and D. Only when A and B=1 will the output =0.

Fig. 2-12. The NAND gate.

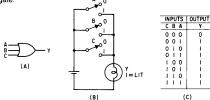

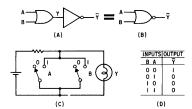

The NOR gate is essentially an OR gate followed by an inverter (Fig. 2-13A). The logic symbol is, therefore, an OR gate symbol with a bubble at the output (Fig. 2-13B). The equivalent switch circuit and truth table are shown in Fig. 2-13C and D. When A or B = 1 the output Y = 0.

Fig. 2-13. The NOR gate.

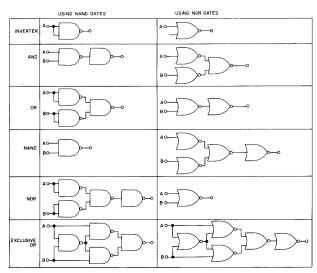

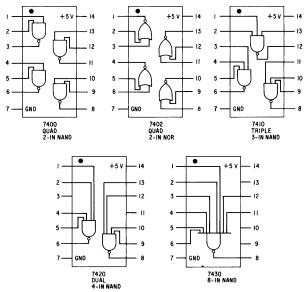

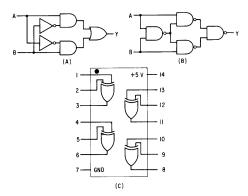

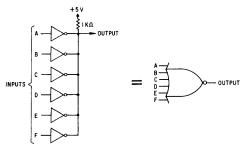

It is possible using only NAND or only NOR gates to perform any type of gate operation. Figure 2-14 shows how NAND and NOR gates can be used to build all other types of logic gates. Figure 2-15 shows the pin-out diagrams of several popular NAND and NOR gate ICs.

## The X-OR and X-NOR Gates

The exclusive-OR, popularly called X-OR, and the exclusive-NOR, or X-NOR, gates are widely used gates actually made from the previous gates. They compare inputs and are often called comparators.

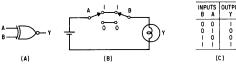

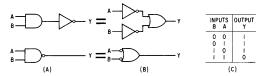

The X-OR gate symbol is shown in Fig. 2-16A with its equivalent switch circuit (B) and truth table (C). The circuit compares switches A and B (inputs). When the input states are opposite, current flows through the lamp and it will light (=1); when the inputs are the same the lamp will not light. The X-OR gate can thus be considered an *inequality detector*.

The X-NOR gate symbol is shown in Fig. 2-17A with its equivalent switch circuit (B) and truth table (C). The circuit compares input A and B and when they

Fig. 2-14. Using NAND and NOR gates to perform basic logic functions.

Fig. 2-15. Pin-out diagrams for popular NAND and NOR ICs.

Fig. 2-16. The X-OR gate.

Fig. 2-17. The X-NOR gate.

Fig. 2-18. Building X-OR gates using basic gates and the 7486 quad X-OR gate IC.

are identical Y = 1. The X-NOR gate can thus be considered an *equality detector*

The X-OR gate can be built using basic gates (Fig. 2-18A and B), and an IC X-OR gate is shown in Fig. 2-18C.

# THE PARITY-BIT AND ERROR-CHECKING

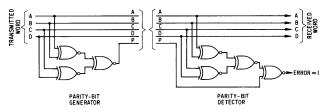

The X-OR and X-NOR gates find wide application in computer data transmission systems. Binary words are often checked as they are sent from one point to another to see that no error has occurred due to noise or equipment failure. This is done using X-NOR gates to generate a *parity-bit*.

The parity-bit is added to the data word and is used to check for errors. Even- and odd-parity systems are used. In the even-parity method, a 1-bit is added to the word if the number of 1-bits in the word is odd. In the odd-parity method, the 1-bit is added if an even number of 1-bits exist in the data word.

Figure 2-19 shows a system utilizing a 5-bit receiver input, where 4 bits are used for data and 1 bit is the parity-bit. The parity-bit generator circuit compares the 4-bit data word and generates the parity bit, so that the transmitted word consists of 5 bits. The parity-bit generator output = 0 for an odd number of 1s in the data word and the output = 1 for an even number of 1s in the data word. At the receiving point a parity-bit detector is used to compare the received word to the parity-bit. An error output is generated if they are not consistent.

Fig. 2-19. Parity-bit method used in data transmission system.

#### **ARITHMETIC CIRCUITS**

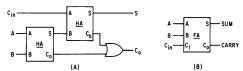

Binary addition (discussed earlier) is accomplished using *half-adder* and *full-adder* circuits. The half-adder circuit (Fig. 2-20A) sums two binary bits and produces the sum and carry. The functional block symbol for the *half-adder* (*HA*) is shown in Fig. 2-20B.

Fig. 2-20. The half-adder circuit.

The full-adder (FA) is shown in Fig. 2-21A. The FA sums two binary bits and the carry from a previous HA or FA. It produces a sum and carry. The functional symbol for the FA is shown in Fig. 2-21B.

Fig. 2-21. The full-adder circuit.

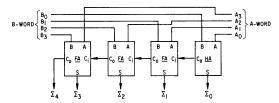

A circuit to add binary words (Fig. 2-22) is called a parallel-adder circuit since it adds all bits at one time. The circuit will sum two 4-bit words. It consists of a HA and 3 FAs. The LSB (least significant bit) requires only a HA since there is no carry-in.

Fig. 2-22. A circuit to add two 4-bit words.

# **DEMORGAN'S THEOREMS**

A very important facet of working with logic gates is referred to as *De-Morgan's Theorems*. These theorems are as follows:

- 1. A NAND gate performs the same logic function as an OR gate with negated inputs. This is shown in Fig. 2-23A and B. Fig. 2-23C shows the truth table which applies to both circuits.

- 2. A NOR gate performs the same logic function as an AND gate with negated inputs. This is shown in Fig. 2-24A, B, and C.

Fig. 2-23. The equivalency of NAND and negated input-OR gates.

Fig. 2-24. The equivalency of NOR and negated input-AND gates.

The equivalency of these gates enable the use of NAND gates to be used as OR gates and the use of NOR gates to perform AND operations.

It is, therefore, very important to note where the bubbles appear on logic gate symbols. For example, a bubble at an input and no bubble at the output indicates that 0-logic levels at the input will produce a 1-logic at the output. The showing of a NAND gate on a schematic as a negated-input-OR gate often better describes to the reader the logic operation being performed.

#### **BUILDING INVERTERS FROM OTHER GATES**

Frequently inverters are made using NAND, NOR, and X-OR gates. This usually occurs because of unused gates in IC packages and the desire to use as few ICs as possible in a system. Figure 2-25 shows how an inverter is built using these gates. Note that the X-OR and X-NOR gates may also be used as controlled inverters if the input, which is shown = 0 (X-OR) or 1 (X-NOR), is used as an enable input. Note also that the arrangements shown in Fig. 2-25A and C are preferred to B and D since this method presents less of a load to the driving circuit.

Fig. 2-25. Using NAND, NOR, X-NOR, and X-OR gates as inverters

#### **ENCODER AND DECODER CIRCUITS**

Logic gates are employed to perform logic functions. In this introductory book it is not feasible to discuss all possible applications. One of the most common applications of logic gates is that of code conversion—converting from decimal-to-binary and from binary-to-decimal. The former is called *encoding* and the latter *decoding*.

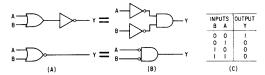

A typical decimal-to-binary encoder circuit is shown in Fig. 2-26. It is typical of the circuit used to convert decimal keyboard output to binary. In other words, when a particular decimal switch is closed on the keyboard, the encoder circuit will develop the correct binary code for the computer.

Note that closing a keyboard switch places a 0 at the particular gate inputs to produce the desired 1 outputs. Hence, the bubbles appear at the inputs. In actuality the circuit is built using NAND gates but the logic functions performed are those of negated-input OR gates.

Fig. 2-26. A decimal-to-binary encoder circuit (10-line to 4-line).

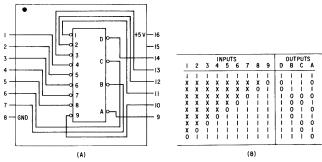

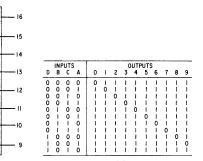

A popular decimal-to-binary encoder IC, also called a 10-line to 4-line encoder, is shown in Fig. 2-27A and its truth table in 2-27B. Note that the desired inputs and outputs are 0-logic levels and, hence, bubbles are shown at both inputs and outputs. In the truth table the X indicates a "don"t-care" state; in other words, it does not matter whether the input is 1 or 0 to achieve the desired output.

Fig. 2-27. The 74147 10-line to 4-line encoder IC.

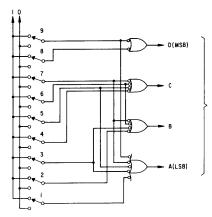

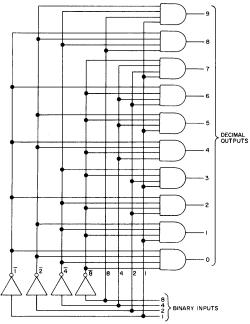

Fig. 2-28. A binary-to-decimal decoder circuit.

The decoder is the opposite of an encoder. For example, the circuit shown in Fig. 2-28 is a binary-to-decimal decoder circuit performing just the opposite code conversion of the previous circuit. Notice that the 4-bit binary word can produce up to 16 distinct outputs.

A popular binary-to-decimal decoder IC is shown in Fig. 2-29.

# TTL, CMOS, AND MOS

So far, we have avoided any discussion of the internal circuitry of ICs. However, a few words are needed here to distinguish between the different types of ICs. Currently there are three basic technologies in use—TTL, CMOS, and MOS.

+5 V

(A)

27

Fig. 2-29. The 7442 binary-to-decimal decoder IC.

TTL, as it is more commonly called, stands for transistor-transistor logic. For a detailed description of the circuit operation the reader is referred to the author's book Fundamentals and Applications of Digital Logic Circuits. TTL is very popular because of its low cost and good performance. All the ICs we have referred to previously are TTL ICs. TTL ICs always start with the designation 74 followed by two or three numbers designating the function. For example, the 7400 is a quad 2-input NAND IC. The 74xx family of ICs is furnished in plastic DIP cases and rated for operation from 0 to  $+70^{\circ}$ C. The 54xx family is the same as the 74xx with the exception that it is furnished in ceramic and rated for -55 to  $+125^{\circ}$ C operation.

Each TTL gate input presents a *unit load* and the gate output can drive up to 10 unit loads. TTL gates are available with high current outputs. They are called *buffers* and can drive 20 to 30 unit loads.

All TTL gates operate from a +5 V power supply, dissipate 10 MW per gate, and have a typical delay of 10 ns (nanoseconds). This means a maximum operating frequency of 35 MHz. High-speed TTL logic designated, with the letter H (i.e., 74H00), has only a 6-ns delay (maximum frequency = 50 MHz) but has an increased power dissipation of 22 MW/gate.

Low-power TTL, designated with the letter L (i.e., 74L00), has a power dissipation of only 1 MW/gate but is much slower (33-ns delay, 10-MHz maximum frequency). Higher frequencies are obtained using *Schottky* diodes with each transistor. These ICs are designated with the letter S (i.e., 74S00). They have a typical delay of only 3 ns (maximum frequency = 125 MHz).

It is also possible to obtain a low-power Schottky type TTL IC. This would be designated with the letters LS (i.e., 74LS00).

CMOS stands for complementary metal-oxide-silicon transistor. This is a newer technology than TTL and offers several advantages. It has very low power dissipation (2-3 MW/gate), very high noise immunity, draws very low current from the driving gate, and can drive up to 50 CMOS loads. However, it has a high delay time (25 ns).

MOS stands for metal-oxide-silicon transistor. ICs using this technology permit a very high density of electronic circuitry in a small piece of silicon. Most microprocessors and memory ICs are built using this technique. MOS ICs are limited in speed and power handling ability.

#### TRI-STATE AND OPEN-COLLECTOR ICs

Logic gates which are connected to a common line (we will discuss this in more detail later) usually employ a *tri-state* output circuit. This means that in addition to the 0- and 1-logic levels appearing at the output, a third state of infinite resistance (like an open switch) can exist. This is particularly useful when many gate outputs are connected to a common line called a *bus*.

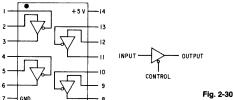

The third state is controlled by a special input to the IC which in effect turns the buffer off. For example Fig. 2-30 shows a buffer IC with tri-state outputs. Each buffer has a control input which when 0 allows the buffer to function as a noninverting logic gate. When the control input = 1 the buffer turns off and the gate is effectively disconnected from the output.

Fig. 2-30. The 74125 buffer with tri-state output.

Prior to the introduction of tri-state gates, bussing was accomplished using open-collector type gates. These gates are slower, less expensive, and more affected by noise than tri-state gates. However, they are in common use. In an open-collector type gate, a resistor which is normally internal to the IC-gate is omitted and instead is connected external to the gate. Using the external resistor permits wiring several open-collector type gate outputs together to share this resistor (Fig. 2-31).

Fig. 2-31. The 7405 hex inverter with open collectors functioning as a NOR

Notice that the output = 1 only when all inputs = 0 and that if any input = 01 the output = 0. Hence, the inverters have been wired to perform the function of a 6-input NOR gate.

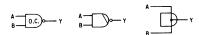

Unfortunately, most schematic diagrams do not distinguish between an open-collector and standard gate. However, sometimes the letters o.c. or a slash are used (Fig. 2-32).

Fig. 2-32. Different ways of indicating an open-collector type gate on schematics.

# **Recommended Further Reading**

- 1. Sol Libes, Fundamentals and Applications of Digital Logic Circuits, Revised Second

- Edition, Hayden Book Co., Inc., Rochelle Park, N.J., 1978.

2. Donald E. Lancaster, TTL Cookbook, Howard W. Sams & Co., Inc., Indianapolis, Ind., 1974.

- 3. Donald E. Lancaster, CMOS Cookbook, Howard W. Sams & Co., Inc., Indianapolis, Ind., 1977.

- 4. Digital, Linear, MOS Data Book, Signetics Corp., Sunnyvale, Calif., 1976.

3.

# More about Digital Logic

Flip-flops are circuits made up of gates which have the ability to store data and to count. As such they are the basic building blocks of memory and control/ timing systems.

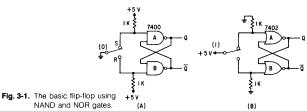

#### THE BASIC FLIP-FLOP (R-S)

A simple flip-flop can be constructed from two NAND or NOR gates (Fig. 3-1). In Fig. 3-1A the resistors are called *pull-up resistors* since, when the gate input is not grounded (0 logic level) through the switch, the gate input is "pulled-up" to a logic-1 level through the resistor. On the other hand, in Fig. 3-1B, when NOR gates are used, the resistors pull the input down to ground (0-logic level) when the switch is open. Hence, the resistors are called pull-down resistors. Notice a pull-up resistor is connected from a gate input to  $+5\,\mathrm{V}\,(1)$  and a pull-down resistor is connected from a gate input to ground (0).

Since the gate inputs and outputs are cross-connected, one gate will always have a 1 output while the other will always have a 0 output. The outputs are labeled Q and  $\bar{Q}$ . The line above the Q indicates that it is the opposite logic state of Q. Hence if Q=0 then  $\bar{Q}=1$  and vice versa. If Q=0 and  $\bar{Q}=1$  we call this the *reset* state. If Q=1 and  $\bar{Q}=0$  this is

called the set state. In Fig. 3-1A, if the flip-flop is reset, then moving the switch up will cause the flip-flop to set. This occurs because gate A has 0 inputs and output = 1 while gate B has 0 and 1 inputs and output = 0. Notice that the switch is labeled S on the side which will cause the flip-flop to set.

Moving the switch down to the R, or reset position, causes gate A to have 1 and 0 inputs and output = 0 and gate B to have 0 inputs and output = 1. Hence, the flip-flop resets.

Notice, that when the switch is between the S and R contacts no change occurs. The flip-flop remains in the same state it was in previously. The flip-flop "remembers" its last logic state. This is the way a memory stores logic state data

There are only two logic states. If the switch should bounce as the contacts close or open, no change, other than the first change, will occur. Hence, no noise is generated. For this reason, this circuit is often employed to *de-bounce* switch contacts.

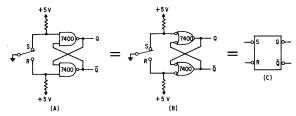

The circuit is commonly referred to as a reset-set flip-flop (R-S flip-flop). Although the circuit is usually constructed with 2-input NAND gates, it is often shown schematically as negated-input OR gates (Fig. 3-2A). This is because, although NAND gates are used, they are functioning as negated-input OR gates. Occasionally, the flip-flop will be shown as a functional logic block (Fig. 3-2C). In this case the bubbles at the R and S inputs indicate that a 0-logic level causes setting and resetting of the flip-flop. Notice that the R and S inputs are never both = 0. This is prohibited since it would cause the Q and  $\bar{\rm Q}$  outputs to = 1.

Fig. 3-2. The R-S flip-flop constructed with NAND gates is often shown functionally (B and C).

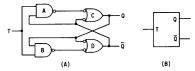

#### THE T FLIP-FLOP AND THE COUNTER

The toggling flip-flop (T-flip-flop) is shown in Fig. 3-3. It consists of a basic R-S flip-flop (gates C and D) and a set of control gates (A and B) which steer a pulse from the T input to the flip-flop to cause it to switch states, i.e., to toggle.

Fig. 3-3. The T flip-flop.

For example, if the flip-flop is reset, a positive pulse (1) at the T input will cause gate A's output to go to 0, setting the flip-flop. If the flip-flop is set, then gate B's output goes to 0 when a 1 occurs at the T input.

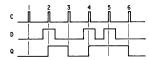

We can observe the action of the circuit with an oscilloscope, when a recurring pulse is fed to the T input. In this case we would observe the waveforms shown in Fig. 3-4. Notice that every time T goes to a 1 the flip-flop